Professional Documents

Culture Documents

R7220404 Switching Theory & Logic Design

Uploaded by

subbuOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

R7220404 Switching Theory & Logic Design

Uploaded by

subbuCopyright:

Available Formats

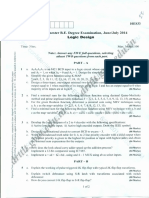

Code: R7220404 R07

B.Tech II Year II Semester (R07) Supplementary Examinations May/June 2015

SWITCHING THEORY & LOGIC DESIGN

(Electronics and Communication Engineering)

Time: 3 hours Max. Marks: 80

Answer any FIVE questions

All questions carry equal marks

*****

1 Construct a 7 - bit single error correcting code to represent the decimal digits by using excess - 3 code

word using even parity checks. Using an example explain the process of error detection and correction.

2 (a) Realize the function F = A(B+CD) + BC using minimum number of NAND gates only.

(b) Simplify the following expression using Boolean theorems:

(A+B+C) (B+C) + (A+D) (A+C).

3 (a) Minimize the following function F(A,B,C,D) = m (0, 1, 2, 3, 5, 7, 8, 9, 11, 14)

(b) Simplify the Boolean expression F = M(0, 1, 3, 5, 6, 7, 10, 14, 15).

4 (a) Design an excess-3 to binary decoder using the unused combinations of the code as dont care

condition.

(b) Draw the logic diagram of a 2 x 4 line decoder using NOR gates only.

5 (a) Draw the internal construction of PLA having three inputs, three product terms and two outputs.

(b) Derive the PLA programming table for the combinational circuit that squares a 3-bit number and also

minimize the number of product terms.

6 (a) Design a modulo-32 ripple counter using JK flip-flops.

(b) Draw the circuit of a decade ripple counter using four flip-flops and explain it working with a table

showing the counting sequences.

7 (a) State the capabilities and limitations of finite state machine.

(b) For a machine given below find the equivalence partition and a corresponding reduces in standard form.

N.S

P.S

X=0 X=1

A D,0 H,1

B F,1 C,1

C D,0 F,1

D C,0 E,1

E C,1 D,1

F D,1 D,1

G D,1 C,1

H B,1 A,1

8 (a) Obtain the ASM chart for the following state transition: if x = 0, control goes from state T1 to T2 ; if x = 1,

generate a conditional output F and go from T1 to T2.

(b) Explain the data path subsystem implementation for weighing machine using ASM chart.

*****

You might also like

- DSD Model Paper 1Document7 pagesDSD Model Paper 1VigneshNo ratings yet

- Rr210203 Switching Theory and Logic DesignDocument9 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao GNo ratings yet

- M.tech Digital System DesignDocument2 pagesM.tech Digital System DesignsrinivasNo ratings yet

- Digital Logic DesignDocument4 pagesDigital Logic DesignShareef KhanNo ratings yet

- 113BU032016Document2 pages113BU032016mushahedNo ratings yet

- Btech Biomed 4 Sem Digital Electronics Circuit Pbm4i102 2018Document3 pagesBtech Biomed 4 Sem Digital Electronics Circuit Pbm4i102 2018Narinder MauryaNo ratings yet

- Rr210203 Switching Theory and Logic DesignDocument8 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao G100% (2)

- S T L DDocument12 pagesS T L DMohan Krishna0% (1)

- Jntuk 2 1 DLD Nov 2017 Q.PDocument5 pagesJntuk 2 1 DLD Nov 2017 Q.PRoopa Krishna ChandraNo ratings yet

- STLD 2009 RegularDocument4 pagesSTLD 2009 RegularrangerNo ratings yet

- 07a4ec09 STLDDocument6 pages07a4ec09 STLDSRINIVASA RAO GANTANo ratings yet

- Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - inDocument2 pagesDrttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - inrama KrishnaNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument23 pages3 Hours / 70 Marks: Seat NoHitesh BadgujarNo ratings yet

- CT 801 / CSE802 - Compiler ConstructionDocument12 pagesCT 801 / CSE802 - Compiler ConstructionSumit PaulNo ratings yet

- DSD Model Paper 2Document8 pagesDSD Model Paper 2VigneshNo ratings yet

- 15A04306 Digital Logic Design4Document2 pages15A04306 Digital Logic Design4Lakshmi PrashanthNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- 21 - 2010 - Nov - R09 - STLDDocument8 pages21 - 2010 - Nov - R09 - STLDvasuvlsiNo ratings yet

- Final Exam Solution - Test Paper Final Exam Solution - Test PaperDocument15 pagesFinal Exam Solution - Test Paper Final Exam Solution - Test Paperciuciu.denis.2023No ratings yet

- Final Exam Solution - Test Paper Final Exam Solution - Test PaperDocument82 pagesFinal Exam Solution - Test Paper Final Exam Solution - Test Paperciuciu.denis.2023No ratings yet

- Rr311901 Digital Systems DesignDocument8 pagesRr311901 Digital Systems DesignSrinivasa Rao GNo ratings yet

- R13 Nov 2016Document2 pagesR13 Nov 2016Anil Kumar BNo ratings yet

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignDocument4 pagesWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaNo ratings yet

- Switching Theory and Logic DesignDocument8 pagesSwitching Theory and Logic DesignSubrahmanyam VjsNo ratings yet

- World: Code: 9A02401Document7 pagesWorld: Code: 9A02401surya pratapNo ratings yet

- Digital and Logic Design Lab-8 Revision LabDocument4 pagesDigital and Logic Design Lab-8 Revision Labprince12No ratings yet

- Previous Year Paper Digital Logic DesignDocument1 pagePrevious Year Paper Digital Logic DesignShivanshu Kumar UpadhyayNo ratings yet

- Fundamentals of Digital System DesignDocument2 pagesFundamentals of Digital System DesignsubramanianNo ratings yet

- WWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Document2 pagesWWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Anil Kumar BNo ratings yet

- Switching Theory and Logic DesignDocument6 pagesSwitching Theory and Logic DesignVijay MNo ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- 2019 Summer Question Paper (Msbte Study Resources)Document4 pages2019 Summer Question Paper (Msbte Study Resources)Parth patkarNo ratings yet

- De As1Document2 pagesDe As1Dr-Tarun ParasharNo ratings yet

- Logic CircuitsDocument2 pagesLogic CircuitsRaman yadavNo ratings yet

- 21 - 2011 - Dec - R09 - STLDDocument8 pages21 - 2011 - Dec - R09 - STLDvasuvlsiNo ratings yet

- CS2100 Finals 2021s2 QuestionsDocument11 pagesCS2100 Finals 2021s2 Questionsjoechua247No ratings yet

- Comp SC 18Document8 pagesComp SC 18Masiur RahamanNo ratings yet

- Answer Two Questions, Question No. 3 Is CompulsoryDocument3 pagesAnswer Two Questions, Question No. 3 Is CompulsoryABHILESH G KNo ratings yet

- University Question Paper - 2016-2018Document27 pagesUniversity Question Paper - 2016-2018Aditya SrivastavaNo ratings yet

- Cse 205Document39 pagesCse 205sharminmin92No ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- MIT6 004s09 Tutor04 SolDocument14 pagesMIT6 004s09 Tutor04 SolAbhijith RanguduNo ratings yet

- DSD Previous PapersDocument8 pagesDSD Previous Paperssunilreddy2winNo ratings yet

- ICT 9A04306 Digital Logic DesignDocument1 pageICT 9A04306 Digital Logic DesignMahaboob SubahanNo ratings yet

- CMP 334 Fall 2020 MidtermDocument4 pagesCMP 334 Fall 2020 MidtermOunteni hyacinthe firmin OboulbigaNo ratings yet

- 08ab303 - Digital Logic CircuitsDocument3 pages08ab303 - Digital Logic CircuitsChandru RamaswamyNo ratings yet

- Logic Circuits 2012 FallDocument2 pagesLogic Circuits 2012 FallSimant ChaudharyNo ratings yet

- CBCS - BA-BSC - HONS - Sem-1 - COMPUTER SCIENCE - CC-1 - DIGITAL LOGIC-3626 2021Document2 pagesCBCS - BA-BSC - HONS - Sem-1 - COMPUTER SCIENCE - CC-1 - DIGITAL LOGIC-3626 2021Bhaswar ChakrabortyNo ratings yet

- 9A04306 Digital Logic DesignDocument2 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- Kec 302 Digital System DesignDocument2 pagesKec 302 Digital System DesignAditya KasaudhanNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- Logic Design June 2010 ESDocument2 pagesLogic Design June 2010 ESPrasad C MNo ratings yet

- AP Computer Science Principles: Student-Crafted Practice Tests For ExcellenceFrom EverandAP Computer Science Principles: Student-Crafted Practice Tests For ExcellenceNo ratings yet

- Topographical Tools for Filtering and Segmentation 2: Flooding and Marker-based Segmentation on Node- or Edge-weighted GraphsFrom EverandTopographical Tools for Filtering and Segmentation 2: Flooding and Marker-based Segmentation on Node- or Edge-weighted GraphsNo ratings yet

- Attainable Region Theory: An Introduction to Choosing an Optimal ReactorFrom EverandAttainable Region Theory: An Introduction to Choosing an Optimal ReactorNo ratings yet

- BT BP AcDocument1 pageBT BP AcsubbuNo ratings yet

- 12D86101 Advanced Computing MethodsDocument1 page12D86101 Advanced Computing MethodssubbuNo ratings yet

- 12D86102 Microelectronic Technology & IC FabricationDocument1 page12D86102 Microelectronic Technology & IC FabricationsubbuNo ratings yet

- 12D86103 Materials For NanotechnologyDocument1 page12D86103 Materials For NanotechnologysubbuNo ratings yet

- 12D75104b Advanced Instrumentation SystemsDocument1 page12D75104b Advanced Instrumentation SystemssubbuNo ratings yet

- Jntuworld: (Common To Vlsies, Esvlsi & Vlsiesd)Document1 pageJntuworld: (Common To Vlsies, Esvlsi & Vlsiesd)subbuNo ratings yet

- 12d20106a Prestressed ConcreteDocument1 page12d20106a Prestressed ConcretesubbuNo ratings yet

- 12D20105c Low Cost Housing TechniquesDocument1 page12D20105c Low Cost Housing TechniquessubbuNo ratings yet

- 12D20102 Advanced Structural AnalysisDocument2 pages12D20102 Advanced Structural AnalysissubbuNo ratings yet

- 9D57102 Analog IC DesignDocument1 page9D57102 Analog IC DesignsubbuNo ratings yet

- 12d20105a Experimental Stress AnalysisDocument1 page12d20105a Experimental Stress AnalysissubbuNo ratings yet

- 9d58106a Advances in DatabasesDocument1 page9d58106a Advances in DatabasessubbuNo ratings yet

- 9D61103 Computer Communication NetworksDocument1 page9D61103 Computer Communication NetworkssubbuNo ratings yet

- 9D58203 Advanced Computer NetworksDocument1 page9D58203 Advanced Computer NetworkssubbuNo ratings yet

- 9D57105 Hardware Software Co-DesignDocument1 page9D57105 Hardware Software Co-DesignsubbuNo ratings yet

- 9D57106c ASIC DesignDocument1 page9D57106c ASIC DesignsubbuNo ratings yet

- Robosapien Hacking2Document3 pagesRobosapien Hacking2GEORGE KARYDISNo ratings yet

- Opentext Documentum Content Services For Sap: Configuration GuideDocument66 pagesOpentext Documentum Content Services For Sap: Configuration GuidespacnavNo ratings yet

- Network Security: Trish MillerDocument58 pagesNetwork Security: Trish MillerXozanNo ratings yet

- Quick Start ECos On Zynq ZC702 Evaluation BoardDocument21 pagesQuick Start ECos On Zynq ZC702 Evaluation BoardTimoMarxNo ratings yet

- Avijit PAL: ExperienceDocument1 pageAvijit PAL: ExperienceAvijit PalNo ratings yet

- MK Comparison Meraki - Vs - Cisco PDFDocument5 pagesMK Comparison Meraki - Vs - Cisco PDFMaría Rita Sánchez ChiuyariNo ratings yet

- AnywayDocument116 pagesAnywayAnonymous nzfEotriWKNo ratings yet

- 06 Final Copa Lesson PlanDocument91 pages06 Final Copa Lesson Planलक्ष्मण कुमार द्विवेदीNo ratings yet

- Y96k DatasheetDocument2 pagesY96k DatasheetAndrea NovellaNo ratings yet

- Atmel Microcontroller ISP Software User's ManualDocument20 pagesAtmel Microcontroller ISP Software User's Manualyusuf amarudinNo ratings yet

- 522 Week2 TutorialDocument2 pages522 Week2 TutorialEdwin SalvadorNo ratings yet

- Veritas Netbackup ™ Enterprise Server and Server 8.2 - 8.X.X Hardware and Cloud Storage Compatibility List (HCL)Document325 pagesVeritas Netbackup ™ Enterprise Server and Server 8.2 - 8.X.X Hardware and Cloud Storage Compatibility List (HCL)AviNo ratings yet

- ADC0802 ADC0803 ADC0804 (Harris)Document16 pagesADC0802 ADC0803 ADC0804 (Harris)Amit PujarNo ratings yet

- Sampling Rate and Aliasing On A Virtual LaboratoryDocument5 pagesSampling Rate and Aliasing On A Virtual LaboratoryJaweria AmjadNo ratings yet

- Basic Control Hijacking AttacksDocument35 pagesBasic Control Hijacking AttacksHaider AliNo ratings yet

- Asterik SolutionDocument5 pagesAsterik SolutionEko TriyantoNo ratings yet

- ALPHA A1800 ModbusDocument98 pagesALPHA A1800 ModbusIlaiyaa RajaNo ratings yet

- WIDI Recognition SystemDocument6 pagesWIDI Recognition SystemRadomir NesicNo ratings yet

- Flashwave Packet Optical Networking Platform PDFDocument10 pagesFlashwave Packet Optical Networking Platform PDFMarcel KebreNo ratings yet

- Multiplexing LED Drive and A 4x4 Keypad SamplingDocument25 pagesMultiplexing LED Drive and A 4x4 Keypad SamplingKathleen GonzagaNo ratings yet

- ES Syllabus ECE PDFDocument12 pagesES Syllabus ECE PDFramanaidu1No ratings yet

- Title Proposal PresentationDocument5 pagesTitle Proposal PresentationSharmaine RoqueNo ratings yet

- Step-By-Step Guide On Deploying Revenue Sharing Blockchain Smart Contracts Using Remix-IDE On WindowsDocument27 pagesStep-By-Step Guide On Deploying Revenue Sharing Blockchain Smart Contracts Using Remix-IDE On WindowsKefa RabahNo ratings yet

- 1448504978725ADSL Modem - Igate AW300N PDFDocument9 pages1448504978725ADSL Modem - Igate AW300N PDFĐỗ DuyNo ratings yet

- FND LoadDocument39 pagesFND LoadVenkatesh VykuntamNo ratings yet

- CBC Computer Systems Servicing NCII 05 PDFDocument2 pagesCBC Computer Systems Servicing NCII 05 PDFOliver CalledoNo ratings yet

- Oracle Database 12c Security D81599GC10 1080544 USDocument5 pagesOracle Database 12c Security D81599GC10 1080544 USJinendraabhiNo ratings yet

- Data Warehouse ConceptDocument18 pagesData Warehouse Conceptvenkateswarlu v100% (1)

- Configuring Terminal Services Core FunctionalityDocument20 pagesConfiguring Terminal Services Core FunctionalityNelsonbohrNo ratings yet

- Gta 4 Cody SerialDocument2 pagesGta 4 Cody SerialVinicius Sipher37% (27)