Professional Documents

Culture Documents

Bcse Paper

Uploaded by

Anonymous eWMnRr70qCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bcse Paper

Uploaded by

Anonymous eWMnRr70qCopyright:

Available Formats

[Ragavi*, Vol.5(Iss.

4): April, 2016] ISSN: 2277-9655

(I2OR), Publication Impact Factor: 3.785

IJESRT

INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH

TECHNOLOGY

IMPLEMENTATION OF VLSI ARCHITECTURE FOR RECONFIGURABLE RRC FIR

FILTER USING GRAPH BASED METHOD

M.Ragavi *, D.K.Monisa , S.Dhivya

Department of Electronics and communication Engineering,

*

Dhirajlal Gandhi College of Technology, Salem,TN,India

Mahendra Engineering College,Namakkal,TN,India

DOI: 10.5281/zenodo.49815

ABSTRACT

The essential factors which contributes for designing the architecture of reconfigurable pulse shaping FIR filter are

low complexity and power consumption. Although several low complexity architectures have been used for the

optimization of Multiple Constant Multiplication (MCM), ie., the multiplication of a data sample by set of

constants, further improvement in area and power consumption for RRC FIR filter design can be accomplished by

employing the highly efficient algorithms. Hence the Graph Based (GB) algorithm had been implemented in RRC

FIR filter. These GB methods are not limited to any particular number representation such as CSD, MSD, Binary

and it yields better solutions than shift add implementation of constant multiplication. It is also capable of operating

for different wordlength filter coefficients without any expense over the hardware circuitry. Hence it has been

observed from the experimental result that the architecture using GB algorithm offers efficient area reduction and

power consumption when compared to existing reconfigurable implementations using BCSE algorithm.

KEYWORDS: Multiple Constant Multiplication (MCM), Root Raised Cosine (RRC), Binary Common

Subexpression Elimination (BCSE), Graph Based (GB) Algorithm

INTRODUCTION

FIR filter plays a vital role in the emerging wireless communication and DSP applications. The reduced bandwidth

is required for this application. On the other side when rectangular pulses are passed through the band limited

channel, the pulses spread with respect to time. So the pulses of each symbol will smear with succeeding symbols to

form Inter Symbol Interference. To overcome ISI, larger channel bandwidth is required. Tackling these two

contrary requirements at the same time leads to the development of RRC filters.

The most crucial part in the architecture of RRC FIR filter is shift and add unit.Hence, the multiplications of filter

coefficient with the input data are generally implemented under shift and add architecture for its reduction in

hardware. This normal shift and add implementation leads to the inclusion of maximum number of operations in the

gate level design of the filter. To overcome that distinctive methods are there to implement the constant

multiplication.

A straight way of implementing the shift and add architecture [1] involves the constant be first converted into

binary. For each binary representation, the occurrence of shifts is done according to that particular bit position. This

method is called digit based recoding. Depending on the number of non-zero digits present, the number of adders

will be required for the product. So this method is useful for optimization of constant multiplication, but it is not

optimal. Sign digit representations (SD) [2] are employed to optimize the multiple constant multiplication problems.

One of the SD method is Canonic sign digit representation [3] which increases the number of zeros and inhibits the

possibility of having two adjacent non zero digits. But, this representation does not contribute to give the minimum

number of operations in MCM. Because, it uses single representation of a constant with minimum number of non-

http: // www.ijesrt.com International Journal of Engineering Sciences & Research Technology

[673]

[Ragavi*, Vol.5(Iss.4): April, 2016] ISSN: 2277-9655

(I2OR), Publication Impact Factor: 3.785

zero digits and both positive, negative signs in the CSD representation may produce partial terms which are less

common in the implementation of constants.

Other algorithms for the optimizing the number of operations in MCM can be categorized into two classes namely

common subexpression elimination techniques and graph based techniques. Common Subexpression elimination

(CSE) [4] algorithm is to finding the most common digit patterns in the set of constants multiplying a variable. CSD

based CSE algorithm (CSD-CSE) [5] is used to identify the multiple occurrences of bit patterns that occur within the

CSD representation of coefficients and eliminate the redundant multiplication. CommonSubexpression Elimination

algorithm depends on number representation such as Binary. It is then named as Binary Common Subexpression

Elimination algorithm (BCSE). In BCSE [6], redundant binary common subexpressions are eliminated by reusing

the Binary Common Subexpressions that occur within the coefficients. The BCSE technique provides improved

adder reductions and low complexity FIR filters when compared to CSD-CSE methods. The objective function for

most of the MCM algorithm is to minimize the adder cost. The Graph Based Algorithm is proposed where the

representation is not dependent. It produces the solution with minimum number of operations while compared to

other techniques.

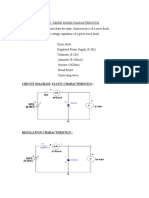

ARCHITECHTURE OF ROOT RAISED COSINE FIR FILTER (RRC FIR)

The RRC FIR filter architecture [8] plays a vital role in three communication standards namely universal mobile

telecommunication, wideband code division multiple access and digital video broadcasting for its ability to reduce

the bit error rate by not allowing the timing jitter at the sampling instant.

CS1

CS2

DATA

GENERATOR CS3

FINAL

CS4 RRCOUT

ACCUMULATION

UNIT

CS5

COEFFICIENT

GENERATOR

CS6

CS7

COEFFICIENT

SELECTOR

Fig.1 Architecture of RRC FIR filter

A. Data generator block (GB)

The interpolation factor for the universal mobile telecommunication standard be 4 for 25 tap filter, 8 for 49 tap

filter, 16 for 97 tap filter. Depending upon the interpolation factor, the data generator block samples the input data

sequence RRCIN and generates subfilter required for the different tap filters such as 25,49,97. For example, if 25

tap filter is used then the sub filters required for their implemenation be 25/4 ie., seven subfilters .

B. Coefficient generator block (CG)

The coefficient generator block performs the multiplication operation between the inputs and filter coefficients. The

two stage optimisation technique is used in this CG block for simplifying the RRC FIR filter with lowest

computation time and with low complexity. The flow diagram of the CG Block is shown in Fig.2 and its

functionality is described as follows.

http: // www.ijesrt.com International Journal of Engineering Sciences & Research Technology

[674]

[Ragavi*, Vol.5(Iss.4): April, 2016] ISSN: 2277-9655

(I2OR), Publication Impact Factor: 3.785

i) First Coding Pass (FCP)

For N tap filter with interpolation factor L requires (N/L) number of convolution operations and also it needs the

number of structural adders for the addition operation. If M, N, O tap filter with interpolation factor L, P, Q requires

large number of convolution operations and more structural adders for their implementation. Henceforth for a

constant propagation delay, the area and power consumption increases with rise in number of multipliers and

structural adders. For this, the optimization is done by First coding Pass (FCP) block. In this FCP, filters varying

only by the filter parameters are passed through the 2:1 multiplexer where the control parameter called rolloff factor

selects the desired filter.

ii) Second Coding Pass (SCP)

The selected filter coefficients from the First Coding Pass block are passed through the second coding pass block.

Depending on the interpolation factor, filter coefficients are coded accordingly.

iii) Shift and Add Unit

Then the multiplication operation performs between the input data and filter coefficients selected from Second

Coding Pass (SCP). For Partial product generation Binary Common Subexpression Elimination Technique (BCSE)

is used for eliminating the most common subexpressions within the coefficients

iv) Multiplexer Unit

The multiplexer unit selects the output generated from the shift and add block depending upon the coded

coefficients.

v) Addition Unit

The addition operation can be performed by summing all the outputs of partial product generator followed by eight

multiplexer units.

FIRST CODING PASS

SECOND CODING PASS

SHIFT AND ADD UNIT

MULTIPLEXER UNIT

ADDITION UNIT

Fig.2 Coefficient Generator

C. Coefficient selector block

The proper data from the coefficient generator block is steered to final accumulation unit according to the

interpolation factor parameter.

D. Final data accumulation unit

The reconfigurable pulse shaping FIR filter is based on transposed direct form architecture.

BINARY COMMON SUBEXPRESSION ELIMINATION (BCSE) ALGORITHM

BCSE [7] deals with the elimination of redundant Binary Common Subexpressions (BCSs) that occur within the

coefficients. The BCSE technique targets on eliminating redundant computations in coefficient multipliers by

reusing the most common binary bit patterns (BCSs) present in coefficients. An n-bit binary number can form 2n

(n + 1) BCSs among themselves. For example, a 2-bit binary representation can form only one BCS, which is 11.

These BCSs can be expressed as [1 1] = x1 = x+ 21x where x is the input signal. The other representation such as

00, 01 and 10 does not require adder for the implementation as they have zero and only one non zero bit is available.

The straightforward implementation of the above BCS requires only one adder.The number of adders required for all

the possible n-bit binary subexpressions is 2n1 1. For n=3, the number of adders required are three. For n=2, the

http: // www.ijesrt.com International Journal of Engineering Sciences & Research Technology

[675]

[Ragavi*, Vol.5(Iss.4): April, 2016] ISSN: 2277-9655

(I2OR), Publication Impact Factor: 3.785

number of adders needed are one. The number of adders needed for the implementation of coefficient multipliers

using BCSE [7] is considerably less than the CSD-based CSE methods.

GRAPH BASED ALGORITHM

The proposed technique implemented in the architecture of RRC FIR is graph based algorithm. These algorithms

are not restricted to any particular number representation and it will synthesize the constants by building a graph.

This graph based algorithm consists of two parts. They are optimal part and heuristic part. In optimal part, the target

constant can be implemented in single operation, whose inputs are in the ready set.

In another part called heuristic, if there exists unimplemented elements in the target set whose inputs are not in the

ready set, then the algorithm moves to this part where an intermediate constant is added to the ready set for reaching

the target set value. Hence this exact algorithm finds the minimum number of intermediate constants and finds the

minimum number of operations solution for the implementation of architecture.

A. Implementation of GB Algorithm

In the proposed graph based algorithm, there will be ready set and target set. Initially ready set always be 1, the

target coefficient values are to be fixed. The target set elements must be made odd and positive integer. To reach the

target set coefficients from ready set, the intermediate constants must be needed. The intermediate constant must

also be odd and positive integer. The generation of intermediate constant depends upon the bit-width of the filter.

For example, if bit-width=3, then the intermediate constant range is from 1 to 15 which is based on j=1 to 2 bw+1-1.

According to this algorithm, after the synthesis of optimal part if there exist unimplemented constants in the target

set then the synthesis of heuristic part will gets started using the intermediate constant. The processing of each

intermediate constant with the target set iteratively selects the best intermediate constant. By using this intermediate

constant, the partial products of target constants are shared and the number of operations for shift and add unit will

be gets reduced. For example if target set T = {39, 53, 7, 11, 9, 13} then the shift and add implementation using

graph based algorithm is shown in Fig.3. The figure describes one sub tractor and five adders are required for the

implementation of target set with six filter coefficients

- +

+

+

+ +

Fig3. Implementation of target constants using GB algorithm

Henceforth this GB algorithm has been adopted in the above coefficient generator block as described in Fig.2 for its

optimization in area and power. Then the carry save adder is used in the addition unit of coefficient generator block

for increase in the gate level speed of constant multiplication in RRC FIR filter.

http: // www.ijesrt.com International Journal of Engineering Sciences & Research Technology

[676]

[Ragavi*, Vol.5(Iss.4): April, 2016] ISSN: 2277-9655

(I2OR), Publication Impact Factor: 3.785

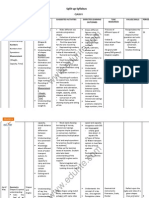

RESULTS AND DISCUSSION

Simulation has been done in Xilinx ISE design 14.2 for synthesizing purposes. Then the synthesized filter design is

implemented in Xilinxs SPARTRAN 3E FPGA. The results depicted in Fig.4 describes that the architecture of

RRC FIR filter using BCSE algorithm has 68.4% improvement in the LUT consumption and 39% improvement in

the speed. From Fig.5, it has been proven that the proposed architecture using GB algorithm provides 28% more

gate consumption and also be noticed that the speed be improved by 58.3% than the previously used BCSE

algorithm. Fig.6 describes the comparison of power in terms of mw and Fig.7 shows that the speed of implementing

the architecture using GB is faster when compared to BCSE algorithm.

Fig.4Simulation result of BCSE algorithm for optimization of MCM design

Fig.5 Simulation result of RRC FIR filter architecture using graph based algorithm

http: // www.ijesrt.com International Journal of Engineering Sciences & Research Technology

[677]

[Ragavi*, Vol.5(Iss.4): April, 2016] ISSN: 2277-9655

(I2OR), Publication Impact Factor: 3.785

6 6

4 4

2 power (mw) 2 speed (ms)

0 0

GB

GB

BCSE

BCSE

Fig.6 Comparison of power in terms of mw Fig.7 Comparison of speed in terms of ms

CONCLUSION

The observations of experimental result states that the design of MCM operation in the shift and add architecture

with the use of Graph Based algorithm achieves significant area reduction and power consumption with respect to

filter design where the multiplier part is implemented by using BCSE algorithm. The implementation of RRC FIR

filter design in FPGA demonstrates the merits of proposed architecture in terms of area and power. Also it is

recommended that the proposed design will be remarkably suited for next generation multistandard communication

systems.

REFERENCES

[1] M. Ercegovac and T. Lang. Digital Arithmetic. Morgan Kaufmann, 2003.

[2] K.-H. Chen and T.-D. Chieueh, A low-power digit-based reconfigurable FIR filter, IEEE Trans. Circuits

Syst. II, Exp. Briefs, vol. 53, no. 8, pp. 617621, Aug. 2006.

[3] K.-H. Chen and T.-D. Chieueh, A low-power digit-based reconfigurable FIR filter, IEEE Trans. Circuits

Syst. II, Exp. Briefs, vol. 53, no. 8, pp. 617621, Aug. 2006.

[4] Yuen H.A.H., Chi U.L., Hing-K.K.,Ngai Wong, Global optimization of common subexpressions for

multiplierless synthesis of multiple constant multiplications IEEE Explore,pp.119-124, 2008.

[5] Y. J. Yu and Y. C. Lim, Optimization of linear phase FIR filters in dynamically expanding subexpressio ns

space, Circuits, Syst., Signal Process., vol. 29. no. 1, pp. 6580, 2010

[6] R. Mahesh and A. P. Vinod, A new common subexpression elimination algorithm for realizing low-

complexity higher order digital filters, IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 27,

no. 2, pp. 217229, Feb. 2008.

[7] R. Mahesh and A. P. Vinod, New reconfigurable architectures for implementing FIR filters with low

complexity, IEEE Trans.Comput.-Aided Design Integr. Circuits Syst., vol. 29, no. 2, pp. 275288, Feb.

2010.

[8] Indragith Hatai, Indragith chakrabharti and swapna Banerjee, An Efficient VLSI Architecture of a

Reconfigurable Pulse Shaping FIR Interpolation Filter for Multistandard DUC, IEEE Transactions on

VERY LARGE SCALE INTEGRATED (VLSI) SYSTEMS, APRIL 2014

http: // www.ijesrt.com International Journal of Engineering Sciences & Research Technology

[678]

You might also like

- Architecture-Aware Optimization Strategies in Real-time Image ProcessingFrom EverandArchitecture-Aware Optimization Strategies in Real-time Image ProcessingNo ratings yet

- Using Artificial Neural Networks for Analog Integrated Circuit Design AutomationFrom EverandUsing Artificial Neural Networks for Analog Integrated Circuit Design AutomationNo ratings yet

- Design and Implementation of Modified Booth Recoder Using Fused Add Multiply OperatorDocument5 pagesDesign and Implementation of Modified Booth Recoder Using Fused Add Multiply OperatorIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalNo ratings yet

- FIR FilterDocument5 pagesFIR FilterManasa UpadhyayaNo ratings yet

- A Triangular Common Subexpression Elimination Algorithm With Reduced Logic Operators in FIR FilterDocument5 pagesA Triangular Common Subexpression Elimination Algorithm With Reduced Logic Operators in FIR FilterPANKAJ GUPTANo ratings yet

- A Modified CSD Conversion For Constant Multiplication Architecture For Air Filter - IRJASHDocument5 pagesA Modified CSD Conversion For Constant Multiplication Architecture For Air Filter - IRJASHIRJASHNo ratings yet

- High Speed and Area Efficient Fpga Implementation of Fir Filter Using Distributed ArithmeticDocument7 pagesHigh Speed and Area Efficient Fpga Implementation of Fir Filter Using Distributed ArithmeticZulfiqar AliNo ratings yet

- International Journal of Computational Engineering Research (IJCER)Document9 pagesInternational Journal of Computational Engineering Research (IJCER)International Journal of computational Engineering research (IJCER)No ratings yet

- Vertical-Horizontal Binary Common Sub-Expression Elimination For Reconfigurable Transposed Form FIR FilterDocument6 pagesVertical-Horizontal Binary Common Sub-Expression Elimination For Reconfigurable Transposed Form FIR FilterIJRASETPublicationsNo ratings yet

- Design of Roba Multiplier Using Mac UnitDocument15 pagesDesign of Roba Multiplier Using Mac UnitindiraNo ratings yet

- Analysis of Different Bit Carry Look Ahead Adder Using Verilog Code-2Document7 pagesAnalysis of Different Bit Carry Look Ahead Adder Using Verilog Code-2IAEME PublicationNo ratings yet

- A Power Efficient Multiplier Architecture For Fir Filters Used For Acoustic Models in Mechanical DiagnosticsDocument8 pagesA Power Efficient Multiplier Architecture For Fir Filters Used For Acoustic Models in Mechanical DiagnosticsTJPRC PublicationsNo ratings yet

- (IJCST-V9I2P10) :DR - Shine N DasDocument6 pages(IJCST-V9I2P10) :DR - Shine N DasEighthSenseGroupNo ratings yet

- Reduction of power supply noise with digital filtersDocument9 pagesReduction of power supply noise with digital filtersडाँ सूर्यदेव चौधरीNo ratings yet

- FPGA Implementation of High Speed FIR Filters Using Add and Shift MethodDocument6 pagesFPGA Implementation of High Speed FIR Filters Using Add and Shift Methodpramani90No ratings yet

- Design of Area-Power Efficient Parallel Fir Filter With Mux Based Full AdderDocument8 pagesDesign of Area-Power Efficient Parallel Fir Filter With Mux Based Full AdderIJRASETPublicationsNo ratings yet

- Scalable Elliptic Curve Cryptosystem FPGA Processor For NIST Prime CurvesDocument4 pagesScalable Elliptic Curve Cryptosystem FPGA Processor For NIST Prime CurvesjanepriceNo ratings yet

- Design of Multiplierless IFIR Based Cosine Modulated Filter Bank Using QPSODocument6 pagesDesign of Multiplierless IFIR Based Cosine Modulated Filter Bank Using QPSOAnant Bhushan NagabhushanaNo ratings yet

- Efficient Design of FIR Filter Using Modified Booth MultiplierDocument5 pagesEfficient Design of FIR Filter Using Modified Booth MultiplierijsretNo ratings yet

- Critical Path Reduction of Distributed Arithmetic Based FIR FilterDocument8 pagesCritical Path Reduction of Distributed Arithmetic Based FIR Filterksreddy2002No ratings yet

- Performance Analysis of Reconfigurable Multiplier Unit For FIR Filter DesignDocument8 pagesPerformance Analysis of Reconfigurable Multiplier Unit For FIR Filter DesignInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- 13 - Chapter 4 - 2Document24 pages13 - Chapter 4 - 2ksreddy2002No ratings yet

- Fpga Implementation of Fir Filter in Signal Processing: AbstractDocument4 pagesFpga Implementation of Fir Filter in Signal Processing: AbstractShafiullaShaikNo ratings yet

- Design and Implementation of Viterbi Decoder Using VHDL: IOP Conference Series: Materials Science and EngineeringDocument7 pagesDesign and Implementation of Viterbi Decoder Using VHDL: IOP Conference Series: Materials Science and Engineeringkrishna mohan pandeyNo ratings yet

- International Journal of Engineering Research and Development (IJERD)Document8 pagesInternational Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- New low-complexity reconfigurable architectures for FIR filtersDocument14 pagesNew low-complexity reconfigurable architectures for FIR filtersSyfunnisa ShaikNo ratings yet

- FIR Filter Design On Chip Using VHDL: IPASJ International Journal of Computer Science (IIJCS)Document5 pagesFIR Filter Design On Chip Using VHDL: IPASJ International Journal of Computer Science (IIJCS)International Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- IJEDR1703147Document8 pagesIJEDR1703147Naga NitheshNo ratings yet

- A12Document6 pagesA12Usha MaddipatiNo ratings yet

- High-Speed Area-Efficient VLSI Architecture of Three-Operand Binary AdderDocument6 pagesHigh-Speed Area-Efficient VLSI Architecture of Three-Operand Binary Adderk NiroshaNo ratings yet

- 2019 TCASI AreaTimePower Efficient FFT Architectures Based On Binary-Signed-Digit CORDICDocument8 pages2019 TCASI AreaTimePower Efficient FFT Architectures Based On Binary-Signed-Digit CORDICTsukasa BerryNo ratings yet

- Bit Error Optimization of Coded Ofdm System Over RDocument10 pagesBit Error Optimization of Coded Ofdm System Over RzelalemaschaleyNo ratings yet

- 1 s2.0 S0026269219309346 MainDocument9 pages1 s2.0 S0026269219309346 MainShylu SamNo ratings yet

- An Enhancement of Decimation Process Using Fast Cascaded Integrator Comb (CIC) FilterDocument5 pagesAn Enhancement of Decimation Process Using Fast Cascaded Integrator Comb (CIC) FilterDr. Rozita teymourzadeh, CEng.100% (1)

- FPGA Implementation of FIR Filters Using Pipelined Bit-Serial CSD MultipliersDocument34 pagesFPGA Implementation of FIR Filters Using Pipelined Bit-Serial CSD MultipliersSARATH MOHANDASNo ratings yet

- 1997 TCASII I. Galton Spectral Shaping of Circuit Errors in Digital To Analog ConvertersDocument10 pages1997 TCASII I. Galton Spectral Shaping of Circuit Errors in Digital To Analog Converterskijiji userNo ratings yet

- Efficient Design Using Fpgas: of Application Specific CoresDocument5 pagesEfficient Design Using Fpgas: of Application Specific CoresK.GurucharanNo ratings yet

- VHDL Generation of Optimized FIR FiltersDocument5 pagesVHDL Generation of Optimized FIR FiltersMauhik ThakkarNo ratings yet

- 5.an Optimized Modified Booth Recorder For Efficient Design of The Add-Multiply Operator.Document11 pages5.an Optimized Modified Booth Recorder For Efficient Design of The Add-Multiply Operator.gestNo ratings yet

- Design and Implementation of High Speed Carry Select AdderDocument6 pagesDesign and Implementation of High Speed Carry Select AdderseventhsensegroupNo ratings yet

- The Design of A Low Power Asynchronous Multiplier: Yijun Liu, Steve FurberDocument6 pagesThe Design of A Low Power Asynchronous Multiplier: Yijun Liu, Steve FurberMishi AggNo ratings yet

- Review On Word Length Optimization: Pandi G Sabareeswari, Bhuvaneswari S DR Manivannan SDocument4 pagesReview On Word Length Optimization: Pandi G Sabareeswari, Bhuvaneswari S DR Manivannan Sbhuvana_eeeNo ratings yet

- A1101010108Document8 pagesA1101010108sudip mandalNo ratings yet

- TSP CMC 27974 Yamini SCIDocument16 pagesTSP CMC 27974 Yamini SCIRooban SNo ratings yet

- Iterative Receivers Combining MIMO DetectionDocument19 pagesIterative Receivers Combining MIMO Detectionrida4No ratings yet

- 39 EfficientDocument7 pages39 EfficientHarryNo ratings yet

- Roba Multiplier: A Rounding-Based Approximate Multiplier For High-Speed Yet Energy-Efficient Digital Signal ProcessingDocument9 pagesRoba Multiplier: A Rounding-Based Approximate Multiplier For High-Speed Yet Energy-Efficient Digital Signal ProcessingRatnakarVarunNo ratings yet

- Signal Processing: Image Communication: B. Krill, A. Ahmad, A. Amira, H. RabahDocument11 pagesSignal Processing: Image Communication: B. Krill, A. Ahmad, A. Amira, H. RabahŢoca CosminNo ratings yet

- Trade-Offs in Multiplier Block Algorithms For Low Power Digit-Serial FIR FiltersDocument6 pagesTrade-Offs in Multiplier Block Algorithms For Low Power Digit-Serial FIR FiltersPankaj JoshiNo ratings yet

- Performance Analysis For Multipliers Based Correlator: Trupti Menghare, Sudesh GuptaDocument5 pagesPerformance Analysis For Multipliers Based Correlator: Trupti Menghare, Sudesh Guptapramod_scribdNo ratings yet

- An Efficient FIR Filter Based On Hardware Sharing Architecture Using CSD Coefficient Grouping For Wireless ApplicationDocument16 pagesAn Efficient FIR Filter Based On Hardware Sharing Architecture Using CSD Coefficient Grouping For Wireless Applicationshikhar bajpaiNo ratings yet

- FIR6Document10 pagesFIR6kishorechiyaNo ratings yet

- Verilogimplementationof Turbo EncoderDocument7 pagesVerilogimplementationof Turbo EncodersaravanaNo ratings yet

- 1 s2.0 S0141933121004920 MainDocument10 pages1 s2.0 S0141933121004920 MainShylu SamNo ratings yet

- Adjustable Window Based Design of Multiplier-Less Cosine Modulated Filter Bank Using Swarm Optimization AlgorithmsDocument10 pagesAdjustable Window Based Design of Multiplier-Less Cosine Modulated Filter Bank Using Swarm Optimization AlgorithmsAman KumarNo ratings yet

- ASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA DownlinkDocument5 pagesASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA DownlinkMunish JassiNo ratings yet

- Roba MulDocument56 pagesRoba MulNishitha NishiNo ratings yet

- Design and Implementation of Energy-Efficient Floating Point MFCC Extraction Architecture For Speech Recognition SystemsDocument11 pagesDesign and Implementation of Energy-Efficient Floating Point MFCC Extraction Architecture For Speech Recognition SystemsIJRASETPublicationsNo ratings yet

- High-Performance DSP Capability Within An Optimized Low-Cost Fpga ArchitectureDocument12 pagesHigh-Performance DSP Capability Within An Optimized Low-Cost Fpga ArchitectureYogesh YadavNo ratings yet

- (Apurba Das (Auth.) ) Digital Communication PrinciDocument25 pages(Apurba Das (Auth.) ) Digital Communication Princiksreddy2002No ratings yet

- Lec 09 111Document246 pagesLec 09 111Anonymous eWMnRr70qNo ratings yet

- NetworksDocument127 pagesNetworksskchiluka100% (2)

- RehuyDocument32 pagesRehuyAnonymous eWMnRr70qNo ratings yet

- Update3 160317004923Document19 pagesUpdate3 160317004923Anonymous eWMnRr70qNo ratings yet

- Advantages of Class B Push Pull Amplifier Over Class ADocument4 pagesAdvantages of Class B Push Pull Amplifier Over Class AAnonymous eWMnRr70qNo ratings yet

- 3aquine Mccluskeymethod 191016140548Document33 pages3aquine Mccluskeymethod 191016140548Anonymous eWMnRr70qNo ratings yet

- 111111111111Document24 pages111111111111Anonymous eWMnRr70qNo ratings yet

- 00numbersystems 130119065930 Phpapp01Document62 pages00numbersystems 130119065930 Phpapp01Anonymous eWMnRr70qNo ratings yet

- Number Systems Explained in 40 CharactersDocument25 pagesNumber Systems Explained in 40 CharactersAnonymous eWMnRr70q100% (1)

- Chapter 3 Special Section: Focus On Karnaugh MapsDocument30 pagesChapter 3 Special Section: Focus On Karnaugh MapsRaja GopalNo ratings yet

- Boolean AlgebraDocument22 pagesBoolean AlgebraAasthaNo ratings yet

- Fed Short QuestionsDocument2 pagesFed Short QuestionsAnonymous eWMnRr70qNo ratings yet

- 3ADocument77 pages3AGurkaranjot SinghNo ratings yet

- BoolDocument33 pagesBoolAnonymous eWMnRr70qNo ratings yet

- Vlsi Technology Kec 053 1Document2 pagesVlsi Technology Kec 053 1Anonymous eWMnRr70qNo ratings yet

- Vlsi Technology Kec 053Document1 pageVlsi Technology Kec 053Anonymous eWMnRr70qNo ratings yet

- Temp Dependance of SemiconductorDocument3 pagesTemp Dependance of SemiconductorAnonymous eWMnRr70qNo ratings yet

- Unit 5 FABRICATION OF DEVICESDocument28 pagesUnit 5 FABRICATION OF DEVICESAnonymous eWMnRr70qNo ratings yet

- The NOT GateDocument20 pagesThe NOT GateAnonymous eWMnRr70qNo ratings yet

- JFET and MOSFET quiz with answersDocument15 pagesJFET and MOSFET quiz with answersAnonymous eWMnRr70qNo ratings yet

- Carrier Densities in SCDocument29 pagesCarrier Densities in SCNeelam KapoorNo ratings yet

- Fed Question BankDocument5 pagesFed Question BankAnonymous eWMnRr70qNo ratings yet

- Fed Previous Questions and Answers PDFDocument60 pagesFed Previous Questions and Answers PDFAnonymous eWMnRr70qNo ratings yet

- AIM: - A) To Observe and Draw The Static Characteristics of A Zener DiodeDocument3 pagesAIM: - A) To Observe and Draw The Static Characteristics of A Zener DiodeAnonymous eWMnRr70qNo ratings yet

- Band DiagramDocument1 pageBand DiagramAnonymous eWMnRr70qNo ratings yet

- Diode ApplicationsDocument22 pagesDiode ApplicationsAnonymous eWMnRr70qNo ratings yet

- TECHNICAL QUIZ EceDocument7 pagesTECHNICAL QUIZ EceAnonymous eWMnRr70qNo ratings yet

- (A) Structure SpecificationDocument2 pages(A) Structure SpecificationAnonymous eWMnRr70qNo ratings yet

- Latex Practice Example PDFDocument19 pagesLatex Practice Example PDFAnonymous eWMnRr70qNo ratings yet

- Fuzzy Calculus & Possibility Theory1Document1 pageFuzzy Calculus & Possibility Theory1Anonymous eWMnRr70qNo ratings yet

- Iemh 101Document27 pagesIemh 101rajyar1994No ratings yet

- Phillips - Introduction To Quantum MechanicsDocument111 pagesPhillips - Introduction To Quantum MechanicsSamurayGomesDeAguiarBritoNo ratings yet

- Computer ArchitectDocument194 pagesComputer Architectksu2006No ratings yet

- Report Card Comments: Made For Grade 3-4 But Is Suitable For Any Grade. Editable and Very ConvenientDocument11 pagesReport Card Comments: Made For Grade 3-4 But Is Suitable For Any Grade. Editable and Very Convenientrini aprilianiNo ratings yet

- Isaac Asimov - Quick and Easy Math (Rare)Document96 pagesIsaac Asimov - Quick and Easy Math (Rare)CatTheMarauderNo ratings yet

- Teaching Math in Primary GradesDocument40 pagesTeaching Math in Primary GradesChristel Joy Taguba100% (1)

- Unit 1: Computer Evolution Performance Measurement and ArithmeticDocument131 pagesUnit 1: Computer Evolution Performance Measurement and ArithmeticPrachi PandeyNo ratings yet

- BASIC MATH SKILLSDocument6 pagesBASIC MATH SKILLSNathaly ZoaNo ratings yet

- 2 - Macros - Arithmetic - FIle HandlingDocument20 pages2 - Macros - Arithmetic - FIle HandlingT ENGANo ratings yet

- Mathematics IVDocument59 pagesMathematics IVMytz PalatinoNo ratings yet

- MathDocument5 pagesMathRashmia LacsonNo ratings yet

- Solving Polynomial Equations and SequencesDocument53 pagesSolving Polynomial Equations and SequencesNodelyn Reyes100% (1)

- Chap 1Document86 pagesChap 1CAPUNDAN JOANNA MARIENo ratings yet

- Keyword Position, Traffic, and CPC Data for Maths Tables KeywordsDocument45 pagesKeyword Position, Traffic, and CPC Data for Maths Tables KeywordsNarayanNo ratings yet

- Year 7 Core Curriculum Chapter 2: Calculations: Challenge ExtraDocument68 pagesYear 7 Core Curriculum Chapter 2: Calculations: Challenge Extrasohailnoreen5062No ratings yet

- Unit I. Integer and Rational Exponents: Engr. Annalyn D. Soria LecturerDocument26 pagesUnit I. Integer and Rational Exponents: Engr. Annalyn D. Soria LecturerAnnalyn Duculan SoriaNo ratings yet

- A Low-Error Energy-Efficient Fixed-Width Booth Multiplier With Sign-Digit-Based Conditional Probability EstimationDocument5 pagesA Low-Error Energy-Efficient Fixed-Width Booth Multiplier With Sign-Digit-Based Conditional Probability Estimationsunandha reddyNo ratings yet

- Enjoy MathematicsDocument47 pagesEnjoy MathematicsPrashant AzadNo ratings yet

- 100+ Math Vocabulary Oleh Pateron IndonesiaDocument3 pages100+ Math Vocabulary Oleh Pateron Indonesiaferdi YansahNo ratings yet

- Summary, Findings, Conclusions, and Recommendations: Divine Word College of Laoag Graduate SchoolDocument44 pagesSummary, Findings, Conclusions, and Recommendations: Divine Word College of Laoag Graduate SchoolJohn Lewis SuguitanNo ratings yet

- Prealgebra OPDocument1,146 pagesPrealgebra OPHoa Dinh Nguyen100% (4)

- Is 3646 3 1968Document56 pagesIs 3646 3 1968sumit4u13No ratings yet

- Scheme of Work Maths Stage 8Document18 pagesScheme of Work Maths Stage 8Sue Adames de VelascoNo ratings yet

- Rational Numbers ExplainedDocument74 pagesRational Numbers ExplainedBestowal Infotechs 2018No ratings yet

- Adding and Subtracting PolynomialsDocument12 pagesAdding and Subtracting PolynomialsDevora Cuanan Lasit-BarbadilloNo ratings yet

- Practice SettttttttttDocument15 pagesPractice SettttttttttjhanelleNo ratings yet

- Programming in Python: 1.1 Getting Started With PythonDocument41 pagesProgramming in Python: 1.1 Getting Started With Python2018 01097No ratings yet

- MYP1-U1 ARCHIVE - What Is Less Than Nothing Unit Planner v2Document5 pagesMYP1-U1 ARCHIVE - What Is Less Than Nothing Unit Planner v2Yueping ShanNo ratings yet

- Class 5 Cbse Maths Syllabus 2012-13Document17 pagesClass 5 Cbse Maths Syllabus 2012-13Sunaina RawatNo ratings yet

- Chapter1 PDFDocument30 pagesChapter1 PDFMin AbdullahNo ratings yet