Professional Documents

Culture Documents

Pr0236e04 0001

Uploaded by

Psd VisaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pr0236e04 0001

Uploaded by

Psd VisaCopyright:

Available Formats

Preliminary Product Brief

AnadigmFilter1™

Universal Programmable Filter

6th Order, DC up to 600kHz with Gain

Anadigm's AnadigmFilter™ is the first of a family of chipsets from Anadigm using its dynamically programmable

Analog Signal Processor (dpASP) plus State Machine to realize a dynamically programmable universal analog filter.

This first application solution realizes 6th order filters, Low pass, band pass, high pass or band stop circuits can be

configured with filters approximating to Butterworth, Bessel, chebyshev or inverse chebyshev. Further there are two

pass/stop band widths for the band pass and band stop filters and the ability to configure the circuit to bypass mode

which provides a flat unfiltered response.

It consists of a choice of 2 fixed input stages which can be configured using external resistors and capacitors to

provide any or all of the following: gain or attenuation, level shifting, single-ended to differential conversion, 1st order

lowpass or highpass filtering. In addition within the core of the dpASP device there is 6th order filter which can be

programmed via a simple 16 bit control word, either statically by hardwiring or setting DIP switches on 16 inputs, or

dynamically from a controller using a 16 bit data bus.

Both gain and stop band frequency can be dynamically programmed on the fly WITHOUT interruption to the signal.

In addition, the user can select between one of two inputs, or both inputs summed, or both inputs disconnected. The

outputs are fully differential for greater immunity to noise and supply ripple.

Power in operation is typically 200mW and there is a low current standby mode.

Bandpass

Bandstop

Highpass

Lowpass

AnadigmFilter1™ Features Filter Topology and

• 128 Programmable stop band frequency for each approximation

input clock frequency (input clock is user defined). Availability chart

These frequencies settings are arranged in octaves

with 8 settings/octave or 9% spacing or step size. Butterworth 3 3 2 2

• Programmable stop band frequency from DC upto Bessel 3 3 3 3

500kHz low pass, 100kHz high pass, 600kHz band Chebyshev 3 3 2 2

pass, 120kHz band stop Inverse Chebyshev 2 2 3 3

• Programmable gain – 8 settings in 3dB steps

• Frequency and gain programmable without signal

Bandpass

Bandstop

Highpass

interruption.

Lowpass

Filter variables

• 4 Filter types – Butterworth, Chebyshev, Inverse Availability chart

Chebyshev (0.5dB passband ripple) and Bessel.

• Extremely simple to use 16 pin programming

interface for static or dynamic programming.

3 3 3 3

• 2 input stages configurable using external

8 values of Fc/octave

Selectable 1 or 2 inputs

resistors and capacitors for optimum signal 3 3 3 3

with summing stage

interfacing and additional filter.

• Differential or single-ended signal input Gain selection

3 3 3 3

• Fully differential analog signal outputs for better

Mute to 18db in 3dB steps

immunity to noise and supply ripple Maximum Fc (kHz) 500 100 600 120

Wide and narrow filter - - 3 3

AnadigmFilter™ Benefits

Gain and Frequency dynamically programmable without

Low operational power 190mW, low standby current 20mW

signal interruption

Extremely simple to use programming interface Easy interfacing to analog signals

Choice of filter topology and approximations Reduced number of system components

AnadigmFilter, AN236K04, Product Brief Doc No. PR0236E04-0001b

dpASP Sub Module - Analog signal path AnadigmFilter1 Solution uses 2 ICs

(Functionally equivalent drawing)

LowPass

HighPass

BandPass

Differential

Summing

stage with

Variable

Gain

BandStop

Clock

divider/scaler

6th order

FCLKout Control Variable Fc,

interface filters

To calculate the corner or center frequency of any filter use the following equation

CORNER FREQUENCY = ( F(aclk) / “Divisor_B” ) * “Divisor_A” * “Divisor_C”

F(aclk) is the external clock frequency applied to the AN231E04 device ACLK pin, pin number 34.

Divisor A, B and C, see table below.

AnadigmFilter1 (lower 8 bits of the 16 Bit Configuration Word)

Divisor_B Divisor_A Divisor_C

Internal Clock divider settings, Filter Fc settings Filter topology max

(divider to scale Fc in octave steps) (9% steps across octave) Fc factor

B4 B3 B2 B1 A3 A2 A1

C6 C5 C4 C3 C2 C1 C0

Pin 13 Pin 14 Pin 15 Pin 16 Pin 17 Pin 18 Pin 19

B4,B3,B2,B1 DivisorB A3,A2,A1 DivisorA

0000 1 000 1.0 low pass 0.05

0001 2 001 0.917 High Pass 0.01

0010 4 010 0.841 Bandpass 0.05

0011 8 011 0.771 Bandstop 0.03

0100 16 100 0.707

0101 32 101 0.648

0110 64 110 0.595

0111 128 111 0.545

1000 256

1001 512

1010 1024

1011 2048

1100 4096

1101 8192

1110 16384

1111 32768

AnadigmFilter, AN236K04, Product Brief Doc No. PR0236E04-0001b

ANADIGM AnadigmFilter1 Control Interface (16 Bit Configuration Word)

DivisorB DivisorA

Analog Input Pin Filter

Gain Settings Filter Topology Internal Clock divider settings, Filter Fc settings

settings approximation

(divider to scale Fc in octave steps) (9% steps across octave)

MSB LSB

G3 G2 G1 I2 I1 T4 T3 T2 T1 B4 B3 B2 B1 A3 A2 A1

C15 C14 C13 C12 C11 C10 C9 C8 C7 C6 C5 C4 C3 C2 C1 C0

Pin 2 Pin 3 Pin 4 Pin 5 Pin 6 Pin 7 Pin 10 Pin 11 Pin 12 Pin 13 Pin 14 Pin 15 Pin 16 Pin 17 Pin 18 Pin 19

G3,G2,G Active Filter

Gain (dBs) I2,I1 T4,T3 B4,B3,B2,B1 DivisorB A3,A2,A1 DivisorA

1 input(s) topology The Filter

000 -infinity (Mute) 00 None 00 Lowpass Approximation 0000 1 000 1.0

applied depends

001 0.0 01 Input A 01 Highpass 0001 2 001 0.917

upon the Filter

010 3.0 10 Input B 10 Bandpass topology 0010 4 010 0.841

011 6.0 11 Bandstop selected. 0011 8 011 0.771

A&B

11

100 9.0 Note1 0100 16 100 0.707

See Table insert

101 12.0 to the lower left 0101 32 101 0.648

110 15.0 0110 64 110 0.595

111 18.0 0111 128 111 0.545

Filter Approximation Applied T4,T3 T2,T1 Comme Width Limits (FCLK = ACLK / DivisorB) 1000 256

t

Lowpass Butterworth 00 00 n/a Max Fc = 400kHz @ FCLK(max) = 8MHz 1001 512

Lowpass Chebyshev 00 01 n/a Max Fc = 500kHz @ FCLK(max) = 10MHz

1010 1024

Lowpass Bessel 00 10 n/a Max Fc = 250kHz @ FCLK(max) = 5MHz

Lowpass Bypass 00 11 n/a Max Fc = 1000kHz @ FCLK(max) = 10MHz

1011 2048

Highpass Butterworth 10 00 n/a Max Fc = 60kHz @ FCLK(max) = 6MHz 1100 4096

Highpass Chebyshev 10 01 n/a Max Fc = 100kHz @ FCLK(max) = 10MHz 1101 8192

Highpass Bessel 10 10 n/a Max Fc = 50kHz @ FCLK(max) = 5MHz

n/a

1110 16384

Highpass Bypass 10 11 Max Fc = 1000kHz @ FCLK(max) = 10MHz

Bandpass Inverse Chebyshev 01 00 narrow 10% Max Fc = 500kHz @ FCLK(max) = 10MHz 1111 32768

Bandpass Bessel 01 01 narrow 10% Max Fc = 600kHz @ FCLK(max) = 12MHz

Bandpass Inverse Chebyshev 01 10 wider 40% Max Fc = 500kHz @ FCLK(max) = 10MHz

Bandpass Bessel 01 11 wider 40% Max Fc = 600kHz @ FCLK(max) = 12MHz

Bandstop Inverse Chebyshev 11 00 narrow 20% Max Fc = 120kHz @ FCLK(max) = 4MHz

Bandstop Bessel 11 01 narrow 20% Max Fc = 120kHz @ FCLK(max) = 4MHz

Bandstop Inverse Chebyshev 11 10 wider 80% Max Fc = 120kHz @ FCLK(max) = 4MHz

Bandstop Bessel 11 11 wider 80% Max Fc = 120kHz @ FCLK(max) = 4MHz

Notes

1) If inputs A and B are selected then the two active input signals will be summed.

2) Setting of five 0’s for the control bits C[15:11] (zero gain and no inputs selected) causes the FPAA to be reset and AnadigmFilter to go into standby (approx 6mA from 3.3volts)

3) Max Fc, or maximum Filter Corner or Center Frequency limits have been determined for better than 1% accurate filter parameters, exceeding these limits will result in loss of filter accuracy.

4) Bypass filter approximation provides a flat response from d.c. to FCLK * 0.1. (FCLK = ACLK / Divisor_B ). Divisor_A inputs have no effect in this mode, gain and input select still apply.

5) Divisor_A step size is mathematically equal to (8thsqrt(2) or ((2)^^(1/8).

6) FCLK (= ACLK / DivisorB) is provided on an output pin from the AN231E04, the primary purpose of this signal is to enable synchronization of any subsequent ADC,

AnadigmFilter, AN236K04, Product Brief Doc No. PR0236E04-0001b

+3.3V +3.3V

Evaluation Kit

Product codes

Volume Chipset

Sample Chipset

AN231E04 10k AN236C04

dpASP 44 36 25 10

State Machine

40

+3.3V

1 1 20

I1P + VDD VSS Gnd

ERRb

RSTb

DVDD

BVDD

AVDD

INA 2 _ 2 19

I1N C15 C0

3 3 C14 18

O1N C1

AnadigmFilter, AN236K04, Product Brief

4 4 17

O1P 14 C13 C2

O3P 5 16

13 OUT C12 C3

AN236K04-EVAL2

6 O3N 6 15

O2P C11 C4

7 7 14

O2N C10 C5

8 _ 8 CLK

I2N SCLK C6 13

INB 9 12

I2P + SI

9 DAT C7

For more information:

10 11

web: www.anadigm.com

C9 C8

Telephone: +1 480 422 0191

Email: support@anadigm.com

FCLK

MODE

VMR

CS2b

CS1b

ACLK

DVSS

BVSS

AVSS

34 39 27 31 32 35 37 29 5

External 100n Gnd

Clock

Gnd

pull-downs

Gnd

DIP Switches x 16

AN236K04-SETTY (contains 1 x AN231E04-QFNTY and 1 x AN236C04-SSOTU)

AN236K04-SETSP (contains 1 x AN231E04-QFNSP and 1 x AN236C04-SSOSP)

+3.3V

Control Word C[15:0] C[15:13] C[12:11] C[10:9] C[8:7] C[6:3] C[2:0]

Gain Input Filter Filter Clock Corner

Select Type Sub- Divisor Frequency Fo

Doc No. PR0236E04-0001b

You might also like

- EDR ENews 071Document4 pagesEDR ENews 071Psd VisaNo ratings yet

- Continued Pushups in 6 Weeks With Absolutely Shredded, Visual Impact Main Course, Visual Impact Prinatable ChartDocument7 pagesContinued Pushups in 6 Weeks With Absolutely Shredded, Visual Impact Main Course, Visual Impact Prinatable ChartPsd VisaNo ratings yet

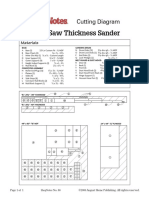

- Thickness Sander PDFDocument1 pageThickness Sander PDFPsd VisaNo ratings yet

- T Hile TransformDocument1 pageT Hile TransformPsd VisaNo ratings yet

- Rangemaster2 Solution For Rfid Tag Readers: PreliminaryDocument4 pagesRangemaster2 Solution For Rfid Tag Readers: PreliminaryPsd VisaNo ratings yet

- Call of Duty - Far Cry - Assassins Creed - Crysis - Tomb Rider - Max Payne - Farcry - Gta - Racing - Sniper Elite - Cricket - Commandos - BatmanDocument1 pageCall of Duty - Far Cry - Assassins Creed - Crysis - Tomb Rider - Max Payne - Farcry - Gta - Racing - Sniper Elite - Cricket - Commandos - BatmanPsd VisaNo ratings yet

- Tec PDFDocument3 pagesTec PDFPsd VisaNo ratings yet

- Mohanaya 01Document19 pagesMohanaya 01Psd Visa100% (1)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- LED SignalDocument34 pagesLED SignalM Mubashshir WarisNo ratings yet

- DDR 30Document42 pagesDDR 30FERNANDO CONTRERASNo ratings yet

- TextDocument1 pageTextEliyanto E BudiartoNo ratings yet

- Passive Optical Network of Company ECIDocument39 pagesPassive Optical Network of Company ECIKundan VanamaNo ratings yet

- Sistem DSC PDFDocument42 pagesSistem DSC PDFCiufi 1No ratings yet

- Xerox XD100-102-104 Service ManualDocument331 pagesXerox XD100-102-104 Service ManualNorton YuNo ratings yet

- Pdfslide - Tips Astm-D7240Document4 pagesPdfslide - Tips Astm-D7240YosiichiHuapayaTamuraNo ratings yet

- Westin Premier Electric MotorDocument4 pagesWestin Premier Electric MotorSandi AslanNo ratings yet

- AC Series MotorsDocument8 pagesAC Series Motorsゞ『HaiDerツ98〆No ratings yet

- lm00614 Onboard DC Grid Brochure - June2014 - 1 PDFDocument8 pageslm00614 Onboard DC Grid Brochure - June2014 - 1 PDFStefanitaNo ratings yet

- ART 312A: Active SpeakerDocument4 pagesART 312A: Active SpeakerMaikel Borges IglesiasNo ratings yet

- gx5500s MoDocument100 pagesgx5500s MoHenry AlvaxNo ratings yet

- Philips TV 7607 Service ManualDocument257 pagesPhilips TV 7607 Service ManualPlayer NumberNo ratings yet

- Foxboro™ SCADA SCD6000 Controller - 41s2m17Document25 pagesFoxboro™ SCADA SCD6000 Controller - 41s2m17Muhd Nu'man H100% (1)

- 14af45 14af45c SVMDocument50 pages14af45 14af45c SVMLuis MorenoNo ratings yet

- CMOS VLSI DESIGN NOTES Made by Barun Dhiman From Various Books Like Kamran Neil E WasteDocument226 pagesCMOS VLSI DESIGN NOTES Made by Barun Dhiman From Various Books Like Kamran Neil E WasteBarun DhimanNo ratings yet

- SEW 5500CB Datasheet PDFDocument2 pagesSEW 5500CB Datasheet PDFSaul Pablo Maita FarfanNo ratings yet

- Lithium Battery UN38.3 Test Report: Prepared ForDocument14 pagesLithium Battery UN38.3 Test Report: Prepared ForBikash Kumar MallickNo ratings yet

- KINETROL Rotary ActuatorDocument56 pagesKINETROL Rotary ActuatorJoseNo ratings yet

- Striker 2: Instruction ManualDocument7 pagesStriker 2: Instruction ManualFredy Andres ValenciaNo ratings yet

- Icepower250A: 250W General Purpose Icepower AmplifierDocument17 pagesIcepower250A: 250W General Purpose Icepower AmplifierJoão LopesNo ratings yet

- Anasthesa Unit VentilatorDocument6 pagesAnasthesa Unit VentilatorWidhiatmoko SangjendralNo ratings yet

- bmp180 Pressure Sensor TutorialDocument14 pagesbmp180 Pressure Sensor Tutorialapi-248437787No ratings yet

- R-L-C Circuit Analysis: ProcedureDocument2 pagesR-L-C Circuit Analysis: ProcedureAbhyuday ChauhanNo ratings yet

- Eee1001 Basic-Electrical-And-Electronics-Engineering Eth 1.0 37 Eee1001 PDFDocument2 pagesEee1001 Basic-Electrical-And-Electronics-Engineering Eth 1.0 37 Eee1001 PDFboomaNo ratings yet

- Solar PV SystemDocument40 pagesSolar PV SystemAbdullahNo ratings yet

- Memory SegmentationDocument38 pagesMemory SegmentationVinaya SreeNo ratings yet

- Digital Energy GT Series: User ManualDocument20 pagesDigital Energy GT Series: User ManualWilton AlvesNo ratings yet

- Passive and Active Battery Balancing Comparison Based On MATLAB SimulationDocument7 pagesPassive and Active Battery Balancing Comparison Based On MATLAB SimulationNhật NguyễnNo ratings yet

- Arema FullDocument2,686 pagesArema Fulldiablopapanatas86% (7)