Professional Documents

Culture Documents

Dlda - It

Uploaded by

nitin_s_chauhan5239Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dlda - It

Uploaded by

nitin_s_chauhan5239Copyright:

Available Formats

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

EXPERIMENT NO 1 :-STUDY OF GATES

Aim: To study basic logic gates and derived logic gates on IC’s .

Apparatus: Digital IC trainer kit, connecting wires,

IC 7402, IC 7400, IC7408, IC 7404, IC7486, IC 7432, IC74266.

Theory: Gate is a logic circuit with one or more inputs but only one output. Gates are digital

(two state) circuit because the input & output are either low or high.Gates provide high

output for certain combinations of input & for other combinations the output is low.

Total number of combinations for a gate is 2n; Where n is number of input.

Classification: The two types of gate are:

1: Basic or Fundamental Gates: 2: Derived Gates:

• OR gate • NAND gate

• AND gate • NOR gate

• NOT gate • X-OR gate

• X-NOR gate

1) Basic Gates:

OR gate: The OR gate has two or more inputs but only 1 output. If any or all the inputs are

high, the output is high. If all the inputs are low, the output is low.

Y=A+B For number of inputs;

Where, Y is output A, B are inputs Y=A+B+C+D+…. +N.

Rules for OR operations are: 0+0=0

0+1=1 A

1+0=1 B Y=A+B

1+1=1

AND gate: The AND gate has two or more inputs but only one output. If any or all inputs are

high then output is also high

Y=A.B For number of inputs;

Where; Y is output A, B are inputs Y=A.B.C.D……N

Rules for AND operations are; 0.0=0

0.1=0 A

1.0=0 B Y=A.B

1.1=1

Information Technology Department Digital Logic Design And Applications 1

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

NOT gate: The Not gate is a gate with only one input and one output. The output is always in

opposite state of an input. A NOT gate is also called as Inverter because it performs inversion.

Y= Not A. Where, Y is output and A is input; A Y=A

Rules for NOT operations are : 0 = 1 and

1=0

2) Derived Gates :

EX-OR gate : The EX-OR gate has two or more inputs but only one output. For odd no of ones

as a input output of EX-OR gate is high.

Y=A O B For number of inputs;

Where; Y is output A, B are inputs Y=A O B O C O D…… O N

Rules for EX-OR operations are; 0O0=0

0O1=1 A

1O0=1

1O1=0 B Y=AOB

NOR gate : The NOR gate has two or more inputs but only one output.If any of its input is

HIGH then it will give LOW output and only when all of its inputs are LOW the output is HIGH

Y=A+B For number of inputs;

Where, Y is output A, B are inputs Y=A+B+C+D+…. +N.

Rules for NOR operations are: 0+0=0

0+1=1 A

1+0=1 B Y=A+B

1+1=1

EX-NOR gate : The EX-NOR gate has two or more inputs but only one output. For even no of

ones or all zeroes the output of this gate is high.

Y=A O B For number of inputs;

Where; Y is output A, B are inputs Y=A O B O C O D…… O N

Rules for EX-OR operations are; 0O0=1

0O1=0 A

1O0=0

1O1=1 B Y=AOB

Information Technology Department Digital Logic Design And Applications 2

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

NAND gate : The NAND gate has two or more inputs but only one output. When any of the

input is low the output will be high.

Y=A.B For number of inputs;

Where; Y is output A, B are inputs Y=A.B.C.D……N

Rules for NAND operations are; 0.0=1

0.1=1 A

1.0 =1 Y=A.B

1.1 =0 B

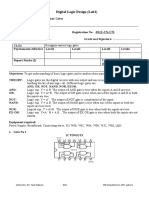

Pin Diagrams :

Conclusion :

Information Technology Department Digital Logic Design And Applications 3

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

EXPERIMENT NO 2 :- 2’S COMPLEMENT SUBTRACTION

Aim : 2’s Complement subtraction using IC 7483.

Apparatus: Digital Trainer kit, connecting wires, IC 7483.

Theory: For subtraction of one binary number from another, we do so by adding 2’s

complement of the former to the latter number using a full adder circuit.IC 7483 is a 16

pin, 4-bit full adder. This IC has a provision to add the carry output to transfer and end

around carry output using Co and C4 respectively. Pin diagram is as shown in fig. 2’s

complement: 2’s complement of any binary no. can be obtained by adding 1 in 1’s

complement of that no.

e.g. 2’s complement of +(10)10 =10102 is as follows

1C of 1010 0101

+1

-(10)10 0110

In 2’s complement subtraction using IC 7483, we are representing negative number in 2’s

complement form and then adding it with 1st number. Circuit connection is as shown in fig.

Procedure:

1) Locate the IC 7483 and 4-not gates block on trainer kit.

2) Connect 1st input no. to A4-A1 input slot and 2nd (negative) no. to B4-B1 through 4-not

gates(1C of 2nd no.)

3) Connect high input to Co so that it will get added with 1C of 2nd no. to get 2C.

4) Connect 4-bit output to the output indicators.

5) Switch ON the power supply and monitor the output for various input combinations.

Example: 710 -210 = 510

7 0111 0111

2 0010 + 1110

1C of 2 1101 1 0101

+1

2C of 2 1110

Information Technology Department Digital Logic Design And Applications 4

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

PIN Diagram:

Logic Diagram:

Conclusion :

Information Technology Department Digital Logic Design And Applications 5

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

EXPERIMENT NO 3 :- 4-BIT MAGNITUDE COMPARATOR

Aim: To verify 4-bit magnitude comparator using IC 7485.

Apparatus: Digital Trainer kit, connecting wires, IC 7485.

Theory: IC 7485 is a 4-bit comparator. It compares two 4-bit words. Three fullydecoded

decisions (A > B, A < B, and A = B) about two, 4-bit words (A, B) are made and

are

externally available at three outputs. These devices are fully expandable to any

number of bits without external gates. Words of greater length may be compared

by connecting comparators in cascade.The A > B, A < B, and A = B outputs of a

stage handling less-significant bits are connected to the corresponding inputs of

the next stage handling more significant bits.The stage handling the least-

significant bits must have a high-level voltage applied to the A = B input as shown

Procedure: 1) Make connection as shown in the circuit diagram.

2) Connect high logic to A=B IN output.

3) Apply 1st number to A4-A1 and 2nd number to B4-B1 input for

comparison.

4) Connect three OUT outputs to output indicators.

5) Apply different inputs and verify the output.

Pin Diagram:

Logic Diagram:

Comparison Table:

Comparing CASCADING INPUTS CASCADING OUTPUTS

inputs I(A<B) I(A=B) I(A>B) Y(A<B) Y(A=B) Y(A>B)

A<B X X X 1 0 0

0 0 0 1 0 1

0 0 1 0 0 1

Information Technology Department Digital Logic Design And Applications 6

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

A=B 1 0 0 1 0 0

1 0 1 0 0 0

X 1 0 1 1 0

A>B X X X 0 0 1

Conclusion:

EXPERIMENT NO 4 : - MULTIPLEXER

Aim: To study Multiplexer using IC 74151.

Apparatus: Digital trainer kit, connecting wires, IC 74151.

Theory : Multiplexer is a digital switch. It allows digital information from several sources to

be routed onto a single output line. The basic multiplexer has several data-input

lines and a single output line. The selection of particular input line is controlled by

a set of selection lines. Normally, there are 2n input lines and n selection lines

whose bit combinations determine which input is selected. Therefore, multiplexer

is ‘many into one’ and it provides the digital equivalent of an analog selector switch.

The 74151 8-to-1 Multiplexer.

It is a 8 to 1 multiplexer. It has eight inputs. It provides two outputs one is active high and

other is active low. There are three sect inputs A, B, C which select one of the eight input. This

IC is provided with active low enable input.

In this following table for each input combinations output is not specified in 1s and 0s.

because, we know that, multiplexer is a data switch, it does not generate any data of its own, but

it simply passes external input data from the selected input to the output.

Truth table

Input Output

Select Enable

A B C EN Y Y

X X X 1 0 1

Information Technology Department Digital Logic Design And Applications 7

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

0 0 0 0 D0 D0

0 0 1 0 D1 D1

0 1 0 0 D2 D2

0 1 1 0 D3 D3

1 0 0 0 D4 D4

1 0 1 0 D5 D5

1 1 0 0 D6 D6

1 1 1 0 D7 D7

Logic Diagram :

Pin Diagram :

Information Technology Department Digital Logic Design And Applications 8

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

Conclusion :

EXPERIMENT NO 5 : - CODE CONVERTER

Aim: To study the code converter.

Apparatus: Digital Trainer kit, connecting wires, IC 7485.

Theory : There is a wide variety of binary codes used in digital systems. Some of these codes are

binary-coded-decimal (BCD), Excess-3, gray, and so on. Many times it is required to convert one

code to another. That’s why we used code converter.

Here we study about Gray to Binary and Binary to Gray code converter.

The gray code is often used in digital systems because it has the advantage that only one bit in

the numerical representation changes between successive numbers.

Binary To Gray

Decimal Binary code Gray code

B3 B2 B1 B0 G3 G2 G1 G0

0 0 0 0 0 0 0 0 0

1 0 0 0 1 0 0 0 1

2 0 0 1 0 0 0 1 1

3 0 0 1 1 0 0 1 0

4 0 1 0 0 0 1 1 0

5 0 1 0 1 0 1 1 1

6 0 1 1 0 0 1 0 1

7 0 1 1 1 0 1 0 0

8 1 0 0 0 1 1 0 0

9 1 0 0 1 1 1 0 1

Information Technology Department Digital Logic Design And Applications 9

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

10 1 0 1 0 1 1 1 1

11 1 0 1 1 1 1 1 0

12 1 1 0 0 1 0 1 0

13 1 1 0 1 1 0 1 1

14 1 1 1 0 1 0 0 1

15 1 1 1 1 1 0 0 0

Note: Draw k map for G0, G1, G2, G3 and write equations for each. And draw logic diagram for

binary to gray code converter.

Gray To Binary :

Gray code Binary code

G3 G2 G1 G0 B3 B2 B1 B0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 1

0 1 0 1 0 1 1 0

0 1 1 0 0 1 0 0

0 1 1 1 0 1 0 1

1 0 0 0 1 1 1 1

1 0 0 1 1 1 1 0

1 0 1 0 1 1 0 0

1 0 1 1 1 1 0 1

1 1 0 0 1 0 0 0

1 1 0 1 1 0 0 1

1 1 1 0 1 0 1 1

1 1 1 1 1 0 1 0

Note: Draw k map for B0, B1, B2, B3 and write equations for each. And draw logic diagram for

gray TO binary code converter.

Conclusion :

Information Technology Department Digital Logic Design And Applications

10

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

EXPERIMENT NO 6 : - FLIP-FLOPS

Aim: To study flip flops (J-K, D, and T flip flop) using IC 7476.

Apparatus: Digital trainer kit, connecting wires, IC 7476.

Theory: "Flip-flop" is the common name given to two-state devices which offer basic

memory for sequential logic operations. Flip-flops are heavily used for digital data

storage and transfer and are commonly used in banks called "registers" for the

storage of binary numerical data.

JK Flip Flop: JK-flip flop has two inputs, traditionally labeled J and K. IC 7476 is a dual JK

master slave flip flop with preset and clear inputs. If J and K are different then the

output Q takes the value of J at the next clock edge. If J and K are both low then no change

occurs. If J and K are both high at the clock edge then the output will toggle from one state to the

other. It can perform the functions of the set/reset flip-flop and has the advantage that there are

no ambiguous states.

D Flip Flop: D flip-flop tracks the input, making transitions with match those of the input D.

The D stands for "data"; this flip-flop stores the value that is on the data line. It can

be thought of as a basic memory cell. D flip-flop can be made from J-K flipflop by connecting

both inputs through a not gate as shown in fig.

T Flip Flop: T or "toggle" flip-flop changes its output on each clock edge, giving an output

which is half the frequency of the signal to the T input. It is useful for constructing

binary counters, frequency dividers, and general binary addition devices. It can be made from a

J-K flip-flop by tying both of its inputs high.

Information Technology Department Digital Logic Design And Applications

11

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

Procedure: 1) Locate IC 7476 on Digital trainer kit

2) Apply various inputs to J & K pins by means of the output on logic

output indicator.

3) Connect a pulsar switch to the clock input.

4) Connect the J&K as D and T flip flop as shown in diagrams and verify

the respective Truth Tables.

Observations :

D Flip-flop Logic Diagram :(draw logic diagram for D, JK and T F/F)

D O/P

0 0

1 1

J-K Flip-flop

Q J K Qn+1 Q n+1

0 0 0 0 1

0 0 1 0 1

0 1 0 1 0

0 1 1 1 0

1 0 0 1 0

1 0 1 0 1

1 1 0 1 0

1 1 1 0 1

T Flip-flop

T O/P

0 Qn

1 Qn

Pin Diagram :

Information Technology Department Digital Logic Design And Applications

12

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

Conclusion :

EXPERIMENT NO 7 :- MOD-100 COUNTER

Aim: To study MOD 100 counter using IC 7490 and IC 7493.

Apparatus: Digital trainer kit, connecting wires.

Theory: IC 7490: The 7490 integrated circuit counts the number of pulses arriving at its

input. The number of pulses counted (up to 9) appears in binary form on four pins

of the ic. When the tenth pulse arrives at the input, the binary output is reset to

zero (0000) and a single pulse appears at another output pin. So for ten pulses in

there is one pulse out of this pin. The 7490 therefore divides the frequency of the

input by ten. If this pulse is applied to the input of a second 7490 then this second

ic will count the pulses from the first ic. It will give one pulse out after 100 pulses

have been applied to the first ic. The 7490 can be connected to divide by other

values.

Decimal Binary

0 0000

1 0001

2 0010

3 0011

4 0100

5 0101

6 0110

7 0111

Information Technology Department Digital Logic Design And Applications

13

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

8 1000

9 1001

IC 7493: These are ripple counters so beware that glitches may occur in any logic gate

systems connected to their outputs due to the slight delay before the later counter

outputs respond to a clock pulse. The count advances as the clock input becomes

low (on the falling-edge), this is indicated by the bar over the clock label. This is

the usual clock behavior of ripple counters and it means a counter output can

directly drive the clock input of the next counter in a chain.

The counter is in two sections: clockA-QA and clockB-QB-QC-QD. For normal use

connect QA to clockB to link the two sections, and connect the external clock signal to clockA.

For normal operation at least one reset0 input should be low, making both high

resets the counter to zero (0000, QA-QD low). Note that the 7490 has a pair of reset9 inputs on

pins 6 and 7, these reset the counter to nine (1001) so at least one of them must be low for

counting to occur.

Counting to less than the maximum (9 or 15) can be achieved by connecting

theappropriate output(s) to the two reset0 inputs. If only one reset input is required the two inputs

can be connected together. For example: to count 0 to 8 connect QA (1) and QD (8) to the reset

inputs.

MOD 100 counter : A Mod 100 counter can be created by cascading IC7490 and Ic 7493.

These IC’s can be individually act as MOD-10 counters. The clock pulse

is applied to a input of 7493, pin1 and 12 are shorted, output of Qb is

connected to pin2 and output of Qd is connected to pin 3. Iutput of IC

7493 is connected to a input of IC 7490. Preset and Reset pins of 7490

are connected to ground. The output of IC 7493 is treated as LSB. This

circuit counts pulses from 0 to 99.

Pin Diagram :

Logic Diagram: MOD-100 using IC 7490 and IC 7493

Information Technology Department Digital Logic Design And Applications

14

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

Conclusion :

EXPERIMENT NO 8 :- STUDY BASIC LOGIC GATES USING VHDL.

Aim: To study Basic logic gates using VHDL on FPGA/CPLD.

Apparatus: VHDL s/w, FPGA/CPLD kit, connecting wires, etc.

Theory: VHDL is stands for ‘Very High Speed Integrated circuit Hardware Description

Language’. It is inherently parallel i.e. commands which responds to logic gate are

executed to parallel as soon as input arrives. Level of Representation and Abstraction:

The highest level of abstraction to the behavioral level that decribes the system in terms of its

components and interconnection between them. A behavioral description specifies the

relationship between the input and output. The structural level describes that are interconnected

to perform a desired task. A structural description can be compared to a schematic of

interconnected logic gates.

Entity declaration:The entity declaration defines the name of entity and lists the inputs and

outputs.

Entity NAME_OF_ENTITY is

Port(signal name : mode type;

___;

___;

___);

end ENTITY_NAME;

Information Technology Department Digital Logic Design And Applications

15

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

The architecture body specifies how the circuit operates and how it is

implemented. The architecture body tools_

Architecture ARCHITECTURE_NAME of ENTITY_NAME

_Declaration

_Components Declaration

_Signal Declaration

_Constant Declaration

_Function Declaration

_Procedure Declaration

_Type Declaration

Behavioral Modeling: Sequential Statement:

a) Process: A process statement is the main construct in behavior modeling that allows to

describe the behavior of system over time. The system of process statement is :

[process label=]process[(sensitivity list)][is][process declaration]

begin

list of sequential statements such as :

Signal assignment

Variable assignment

Case statement

If statement

Loop statement

Next statement

:

:

end process[process label];

a process is declared within an architecture and is a concurrent statement. However the statement

inside a process is executes sequentially. A process reads and writes signals and values if the

interface port to indicate root of architecture.

****Basic Gates Using VHDL****

Library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declaration that are provided for

-- instantiating Xilink Primitive components.

-- library UNISIM;

-- use UNISIM.VComponents.all;

entity logic_gates is

Information Technology Department Digital Logic Design And Applications

16

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

Port(a: in std_logic;

b: in std_logic;

c: out std_logic;

d: out std_logic;

e: out std_logic);

end logic_gates;

architecture Behavioral of logic_gates is

begin

c<= not a;

d<= a and b;

e<= a or b;

end Behaviral;

Conclusion:

EXPERIMENT NO 9 :- 4:1 MUX USING VHDL.

Aim: Implementation of 4:1 MUX using VHDL and Simulation using ModelSim

Apparatus: VHDL s/w, ModelSim simulator, etc.

Theory: VHDL is stands for ‘Very High Speed Integrated circuit Hardware Description

Language’. It is inherently parallel i.e. commands which responds to logic gate are

executed to parallel as soon as input arrives. Level of Representation and Abstraction:

The highest level of abstraction to the behavioral level that decribes the system in terms of its

components and interconnection between them. A behavioral description specifies the

relationship between the input and output. The structural level describes that are interconnected

to perform a desired task. A structural description can be compared to a schematic of

interconnected logic gates.

Entity declaration:The entity declaration defines the name of entity and lists the inputs and

outputs.

Entity NAME_OF_ENTITY is

Port(signal name : mode type;

___;

___;

___);

end ENTITY_NAME;

Information Technology Department Digital Logic Design And Applications

17

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

The architecture body specifies how the circuit operates and how it is

implemented. The architecture body tools_

Architecture ARCHITECTURE_NAME of ENTITY_NAME

_Declaration

_Components Declaration

_Signal Declaration

_Constant Declaration

_Function Declaration

_Procedure Declaration

_Type Declaration

Behavioral Modeling: Sequential Statement:

a) Process: A process statement is the main construct in behavior modeling that allows to

describe the behavior of system over time. The system of process statement is :

[process label=]process[(sensitivity list)][is][process declaration]

begin

list of sequential statements such as :

Signal assignment

Variable assignment

Case statement

If statement

Loop statement

Next statement

:

:

end process[process label];

a process is declared within an architecture and is a concurrent statement. However the statement

inside a process is executes sequentially. A process reads and writes signals and values if the

interface port to indicate root of architecture.

Multiplexer: MUX or Multiplexer is a special type of combinational circuit that is one of

the most widely used standard circuit in digital design. The block diagram of

multiplexer consist of n-data inputs, one output and m select lines with 2m=n relation.

A multiplexer is a digital circuit which selects one of n data inputs. Selection

of data input is depends upon select inputs.

4:1 MUX : In 4:1 MUX no. of data inputs are n=4, no. of select lines are m=2 so that

2m=n and 1 output. A 4:1 multiplexer is shown in figure below, each of 4 input lines DI0 to DI3

is applied to one input of an AND gate. Selection lines S0 and S1 are decoded to select a

particular AND gate. The truth table for the 4:1 MUX is given in the table below.

Information Technology Department Digital Logic Design And Applications

18

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

Logic:

1) For the implementation of 4:1 MUX using VHDL, according to the truth

table, we take four variables for data input, two variables for select line and one

variable for output. Assigned one of the data input to output depending upon the

combination of select lines.

Circuit Diagram: Truth Table:

S1 S0

o o

S1 S0 Y

D0 0 0 D0

0 1 D1

D1 1 0 D2

Y 1 1 D3

D2

D3

****4:1 Multiplexer Using VHDL****

Library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declaration that are provided for

-- instantiating Xilink Primitive components.

-- library UNISIM;

-- use UNISIM.VComponents.all;

entity mux is

Port(d: in std_logic_vector(3 downto 0)

s: in std_logic_vector(1 downto 0)

y: out std_logic);

end mux;

architecture Behavioral of mux is

begin

y<=d(0) when s=”00” else

d(1) when s=”01” else

d(2) when s=”10” else

d(3) when s=”11”;

end Behaviral;

Information Technology Department Digital Logic Design And Applications

19

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

Conclusion :

EXPERIMENT NO 10 :- 4-BIT SYNCHRONOUS COUNTER

Aim: To implement 4-bit Synchronous counter using VHDL and simulate on

ModelSim.

Apparatus: VHDL s/w, ModelSim simulator, etc.

Theory: VHDL is stands for ‘Very High Speed Integrated circuit Hardware Description

Language’. It is inherently parallel i.e. commands which responds to logic gate are

executed to parallel as soon as input arrives. Level of Representation and Abstraction:

The highest level of abstraction to the behavioral level that decribes the system in terms of its

components and interconnection between them. A behavioral description specifies the

relationship between the input and output. The structural level describes that are interconnected

to perform a desired task. A structural description can be compared to a schematic of

interconnected logic gates.

Entity declaration:The entity declaration defines the name of entity and lists the inputs and

outputs.

Entity NAME_OF_ENTITY is

Port(signal name : mode type;

___;

___;

___);

Information Technology Department Digital Logic Design And Applications

20

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

end ENTITY_NAME;

The architecture body specifies how the circuit operates and how it is

implemented. The architecture body tools_

Architecture ARCHITECTURE_NAME of ENTITY_NAME

_Declaration

_Components Declaration

_Signal Declaration

_Constant Declaration

_Function Declaration

_Procedure Declaration

_Type Declaration

Behavioral Modeling: Sequential Statement:

a) Process: A process statement is the main construct in behavior modeling that allows to

describe the behavior of system over time. The system of process statement is :

[process label=]process[(sensitivity list)][is][process declaration]

begin

list of sequential statements such as :

Signal assignment

Variable assignment

Case statement

If statement

Loop statement

Next statement

:

:

end process[process label];

a process is declared within an architecture and is a concurrent statement. However the statement

inside a process is executes sequentially. A process reads and writes signals and values if the

interface port to indicate root of architecture

Synchronuos Counter: Digital circuit used for counting pulses is known as counter. It is a

Information Technology Department Digital Logic Design And Applications

21

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

sequential circuit. It is a group of flip flops with a clock signal applied.

With some modifications it can be used to measuring frequency as time period.

4-bit Synchronous Counter: In synchronous counter clock pulse is applied to all flip flops

separately which drives each flip flop. In 4-bit synchronous

counter there are 4 flip flops which counts 0000 to 1111 on application of clock pulse. The

circuit diagram is as shown. This concept is used to design it using VHDL.

Logic: To implement the 4-bit synchronous counter using VHDL, we need one variable for

clock pulse which changes between 0 and 1 after specific time duration. Then 4 variable

for 4 bits and one variable to reset the counter.

****Synchronous Counter Using VHDL****

Library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declaration that are provided for

-- instantiating Xilink Primitive components.

-- library UNISIM;

-- use UNISIM.VComponents.all;

entity sync_4 is

Port(clk: in std_logic;

q: out std_logic_vector(3 downto 0)

clr: in std_logic;

ld: in std_logic;

enp: in std_logic;

ent: in std_logic;

tc: out std_logic);

end sync_4;

architecture Behavioral of sync_4 is

signal q_s: std_logic_vector(3 downto 0);

begin

Information Technology Department Digital Logic Design And Applications

22

SES’S

YADAVRAO TASGAONKAR COLLEGE OF ENGINEERING & MANAGEMENT, CHANDAI, KARJAT

process(clk)

begin

if(clk’event and clk=’1’ and clr=’0’)

then q_s<=”0000”;

end if;

if(ent=’1’ and enp=’1’ and clk=’1’)then

q_s<=q_s+1;

end if;

if(q_s=”1111” and ent=’1’ and enp=’1’)

then tc<=’0’;

end if;

end process;

q<=q_s;

end Behaviral;

Conclusion :

Information Technology Department Digital Logic Design And Applications

23

You might also like

- Digital Logic Design: Dcse, Section C Uet, PeshawarDocument9 pagesDigital Logic Design: Dcse, Section C Uet, PeshawarZAINUL ABIDEENNo ratings yet

- Logic Gates and Boolean AlgebraDocument63 pagesLogic Gates and Boolean AlgebraLeng Hour lengNo ratings yet

- Physics Investigatory Project On Logic GatesDocument32 pagesPhysics Investigatory Project On Logic GatesvijuNo ratings yet

- 2CE302 Digital Electronics: Practical 1Document3 pages2CE302 Digital Electronics: Practical 1yagneshNo ratings yet

- Digital Electronics Lab Worksheet: Validation of Truth Tables of Logic GatesDocument10 pagesDigital Electronics Lab Worksheet: Validation of Truth Tables of Logic GatesAnjali ChauhanNo ratings yet

- DE Lab EXP.1,2,3Document18 pagesDE Lab EXP.1,2,3Saksham DhawanNo ratings yet

- DLD - Lab - 1Document7 pagesDLD - Lab - 1Bunty HaqueNo ratings yet

- Lab 5 Universal GatesDocument6 pagesLab 5 Universal Gatessafdarmunir070No ratings yet

- Switching Theory and Logic Design Lab: Paper Code Etec-252Document34 pagesSwitching Theory and Logic Design Lab: Paper Code Etec-252AnishSaxenaNo ratings yet

- Digital ElectronicsDocument42 pagesDigital ElectronicsSailu KatragaddaNo ratings yet

- Microprocessor Lab - Excperiment-01Document4 pagesMicroprocessor Lab - Excperiment-01Samin Sadique AurinNo ratings yet

- Unit LV Digital ElectronicsDocument6 pagesUnit LV Digital ElectronicsSadan SriNo ratings yet

- 1 Basic Logic GateDocument8 pages1 Basic Logic GateSohil VohraNo ratings yet

- Lab 1-DLDDocument4 pagesLab 1-DLDArif KamalNo ratings yet

- Assignment No.01 (DTM) .Document14 pagesAssignment No.01 (DTM) .Om TNo ratings yet

- De All ManualsDocument44 pagesDe All ManualsAbhipsha PatroNo ratings yet

- Digital Electronics ManualDocument49 pagesDigital Electronics ManualPratik SinghNo ratings yet

- Module 4 Part 1Document26 pagesModule 4 Part 1vinuth nNo ratings yet

- Chapter 2 Part ADocument23 pagesChapter 2 Part ANeetesa NepalNo ratings yet

- DLD Lab 1 PDFDocument6 pagesDLD Lab 1 PDFArnab DeyNo ratings yet

- De - Experiment 1Document14 pagesDe - Experiment 1harvi.kotadiya121816No ratings yet

- De Lab Manual 21-22Document46 pagesDe Lab Manual 21-22AUTHOR SOULNo ratings yet

- Chapter One COADocument35 pagesChapter One COAChala GetaNo ratings yet

- DLC LAB - 01 - Student - ManualDocument12 pagesDLC LAB - 01 - Student - ManualCarry GamingNo ratings yet

- DLD Lab Report 3 - 010324Document4 pagesDLD Lab Report 3 - 010324haideraliNo ratings yet

- Verification of Basic Logic Gates Lab ReportDocument4 pagesVerification of Basic Logic Gates Lab ReportFarjana KabirNo ratings yet

- Physics Project For Class 12Document17 pagesPhysics Project For Class 12intustan leeNo ratings yet

- Lecturenote - 1541580522chapter 1Document17 pagesLecturenote - 1541580522chapter 1tasheebedaneNo ratings yet

- Digital ElectronicsDocument8 pagesDigital ElectronicsSabiha Benta Sayed BadhonNo ratings yet

- Physics Logic GatesDocument19 pagesPhysics Logic GatesMohit RaoNo ratings yet

- DLD LabDocument4 pagesDLD LabSalman KhanNo ratings yet

- Topic 2 - Subtopic 2.2Document49 pagesTopic 2 - Subtopic 2.2Navinaash Chanthra SegaranNo ratings yet

- Logic Gates and Boolean Algebra ImplementationDocument12 pagesLogic Gates and Boolean Algebra ImplementationEdmond100% (1)

- TASK-3: Digital Logic DesignDocument27 pagesTASK-3: Digital Logic DesignHarsha VardhanNo ratings yet

- DLD Lab 1Document5 pagesDLD Lab 1tm tigerNo ratings yet

- Lab Manual - DF - 3130704Document26 pagesLab Manual - DF - 3130704Unknown Person456No ratings yet

- Digital Systems and Signals Lab Manual - 2018Document25 pagesDigital Systems and Signals Lab Manual - 2018ram kumarNo ratings yet

- Experiment No.1 Aim: Objective:: Not Gate: IC 7404 (HEX Inverter) 14 Pin Supply Voltage:5vDocument10 pagesExperiment No.1 Aim: Objective:: Not Gate: IC 7404 (HEX Inverter) 14 Pin Supply Voltage:5vCharanpreet SinghNo ratings yet

- Lecture1616 - 12284 - Logic Gates and SOP POS KMAP1Document32 pagesLecture1616 - 12284 - Logic Gates and SOP POS KMAP1anishkjainalphaNo ratings yet

- Unit - IiDocument143 pagesUnit - IiB SpNo ratings yet

- DSD Lab ManualDocument65 pagesDSD Lab Manualmjeevansai07No ratings yet

- Assignment 1Document12 pagesAssignment 1abuzarkazmi779No ratings yet

- Expt 4 Truth Table Verification of Logic GatesDocument5 pagesExpt 4 Truth Table Verification of Logic GatesSwapnil Babele100% (1)

- DcsDocument50 pagesDcskartikNo ratings yet

- CSE 231 Lab ManualDocument34 pagesCSE 231 Lab Manualdettol skincare33% (3)

- Module-II Logic Gates & Logic FamiliesDocument143 pagesModule-II Logic Gates & Logic Familiesvamshi krishna veerakotiNo ratings yet

- Experiment Name: Study of Basic Logic GatesDocument17 pagesExperiment Name: Study of Basic Logic GatesA K M Fahim Faysal (182016018)No ratings yet

- Index: S.No Experiment Name Date of Experiment Date of Submission Remark & Sign 1Document32 pagesIndex: S.No Experiment Name Date of Experiment Date of Submission Remark & Sign 1Ritwik KumarNo ratings yet

- IDS Lab ManualDocument38 pagesIDS Lab ManualÃMĪT KUMAR SINGHNo ratings yet

- Lab Reportuhhh PDFDocument6 pagesLab Reportuhhh PDFMuhammad ShahidNo ratings yet

- DLD Lab Report 3 PDFDocument6 pagesDLD Lab Report 3 PDFArnab DeyNo ratings yet

- Lab 1 Digital Logic Gates and Boolean FunctionsDocument7 pagesLab 1 Digital Logic Gates and Boolean FunctionsIfthakharul Alam Shuvo100% (1)

- Lab Mannual For Digital Electronics LabDocument35 pagesLab Mannual For Digital Electronics LabSia ghoshNo ratings yet

- Digital Logic Technology: Engr. Muhammad Shan SaleemDocument9 pagesDigital Logic Technology: Engr. Muhammad Shan SaleemAroma AamirNo ratings yet

- Digital ElectronicsDocument19 pagesDigital ElectronicsAmitNo ratings yet

- DLD - LAB - MANUAL - New - Verilog Spring 2017 PDFDocument48 pagesDLD - LAB - MANUAL - New - Verilog Spring 2017 PDFAli RaoNo ratings yet

- NEWLGDocument34 pagesNEWLGdaniNo ratings yet

- Physics Investigatory ProjectDocument13 pagesPhysics Investigatory ProjectAnush DcostaNo ratings yet

- Lec - 4-Basic Digital LogicDocument29 pagesLec - 4-Basic Digital LogicNurhussen NureNo ratings yet

- FortiClient 5.6.0 Administration GuideDocument131 pagesFortiClient 5.6.0 Administration GuideSean BaileyNo ratings yet

- 02 LTE KPI ArchitectureDocument104 pages02 LTE KPI ArchitectureVahid ZibakalamNo ratings yet

- Direct Transient ResponseDocument24 pagesDirect Transient Responseselva1975No ratings yet

- Website Launch Checklist - 25 Must-Dos Before Going Live - ElementorDocument34 pagesWebsite Launch Checklist - 25 Must-Dos Before Going Live - ElementorMaher rahmanNo ratings yet

- ESM-xx53 Motorized Valve ControllerDocument4 pagesESM-xx53 Motorized Valve ControllerCristian SerbanoiuNo ratings yet

- Apple Watch SpecificationsDocument3 pagesApple Watch Specificationsalvipin001No ratings yet

- Complete Practice Quiz in Data Communications and NetworkingDocument2 pagesComplete Practice Quiz in Data Communications and NetworkingFaruk KhanNo ratings yet

- Availability Dependencies EN XXDocument213 pagesAvailability Dependencies EN XXraobporaveenNo ratings yet

- Python by WiproDocument48 pagesPython by WiproPratik SanasNo ratings yet

- TWS EAERBUDS Price List From HOPORA CompanyDocument15 pagesTWS EAERBUDS Price List From HOPORA CompanySindy JimenezNo ratings yet

- E LESF GRADE 3 07 14 20 2MALE 151 2FEMALE 131 Tunay EditedDocument282 pagesE LESF GRADE 3 07 14 20 2MALE 151 2FEMALE 131 Tunay EditedGervinBulataoNo ratings yet

- eRAN KPI Reference (V100R013C10 - 01) (PDF) - ENDocument98 pageseRAN KPI Reference (V100R013C10 - 01) (PDF) - ENTry Test100% (1)

- 112-07-005 Rev 1 - iSED Inter-Sample Carry Over Test ProtocolDocument4 pages112-07-005 Rev 1 - iSED Inter-Sample Carry Over Test ProtocolAmine CHAHIDNo ratings yet

- Security HackerDocument213 pagesSecurity HackerCath Tacis0% (1)

- DCIT104 Lecture 2Document56 pagesDCIT104 Lecture 2Muel OpokuNo ratings yet

- Chapter 4 Word Processor Mail MergeDocument2 pagesChapter 4 Word Processor Mail MergeBindu RaviNo ratings yet

- Manish Kumar Email Mob: - +919620132512: Areer BjectiveDocument4 pagesManish Kumar Email Mob: - +919620132512: Areer BjectiveRajeev TripathiNo ratings yet

- Dxdiag LumionDocument43 pagesDxdiag LumionMANUEL ALEJANDRO CELEITA GONZALEZNo ratings yet

- Advanced SQL Presentation TemplateDocument29 pagesAdvanced SQL Presentation Templateamit kumarNo ratings yet

- College Time Table Generation AbstractDocument5 pagesCollege Time Table Generation AbstractTelika Ramu100% (1)

- ICS 223: Transaction Processing and Distributed Data Management Winter 2011Document11 pagesICS 223: Transaction Processing and Distributed Data Management Winter 2011Reese FrasierNo ratings yet

- EDS Export: User's ManualDocument2 pagesEDS Export: User's ManualMinh Trieu NguyenNo ratings yet

- Polar Orbiter Ingester PDFDocument58 pagesPolar Orbiter Ingester PDFEduardo Luisenrique Sanchez CarrionNo ratings yet

- Troubleshooting FWSM PerformanceDocument2 pagesTroubleshooting FWSM PerformanceDinkar SharmaNo ratings yet

- Resume Vikas PhulriyaDocument3 pagesResume Vikas PhulriyaVikas PhulriyaNo ratings yet

- Resume: Sandeep BauraiDocument3 pagesResume: Sandeep BauraiSandeep BaudaiNo ratings yet

- The Definitive ANTLR 4 Reference: Extracted FromDocument11 pagesThe Definitive ANTLR 4 Reference: Extracted FromYao LiNo ratings yet

- B0700FCDocument176 pagesB0700FCfadhelNo ratings yet

- Keyboard Shortcuts in Evernote For Windows - Evernote Help & LearningDocument8 pagesKeyboard Shortcuts in Evernote For Windows - Evernote Help & LearningRahulNo ratings yet

- ECE522 Pre-Test1 SolutionsDocument11 pagesECE522 Pre-Test1 SolutionsJohnny Tagal100% (1)