Professional Documents

Culture Documents

412n - Unit I - Digital Design Automation

Uploaded by

Marc Neil ApasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

412n - Unit I - Digital Design Automation

Uploaded by

Marc Neil ApasCopyright:

Available Formats

UNIT I:

Digital System Design

Automation

CpE 425 Digital Systems Design 1

Unit Outline

● Design Concepts

● Design Process

● Abstraction Levels

● Introduction to FPGA

● Introduction to HDLs (VHDL and Verilog)

CpE 425 Digital Systems Design 2

Digital Concepts

CpE 425 Digital Systems Design 3

Digital Hardware

● Standard Chips

● Programmable Logic Devices

● Custom-Designed Chips

CpE 425 Digital Systems Design 4

The Design

Process

CpE 425 Digital Systems Design 5

Abstraction Levels

Level Components Representation

Behavioral Algorithms, FSMs Algorithmic representation of

system functions

System Processors, Interconnection of major

(architectural) memories, functional functional units

subsystems

Register Registers, adders, Data movement and

Transfer Level comparators, ALUs, transformation and required

(RTL/dataflow) counters, controllers, sequential control

bus

Gate (logic Logic gates, flip-flops Implementation of register

level) level components using gates

and flip-flops

Transistor Transistors, resistors, Implementation of gates and

(switch level) capacitors flip-flops using transistors,

capacitors, and resistors

CpE 425 Digital Systems Design 6

Software Aspects of Digital

Design

● In computer-aided design (CAD), various software tools

improve the designer’s productivity and help to improve the

correctness and quality of designs.

● Software tools:

– Schematic entry

– HDLs

– HDL compilers, simulators, and synthesis tools

– Simulators

– Test benches

– Timing analyzers and verifiers

CpE 425 Digital Systems Design 7

Design Methodology

● Uses HDL to describe the system being designed and the

testbench used to verify the design

● Uses a software compiler and simulator tool to simulate the

design to verify its functionality and timing

● Uses a software synthesis tool to create the logic described

● Uses a software place-and-route tool to map the synthesized

logic to the target PLD and to generate a timing model and a

configuration file (timing verification can also follow)

● Uses a PLD to physically implement the design

● Uses the information in configuration file to program the PLD

CpE 425 Digital Systems Design 8

FPGA

● 1985: Xilinx (Ross Freeman) introduced a completely

new idea:

– User control and time to market of PLDs

– Densities and cost benefit of gate arrays

● Field Programmable Gate Arrays

● FPGAs are programmable semiconductor devices that

are based around a matrix of configurable logic blocks

(CLBs) or logic cells connected via programmable

interconnects.

CpE 425 Digital Systems Design 9

General FPGA Configuration

CpE 425 Digital Systems Design 10

Two FPGA Types

● Two basic types:

– SRAM-based reprogrammable

– One Time Programmable (OTP)

● The two types differ in the implementation of the logic

cell and the mechanism used to make connections in

the device.

CpE 425 Digital Systems Design 11

Two FPGA Types

SRAM-based OTP

Programmable

CpE 425 Digital Systems Design 12

FPGAs vs. CPLDs

FPGAs CPLDs

● Fine-grain devices ● Coarse-grain devices

– Contains a lot (up to 100,000) of – Contains relatively few (a few

tiny blocks of logic with flip-flops

100's max) large blocks of

● RAM-based logic with flip-flops

● Have special routing resources to ● EEPROM-based

implement efficiently arithmetic

functions

● Faster input-to-output timings

– Binary counters, adders, – Better suited for

comparators, etc. microprocessor decoding logic

● Can contain large digital designs ● Can contain small designs only

CpE 425 Digital Systems Design 13

FPGAs vs. Microcontrollers

FPGAs Microcontrollers

● Implement programmable ● Are based on a CPU

logic elements running in a architecture (executes a set of

parallel fashion instructions in a sequential

manner)

●

● More configurable

● Have on-chip peripherals that

also execute in parallel with

their CPU

CpE 425 Digital Systems Design 14

HDLs

● A hardware description language (HDL) is similar to a

typical computer programming language except that an

HDL is used to describe hardware rather than a program to

be executed on a computer.

● Institute of Electrical and Electronics Engineers (IEEE)

standard HDLs:

– VHDL

– Verilog HDL

CpE 425 Digital Systems Design 15

HDLs

● The complexity of ASIC and FPGA designs has meant an

increase in the number of specific tools and libraries of

macro and mega cells written in either VHDL or Verilog.

● As a result, it is important that designers know both VHDL

and Verilog and that EDA tools vendors provide tools that

provide an environment allowing both languages to be used

in unison.

CpE 425 Digital Systems Design 16

HDLs

● VHDL (Very high speed integrated circuit Hardware Description

Language) became IEEE standard 1076 in 1987.

● The Verilog hardware description language has been used far

longer than VHDL and has been used extensively since it was

launched by Gateway in 1983.

● Cadence bought Gateway in 1989 and opened Verilog to the

public domain in 1990.

● Verilog became IEEE standard 1364 in December 1995.

CpE 425 Digital Systems Design 17

VHDL and Verilog

in Comparison

CpE 425 Digital Systems Design 18

Capability

● VHDL – like Pascal or Ada programming languages

● Verilog – like C programming language

● It is important to remember that both are Hardware

Description Languages and not programming languages

● For synthesis, only a subset of languages is used.

CpE 425 Digital Systems Design 19

Capability

● Hardware structure can be modeled equally effectively in both VHDL

and Verilog.

● When modeling abstract hardware, the capability of VHDL can

sometimes only be achieved in Verilog when using the Programming

Language Interface (PLI).

● The choice of which to use is not therefore based solely on technical

capability but on:

– personal preferences

– EDA tool availability

– commercial, business and marketing issues

CpE 425 Digital Systems Design 20

Capability

● The modeling constructs of VHDL and Verilog cover a

slightly different spectrum across the levels of behavioral

abstraction.

CpE 425 Digital Systems Design 21

Compilation

● VHDL:

– Multiple design-units (entity/architecture pairs), that reside in

the same system file, may be separately compiled if so

desired.

– It is good design practice to keep each design unit in it's own

system file in which case separate compilation should not be

an issue.

CpE 425 Digital Systems Design 22

Compilation

● Verilog:

– The Verilog language is still rooted in it's native interpretative

mode.

– Compilation is a means of speeding up simulation, but has not

changed the original nature of the language.

– The care must be taken with both the compilation order of code

written in a single file and the compilation order of multiple files.

– Simulation results can change by simply changing the order of

compilation.

CpE 425 Digital Systems Design 23

Data Types

● VHDL:

– A multitude of language or user defined data types can be used.

– This may mean dedicated conversion functions are needed to

convert objects from one type to another.

– The choice of which data types to use should be considered

wisely, especially enumerated (abstract) data types.

– VHDL may be preferred because it allows a multitude of language

or user defined data types to be used.

CpE 425 Digital Systems Design 24

Data Types

● Verilog:

– Compared to VHDL, Verilog data types a very simple, easy to use

and very much geared towards modeling hardware structure as

opposed to abstract hardware modeling.

– Unlike VHDL, all data types used in a Verilog model are defined by

the Verilog language and not by the user.

– There are net data types, for example wire, and a register data type

called reg.

– Verilog may be preferred because of its simplicity.

CpE 425 Digital Systems Design 25

Design Reusability

● VHDL:

– Procedures and functions may be placed in a package so that

they are available to any design-unit that wishes to use them.

● Verilog:

– There is no concept of packages in Verilog.

– Functions and procedures used within a model must be defined in

the module.

– To make functions and procedures generally accessible from

different module statements the functions and procedures must

be placed in a separate system file and included using the

`include compiler directive.

CpE 425 Digital Systems Design 26

Ease of Learning

● Starting with zero knowledge of either language, Verilog is

probably the easiest to grasp and understand.

● VHDL may seem less intuitive at first for two primary

reasons:

– First, it is very strongly typed; a feature that makes it robust

and powerful for the advanced user after a longer learning

phase.

– Second, there are many ways to model the same circuit,

specially those with large hierarchical structures

CpE 425 Digital Systems Design 27

High Level Constructs

● VHDL:

– There are more constructs and features for high-level modeling

in VHDL than there are in Verilog.

– Abstract data types can be used along with the following

statements:

● package statements for model reuse,

● configuration statements for configuring design structure,

● generate statements for replicating structure,

● generic statements for generic models that can be

individually characterized, for example, bit width.

– All these language statements are useful in synthesizable

models.

CpE 425 Digital Systems Design 28

High Level Constructs

● Verilog:

– Except for being able to parameterize models by overloading

parameter constants, there is no equivalent to the high-level

VHDL modeling statements in Verilog.

CpE 425 Digital Systems Design 29

Libraries

● VHDL:

– A library is a store for compiled entities, architectures,

packages and configurations. Useful for managing multiple

design projects.

● Verilog:

– There is no concept of a library in Verilog. This is due to it's

origins as an interpretive language.

CpE 425 Digital Systems Design 30

Low Level Constructs

● VHDL:

– Simple two input logical operators are built into the language:

NOT, AND, OR, NAND, NOR, XOR, and XNOR.

– Any timing must be separately specified using the after

clause.

– Separate constructs defined under the VITAL language must

be used to define the cell primitives of ASIC and FPGA

libraries.

CpE 425 Digital Systems Design 31

Low Level Constructs

● Verilog:

– The Verilog language was originally developed with gate level

modeling in mind, and so has very good constructs for

modeling at this level and for modeling the cell primitives of

ASIC and FPGA libraries.

– Examples include User Defined Primitives (UDP), truth tables

and the specify block for specifying timing delays across a

module.

CpE 425 Digital Systems Design 32

Managing Large Designs

● VHDL:

– Configuration, generate, generic and package statements all

help manage large design structures.

● Verilog:

– There are no statements in Verilog that help manage large

designs.

CpE 425 Digital Systems Design 33

Operators

● The majority of operators are the same between the two

languages.

● Verilog does have very useful unary reduction operators

that are not in VHDL.

● A loop statement can be used in VHDL to perform the same

operation as a Verilog unary reduction operator.

● VHDL has the mod operator that is not found in Verilog.

CpE 425 Digital Systems Design 34

Procedures and Tasks

● VHDL:

– Concurrent procedure calls are allowed.

● Verilog:

– Concurrent procedure calls are not allowed

CpE 425 Digital Systems Design 35

Readability

● This is more a matter of coding style and experience than

language feature.

– VHDL is a concise and verbose language;

– Verilog is more like C because it's constructs are based

approximately 50% on C and 50% on Ada.

● For this reason an existing C programmer may prefer Verilog

over VHDL.

● Whatever HDL is used, when writing or reading an HDL model to

be synthesized, it is important to think about hardware intent.

CpE 425 Digital Systems Design 36

Structural Replication

● VHDL:

– The generate statement replicates a number of instances of

the same design-unit or some sub part of a design, and

connects it appropriately.

● Verilog:

– There is no equivalent to the generate statement in Verilog.

CpE 425 Digital Systems Design 37

Verboseness

● VHDL:

– Because VHDL is a very strongly typed language, models

must be coded precisely with defined and matching data

types.

– This may be considered an advantage or disadvantage.

– It does mean models are often more verbose, and the code

often longer, than it's Verilog equivalent.

CpE 425 Digital Systems Design 38

Verboseness

● Verilog:

– Signals representing objects of different bits widths may be assigned to

each other.

– The signal representing the smaller number of bits is automatically padded

out to that of the larger number of bits, and is independent of whether it is

the assigned signal or not.

– Unused bits will be automatically optimized away during the synthesis

process.

– This has the advantage of not needing to model quite so explicitly as in

VHDL, but does mean unintended modeling errors will not be identified by

an analyzer.

CpE 425 Digital Systems Design 39

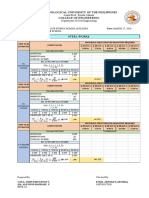

Summary

CpE 425 Digital Systems Design 40

Summary

CpE 425 Digital Systems Design 41

Summary

CpE 425 Digital Systems Design 42

Summary

CpE 425 Digital Systems Design 43

References

● Douglas J. Smith, “VHDL & Verilog Compared & Contrasted

Plus Modeled Example Written in VHDL, Verilog and C”

● www.ue.pwr.wroc.pl/pld/pld_12.pdf

● www.asic-world.com

● http://www.ece.umd.edu/courses/enee359a/verilog_tutorial.

CpE 425 Digital Systems Design 44

You might also like

- Lab 1Document41 pagesLab 1J JAYDON100% (1)

- 1 Introduction To VHDL 1Document26 pages1 Introduction To VHDL 1R Venkat Kalyan NaikNo ratings yet

- Introuction To DSD With VHDLDocument19 pagesIntrouction To DSD With VHDLAssini HussainNo ratings yet

- Cadence Design Flows: Mike Cooney Idlab Feb. 18, 2010Document18 pagesCadence Design Flows: Mike Cooney Idlab Feb. 18, 2010Ahmed EdrisNo ratings yet

- Design Methods: Verilog HDL VHDLDocument6 pagesDesign Methods: Verilog HDL VHDLNiranjan BeheraNo ratings yet

- VlsipythonDocument4 pagesVlsipythonsiri.pogulaNo ratings yet

- The Custom Designer Ecosystem at Synopsys: October 2009Document23 pagesThe Custom Designer Ecosystem at Synopsys: October 2009monikaNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Design Representation VHDL: Henok TDocument51 pagesDesign Representation VHDL: Henok TNuhamin BirhanuNo ratings yet

- Definition:: Field-Programmable Gate ArrayDocument6 pagesDefinition:: Field-Programmable Gate ArrayyaduyadavendraNo ratings yet

- PYNQ Productivity With PythonDocument67 pagesPYNQ Productivity With PythonDr. Dipti KhurgeNo ratings yet

- Digital Filters in Programmable Logic DevicesDocument13 pagesDigital Filters in Programmable Logic DevicesJoerg MenkeNo ratings yet

- Lec 1 (Introduction HDL, VHDL, FPGA)Document35 pagesLec 1 (Introduction HDL, VHDL, FPGA)eslam MohamedNo ratings yet

- Fpga VHDLDocument19 pagesFpga VHDLAshraf maghNo ratings yet

- Manual SelfDocument133 pagesManual Selfchiranjeevee02No ratings yet

- 02.-Introduction VHDL ProgrammingDocument71 pages02.-Introduction VHDL ProgrammingFarias Ben JaNo ratings yet

- EE382N-4 Advanced Microcontroller Systems: Accelerators and Co-ProcessorsDocument75 pagesEE382N-4 Advanced Microcontroller Systems: Accelerators and Co-ProcessorshilgadNo ratings yet

- VHDL Slide Nectec PDFDocument162 pagesVHDL Slide Nectec PDFภัทรชัย โรจนนาคNo ratings yet

- Hardware Description Languages and Programmable LogicDocument30 pagesHardware Description Languages and Programmable LogicJay UlomiNo ratings yet

- Carrera de Ingeniería Electrónica Arquitectura de ComputadoresDocument15 pagesCarrera de Ingeniería Electrónica Arquitectura de ComputadoresMario Sebastian Rubio ToroNo ratings yet

- Implementation of Uart Using Systemc and Fpga Based Co-Design MethodologyDocument7 pagesImplementation of Uart Using Systemc and Fpga Based Co-Design MethodologyRakeshconclaveNo ratings yet

- Tutorial 1Document3 pagesTutorial 1Xzk KhooiNo ratings yet

- Codesys eDocument1 pageCodesys eMrSarvanNo ratings yet

- Is A FPGA A CPUDocument9 pagesIs A FPGA A CPUjackNo ratings yet

- Unit I Embedded SystemDocument42 pagesUnit I Embedded Systemkarthick707No ratings yet

- Hardware Modelling Using VerilogDocument15 pagesHardware Modelling Using VerilogYogesh Tiwari25% (4)

- VHDL NotesDocument40 pagesVHDL Notesangel_hunNo ratings yet

- Implementation of Serial Communication IP For Soc ApplicationsDocument4 pagesImplementation of Serial Communication IP For Soc ApplicationsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Altera Enixs Course PDFDocument3 pagesAltera Enixs Course PDFLe LamNo ratings yet

- Embedded Systems Unit I Part A (2 Marks)Document47 pagesEmbedded Systems Unit I Part A (2 Marks)Vijaya KumarNo ratings yet

- Introduction To HDLDocument28 pagesIntroduction To HDLBack UpNo ratings yet

- Unit-5 System Level Design Using Mentor Graphics EDA Tool (FPGA Advantage)Document12 pagesUnit-5 System Level Design Using Mentor Graphics EDA Tool (FPGA Advantage)kumarkankipati19No ratings yet

- VHDLDocument50 pagesVHDLJayant JamwalNo ratings yet

- Module 4A HDL Intro 04-12-23Document15 pagesModule 4A HDL Intro 04-12-23raovinayakm2No ratings yet

- Vlsi Cad Tools: Slides Courtesy of Deming Chen, LeslieDocument50 pagesVlsi Cad Tools: Slides Courtesy of Deming Chen, LeslieAsShabNo ratings yet

- DSP Lab ManualDocument169 pagesDSP Lab Manualapi-26783388100% (2)

- 2.VLSI Design Using Verilog HDL 2.1 Explain The Steps Involved in The Design Flow For The VLSI IC Design: Typical Design FlowDocument21 pages2.VLSI Design Using Verilog HDL 2.1 Explain The Steps Involved in The Design Flow For The VLSI IC Design: Typical Design FlowDinesh PalavalasaNo ratings yet

- Digital Design Using Verilog HDL: Fall 21Document39 pagesDigital Design Using Verilog HDL: Fall 21ifireNo ratings yet

- Unit 01 (2nd Part)Document50 pagesUnit 01 (2nd Part)Udbhav PachisiaNo ratings yet

- Verilog Chapter1 IntroductionDocument32 pagesVerilog Chapter1 Introductionka jonhNo ratings yet

- Tutorial On Transaction Level Modeling With Systemc For System Level DesignDocument151 pagesTutorial On Transaction Level Modeling With Systemc For System Level Designramsampath78No ratings yet

- Types of Modelling PDFDocument14 pagesTypes of Modelling PDFAnonymous 3XeTp7drNo ratings yet

- Introduction To FPGADocument16 pagesIntroduction To FPGAapi-19457371100% (1)

- 18EC56 - Suryakanth B.MDocument76 pages18EC56 - Suryakanth B.M1am17ec014 ashnal ahmedNo ratings yet

- 08.546 DSD With VHDL Lecture Notes - Module 1Document70 pages08.546 DSD With VHDL Lecture Notes - Module 1Assini Hussain100% (1)

- 8 Bit ALU by XilinxDocument16 pages8 Bit ALU by XilinxDIPTANU MAJUMDERNo ratings yet

- Module 1 PDFDocument15 pagesModule 1 PDFShivu KNo ratings yet

- Fpga: Digital Designs: Team Name:Digital DreamersDocument8 pagesFpga: Digital Designs: Team Name:Digital DreamersRishabhNo ratings yet

- Ijert: 32-Bit Risc Processor For Computer ArchitectureDocument6 pagesIjert: 32-Bit Risc Processor For Computer ArchitectureTàiLươngNo ratings yet

- 1-Introduction 1.0 Motivation: Which Is Like A"blueprint" For Building The Machine)Document63 pages1-Introduction 1.0 Motivation: Which Is Like A"blueprint" For Building The Machine)Manikanta Raja MedapatiNo ratings yet

- VHDL GuideDocument30 pagesVHDL Guidelxz5101No ratings yet

- CME 4456 Reconfigurable Computing: Şerife YILMAZDocument72 pagesCME 4456 Reconfigurable Computing: Şerife YILMAZB. TNo ratings yet

- Basics VHDLLabDocument266 pagesBasics VHDLLabBasma GamalNo ratings yet

- Verilog CourseDocument181 pagesVerilog Coursemanya mehtaNo ratings yet

- pn0010676 2Document2 pagespn0010676 2Elangovan SekarNo ratings yet

- Introduction To System On ChipDocument110 pagesIntroduction To System On ChipKhNo ratings yet

- Embedded Systems Design with Platform FPGAs: Principles and PracticesFrom EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesRating: 5 out of 5 stars5/5 (1)

- Software Engineering for Embedded Systems: Methods, Practical Techniques, and ApplicationsFrom EverandSoftware Engineering for Embedded Systems: Methods, Practical Techniques, and ApplicationsRating: 2.5 out of 5 stars2.5/5 (2)

- "Unleashing the Power of Assembly Language: Mastering the World's Most Efficient Code"From Everand"Unleashing the Power of Assembly Language: Mastering the World's Most Efficient Code"No ratings yet

- Practical Programmable Circuits: A Guide to PLDs, State Machines, and MicrocontrollersFrom EverandPractical Programmable Circuits: A Guide to PLDs, State Machines, and MicrocontrollersNo ratings yet

- 3 Intro+to+MB90F387S PDFDocument29 pages3 Intro+to+MB90F387S PDFMarc Neil ApasNo ratings yet

- 5 Interfacing+LCD+with+MB90F387S PDFDocument40 pages5 Interfacing+LCD+with+MB90F387S PDFMarc Neil ApasNo ratings yet

- MCU Architecture & Programming: An IntroductionDocument26 pagesMCU Architecture & Programming: An IntroductionMarc Neil ApasNo ratings yet

- Interfacing Numeric Keypad With MB90F387SDocument18 pagesInterfacing Numeric Keypad With MB90F387SMark VillamorNo ratings yet

- 412n - Unit III - Behavioral ModelingDocument26 pages412n - Unit III - Behavioral ModelingMarc Neil ApasNo ratings yet

- 4 MB90F387S+IO+Configuration PDFDocument28 pages4 MB90F387S+IO+Configuration PDFMarc Neil ApasNo ratings yet

- 7 Interfacing+Stepper+Motor+with+MB90F387SDocument28 pages7 Interfacing+Stepper+Motor+with+MB90F387SMarc Neil ApasNo ratings yet

- 1 Intro+to+Embedded+Systems PDFDocument38 pages1 Intro+to+Embedded+Systems PDFMarc Neil ApasNo ratings yet

- 412n - Unit IV - Modeling of Sequential CircuitsDocument19 pages412n - Unit IV - Modeling of Sequential CircuitsMarc Neil ApasNo ratings yet

- APAS - Written Report - Windows Vs Unix (I - O and File Management)Document4 pagesAPAS - Written Report - Windows Vs Unix (I - O and File Management)Marc Neil Apas100% (2)

- Unit II - Structural and Gate Level ModelingDocument18 pagesUnit II - Structural and Gate Level ModelingFrancesNo ratings yet

- RibaDocument1 pageRibaMohamed KhalidNo ratings yet

- اﻹبتكار واﻹبداع في قطاع المقاولات - دراسة التجربة الوطنية و تجارب دولية رائدةDocument17 pagesاﻹبتكار واﻹبداع في قطاع المقاولات - دراسة التجربة الوطنية و تجارب دولية رائدةkhadeejah.yasserNo ratings yet

- Geethanjali: Department of Mechanical EngineeringDocument43 pagesGeethanjali: Department of Mechanical EngineeringMalkapuram DevaiahNo ratings yet

- SWE2004 - Software Design and ArchitectureDocument20 pagesSWE2004 - Software Design and ArchitecturePradhyumna GundaNo ratings yet

- A Better Choice Among Cad-Cam Systems For FootwearDocument3 pagesA Better Choice Among Cad-Cam Systems For FootwearMihaiNo ratings yet

- Design For Real PeopleDocument48 pagesDesign For Real PeoplekishoreuxNo ratings yet

- Delhi Architects - List of Architects in DelhiDocument96 pagesDelhi Architects - List of Architects in Delhiru4angelNo ratings yet

- Conceptualisation To MaterialisationDocument52 pagesConceptualisation To MaterialisationPrajakta GhatgeNo ratings yet

- AR - 513 Thesis Design - I: Dr. Yusuf AwanDocument8 pagesAR - 513 Thesis Design - I: Dr. Yusuf AwanSadia SamiNo ratings yet

- Price List TbossDocument6 pagesPrice List TbossAdi YugoNo ratings yet

- Subject OutlineDocument6 pagesSubject OutlineRazat SiwakotiNo ratings yet

- SyallabusDocument48 pagesSyallabusAbhijeet DhavaleNo ratings yet

- Henok Shiferaw BestDocument156 pagesHenok Shiferaw BestabrhamNo ratings yet

- Canny AntiguoDocument178 pagesCanny Antiguoguillermo Bueno100% (1)

- The Database Development Life CycleDocument24 pagesThe Database Development Life CycleLuis ForniNo ratings yet

- SchneiderDocument331 pagesSchneiderAngelo AmayNo ratings yet

- Wepik Le Corbusier The Revolutionary Architect of Modernism 20231026135446Prp2Document11 pagesWepik Le Corbusier The Revolutionary Architect of Modernism 20231026135446Prp2rdmalviya07No ratings yet

- Survey Kepemilikan Laptop - Notebook (168 Mahasiswa)Document10 pagesSurvey Kepemilikan Laptop - Notebook (168 Mahasiswa)Anastasya SaragihNo ratings yet

- PDMS HVAC Design FeaturesDocument1 pagePDMS HVAC Design FeaturesPrasadNo ratings yet

- Dr. Dennis E. Becker - Testing in Geotechnical Design-SEAGS AGSSEA Journal 2010 PDFDocument12 pagesDr. Dennis E. Becker - Testing in Geotechnical Design-SEAGS AGSSEA Journal 2010 PDFthanhtrung87No ratings yet

- Export To PDMS User's GuideDocument3 pagesExport To PDMS User's GuidelnacerNo ratings yet

- Math Trails: Meaningful Mathematics Outside The Classroom With Pre-Service TeachersDocument11 pagesMath Trails: Meaningful Mathematics Outside The Classroom With Pre-Service TeachersMinus0No ratings yet

- NX Tooling Brochure W 1 - tcm642-4494 PDFDocument16 pagesNX Tooling Brochure W 1 - tcm642-4494 PDFvijayNo ratings yet

- The Language of School Design Design Patterns For 21st CenturyDocument5 pagesThe Language of School Design Design Patterns For 21st CenturyHamad Habad0% (1)

- EMT3701 Tut Letter 2021Document9 pagesEMT3701 Tut Letter 2021Zinhle NobahleNo ratings yet

- Current Steering Circuits: V R I V V V R R RDocument3 pagesCurrent Steering Circuits: V R I V V V R R RjaberyemeniNo ratings yet

- Healing Gardens' Design: Dr. Hesham El BarmelgyDocument20 pagesHealing Gardens' Design: Dr. Hesham El BarmelgyMohd SalahuddinNo ratings yet

- 5 Steel Works Columns CompuDocument22 pages5 Steel Works Columns CompuALFONSO RAPHAEL SIANo ratings yet

- Skripsi Nurwahida (1) - Addie PDFDocument265 pagesSkripsi Nurwahida (1) - Addie PDFBondan SetiawanNo ratings yet

- The ChemCollective-Virtual LabsDocument2 pagesThe ChemCollective-Virtual LabsRikta SahaNo ratings yet