Professional Documents

Culture Documents

01 Introduccion

Uploaded by

Flakita S MelcOchitaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

01 Introduccion

Uploaded by

Flakita S MelcOchitaCopyright:

Available Formats

Escuela Politécnica Nacional. Vinueza, Miranda. Lab. Sist. Digitales.

OPERACIONES ARITMÉTICAS BINARIAS

(VHDL)

Julio Cesar Miranda Carrasco, Yaritza Salome Vinueza Cuestas

Laboratorio de Sistemas Digitales, Departamento de Electrónica, Telecomunicaciones y Redes de Información

Escuela Politécnica Nacional

Quito, Ecuador

yaritza.vinueza@epn.edu.ec, julio.miranda01@epn.edu.ec

Abstract— En el presente trabajo se indican algunos Restador_tb.vhd

ejemplos prácticos del uso de VHDL para representar las

compuertas básicas aplicando la sintaxis de cada elemento en el

programa.

I. INFORME

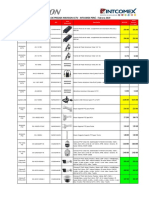

A. Diseñar y Simular un restador de tres bits usando la

VHDL, presente el resultado mediante un display, y un led

que indique el signo (apagado positivo, prendido negativo).

Presente el código desarrollado y la simulación en Proteus.

Consultar sobre al menos 10 aplicaciones de VHDL en la

industria.

B

1

U7 U8 U9

NOT NOT NOT

1

A

13

16

10

11

4

7

1

3

8

U1

C0

B4

B3

B2

B1

A4

A3

A2

A1

0

1

1

7483

C4

S4

S3

S2

S1

14

15

2

6

9

13

16

10

11

4

7

1

3

8

U3

C0

B4

B3

B2

B1

A4

A3

A2

A1

7483

1

C4

S4

S3

S2

S1

U2:A

14

15

2

6

9

1 U5

3 10 9 U10

A1 S1

2 8 6 7 13

U2:B A2 S2 A QA

3 2 1 12

A3 S3 B QB

5 4077 1 15 2 11

A4 S4 C QC

4 6 10

D QD

6 11 4 9

U2:C B1 BI/RBO QE

7 5 15

8 4077 4

B2

B3

1 3

RBI

LT

QF

QG

14

10 16

B4

9 7447

13 14

C0 C4

4077

7483

U4

NOT

D1

LED-BLUE D1=Signo(0-Positivo; 1-Negativo)

B. Diseñar y Simular un comparador de magnitud entre dos

Fig [1]. Simulacion del restador.

A y B números de 4 bits usando VHDL. El circuito dispondrá

de dos salidas, que harán que se prenda un led verde (salida

Restador.vhd 1) en Caso de que A sea mayor que B, mientras que se prenda

un led rojo (salida 2) en caso de que B sea mayor que A. Caso

que los números sean iguales, los dos leds deberán

permanecer apagados. Presente el código desarrollado y la

simulación en Proteus.

Escuela Politécnica Nacional. Vinueza, Miranda. Lab. Sist. Digitales. 2

Fig [3]. Simulacion de estados.

Fig [2]. Simulacion de comparador.

C. Implementar las siguientes funciones Booleanas usando

CODIGO VHDL COMPARADOR

VHDL

library ieee;

use ieee.std_logic_1164.all;

entity compuerta_comparador is

port ( Presente el código desarrollado

entrada1: in std_logic_vector (3 downto 0);

entrada2: in std_logic_vector (3 downto 0); F=MoM2M4

Mayor: out std_logic_vector (3 downto 0);

Menor: out std_logic_vector (3 downto 0);

Funcion024.vhd

Igual: out std_logic_vector (3 downto 0));

library ieee;

end compuerta_comparador;

use ieee.std_logic_1164.all;

architecture Behavioral of compuerta_comparador is

begin

Mayor <= entrada1 when (entrada1 > entrada2) else entity funcion024 is

entrada2; port(

Menor <= entrada2 when (entrada1 < entrada2) else a: in std_ulogic;

entrada1; b: in std_ulogic;

Igual <= entrada2 when (entrada1 = entrada2) else "0000"; c: in std_ulogic;

end Behavioral; x: out std_ulogic

library ieee; );

use ieee.std_logic_1164.all; end funcion024;

entity compuerta_comparador_tb is

end compuerta_comparador_tb; architecture behave of funcion024 is

architecture test of compuerta_comparador_tb is begin

component compuerta_comparador x <= (a or c)and((not a)or(b)or(c));

port ( end behave;

entrada1: in std_logic_vector (3 downto 0);

entrada2: in std_logic_vector (3 downto 0); Funcion024_tb.vhd

Mayor: out std_logic_vector (3 downto 0);

Menor: out std_logic_vector (3 downto 0); library ieee;

Igual: out std_logic_vector (3 downto 0));

use ieee.std_logic_1164.all;

end component;

signal a, b, m, n, i: std_logic_vector (3 downto 0);

entity funcion024_tb is

begin

DUT: compuerta_comparador port map ( entrada1 => a,

entrada2=> b, Mayor=> m, Menor=>n, Igual=>i ); end funcion024_tb;

process begin

a<= "0001"; architecture test of funcion024_tb is

b<= "0011"; component funcion024

wait for 4 ns; port(

assert false report "Comprobacion"; a: in std_ulogic;

wait; b: in std_ulogic;

end process; c: in std_ulogic;

end test; x: out std_ulogic

);

Escuela Politécnica Nacional. Vinueza, Miranda. Lab. Sist. Digitales. 3

end component; • Al usar el lenguaje de programación de VHDL, se esta

signal a, b, c, x : std_ulogic; reduciendo el gasto en materiales para armar el

begin circuito, ya que el código será ejecutado en un

funcion024test: funcion024 port elemento que ya tiene muchos de los componentes

map (a => a, b => b, c => c, x => x); usados en anteriores prácticas, sin las falencias de

process begin fábrica.

a <= 'X'; Salome Vinueza

b <= 'X';

c <= 'X'; • Comprobamos que con la ayuda de VHDL podemos

wait for 10 fs; también simular el comportamiento de nuestro circuito

lógico sin necesidad de armarlo físicamente.

a <= '0'; • Comprobamos la utilidad de VHDL para crear

b <= '0';

componentes de circuitos más complejos a cualquier

c <= '0';

wait for 10 fs; escala.

• Se comprobó que la implementación de algunos

assert false report circuitos es mejor realizarlos con un simulador como

"Reached end of test"; Proteus, ya que nos evitan la necesidad de escribir

wait; largos códigos para obtener simulaciones de circuitos

end process; integrados.

end test;

III. RECOMENDACIONES

Cesar Miranda

F=m1+m2+m5+m7

• Tener conocimiento de las secuencias básicas de

library ieee use ieee.std_logic_1164.all; VHDL.

use ieee.std_logic_arith.all; • Tener en cuenta las pequeñas diferencias que tiene

use ieee.std_logic_unsigned.all; VHDL con otros lenguajes de programación.

entity minterminos is

port ( Salome Vinueza

A : in std_logic; • Debemos siempre revisar que la sintaxis sea correcta

B :in std_logic; • Se debe utilizar librerías estándar para la simulación

C :in std_logic; var : de componentes en VHDL

out std_logic • Utilizar buenas normas de programación para la

); escritura de nuestro código y así hacerlo más

end minterminos; comprensible al momento de que alguien más lo

architecture Behavioral of minterminos is revise.

signal s1: std_logic;

signal s2: std_logic;

signal s3: std_logic;

begin IV. REFERENCIAS

s1 <= not B and A;

s2 <= (not C) and B and not A;

s3 <= C and A; var <= s1 or s2 or s3; end [1] C. Novillo Montero, «Repositorio Digital - EPN,» 2008.

Behavioral; [En línea]. Available:

http://bibdigital.epn.edu.ec/handle/15000/4829. [Último

acceso: 03 12 2017].

II. CONCLUSIONES [2] R. J. N. S. W. G. L. M. TOCCI, «Sistemas digitales,

Cesar Miranda Principios y Aplicaciones,» Mexico, Pearson Educacion,

2007, p. 84.

• El código VHDL nos permite simular el

funcionamiento de algunos elementos de sistemas

digitales, mediante la programación del

comportamiento de los mismo, con su funcionamiento

de caja negra y arquitectura.

You might also like

- Comparacion Modelos Lineal No Lineal PDFDocument7 pagesComparacion Modelos Lineal No Lineal PDFFlakita S MelcOchitaNo ratings yet

- Informe1 CamaroneraDocument9 pagesInforme1 CamaroneraFlakita S MelcOchitaNo ratings yet

- Solicitud Gira UnileverDocument3 pagesSolicitud Gira UnileverFlakita S MelcOchitaNo ratings yet

- Informe 9 DigitalesDocument5 pagesInforme 9 DigitalesFlakita S MelcOchitaNo ratings yet

- Informe 3Document7 pagesInforme 3Flakita S MelcOchitaNo ratings yet

- Estudio Legal ProyectoDocument11 pagesEstudio Legal ProyectoFlakita S MelcOchitaNo ratings yet

- Polarización Del FET en DCDocument3 pagesPolarización Del FET en DCFlakita S MelcOchitaNo ratings yet

- Preparatorio 3Document14 pagesPreparatorio 3Flakita S MelcOchita100% (1)

- Switch CursoDocument28 pagesSwitch CursoalvezhNo ratings yet

- Actividad 2Document5 pagesActividad 2CRISNo ratings yet

- Memorias Ram-DesktopDocument1 pageMemorias Ram-DesktopEncontre ElrepuestoNo ratings yet

- TP 1 Redes Ceroleni-Mariño-SfiligoyDocument22 pagesTP 1 Redes Ceroleni-Mariño-SfiligoyNatalia SfiligoyNo ratings yet

- Practica1vozsobreipDocument10 pagesPractica1vozsobreipYENI JULIETH FUQUEN FUQUENENo ratings yet

- CNv6 instructorPPT Chapter2 PDFDocument32 pagesCNv6 instructorPPT Chapter2 PDFAriel Felipe Gomez RozoNo ratings yet

- Comando ICND1Document4 pagesComando ICND1anon_408008473No ratings yet

- Tarea de IPV4 GR IIDocument2 pagesTarea de IPV4 GR IIKatherine BorjasNo ratings yet

- SITE SURVEY - CLARO - Ecopetrol - ENCLOSTER #3Document17 pagesSITE SURVEY - CLARO - Ecopetrol - ENCLOSTER #3Jhon Jairo Serna MosqueraNo ratings yet

- Tarea1 1bimDocument12 pagesTarea1 1bimCarina MuñozNo ratings yet

- Lista de Precios Hikvision Accesorios Febrero 2019Document6 pagesLista de Precios Hikvision Accesorios Febrero 2019JesusMatheusMatiuU'No ratings yet

- Chuleta de DTDDocument2 pagesChuleta de DTDMaese MorcyNo ratings yet

- RETDocument4 pagesRETSsh Redes TecnologiaNo ratings yet

- Curso: Ccna 7.0 Introduction To NetworksDocument4 pagesCurso: Ccna 7.0 Introduction To NetworksHarold Gaspar RojasNo ratings yet

- Capitulo 2 Escalamiento de VlamDocument15 pagesCapitulo 2 Escalamiento de VlamEmil Eduardo Noesi LaraNo ratings yet

- Apoyo Milo PDFDocument140 pagesApoyo Milo PDFLupe MuñozNo ratings yet

- 8 Multi Protocolé Encapsulation (MPE) - RevDocument5 pages8 Multi Protocolé Encapsulation (MPE) - RevramonrramonezNo ratings yet

- Mtcna v22 05 WirelessDocument41 pagesMtcna v22 05 WirelessAlejandro Javier BerardiNo ratings yet

- Practica 3Document2 pagesPractica 3Fabian Silva EscobarNo ratings yet

- 10.1.2.5 Lab - Configure CDP and LLDPDocument19 pages10.1.2.5 Lab - Configure CDP and LLDPDIEGO GUALOCHICO100% (1)

- Tarea 4 - MODELO TCP IPDocument8 pagesTarea 4 - MODELO TCP IPPavelSaavedraNo ratings yet

- Practica 03Document0 pagesPractica 03Fernando RuizNo ratings yet

- Investigacion - Unidad 4 TelecomunicacionesDocument15 pagesInvestigacion - Unidad 4 Telecomunicacionesjuan pabloNo ratings yet

- Mapa Conceptual de Las Organismos de Estandarizacion de RedesDocument1 pageMapa Conceptual de Las Organismos de Estandarizacion de Redesplanetsatdocument100% (1)

- Foundation HseDocument46 pagesFoundation Hsereplapi100% (1)

- Ripv 3Document13 pagesRipv 3Sergio Carlos VillazanaNo ratings yet

- 8.4.1.1 Class Activity - Stepping Through OSPFv3 InstructionsDocument4 pages8.4.1.1 Class Activity - Stepping Through OSPFv3 InstructionsErid RocaNo ratings yet

- Controladora y Protocolos SOYALDocument28 pagesControladora y Protocolos SOYALRey Delnorte100% (1)

- Temario Ipasolink 200+TEDocument3 pagesTemario Ipasolink 200+TEJavier DávilaNo ratings yet

- Proceso de Configuración de ACL PDFDocument12 pagesProceso de Configuración de ACL PDFleonel sanchezNo ratings yet