Professional Documents

Culture Documents

Matrices y Vectores

Uploaded by

Jefry Gonzalez0 ratings0% found this document useful (0 votes)

9 views2 pagesasdksjdkfamsd

Copyright

© © All Rights Reserved

Available Formats

TXT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentasdksjdkfamsd

Copyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

9 views2 pagesMatrices y Vectores

Uploaded by

Jefry Gonzalezasdksjdkfamsd

Copyright:

© All Rights Reserved

Available Formats

Download as TXT, PDF, TXT or read online from Scribd

You are on page 1of 2

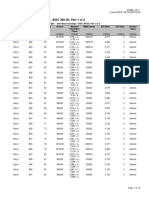

signal b00: std_logic_vector(9 downto 0):= "0000000000";

signal b01: std_logic_vector(9 downto 0):= "1111111111";

signal b02: std_logic_vector(9 downto 0):= "1000100000";

signal b03: std_logic_vector(9 downto 0):= "1000010001";

signal b04: std_logic_vector(9 downto 0):= "0100000010";

signal b05: std_logic_vector(9 downto 0):= "1000000001";

signal b06: std_logic_vector(9 downto 0):= "0000100000";

signal b07: std_logic_vector(9 downto 0):= "1000011111";

signal b08: std_logic_vector(9 downto 0):= "1000000000";

signal b09: std_logic_vector(9 downto 0):= "0000000001";

signal b10: std_logic_vector(9 downto 0):= "0100000000";

signal b11: std_logic_vector(9 downto 0):= "0001001000";

signal b12: std_logic_vector(9 downto 0):= "0010000100";

signal b13: std_logic_vector(9 downto 0):= "0100000010";

signal b14: std_logic_vector(9 downto 0):= "0011100000";

signal b15: std_logic_vector(9 downto 0):= "0000111000";

signal b16: std_logic_vector(9 downto 0):= "0000001110";

signal b17: std_logic_vector(9 downto 0):= "1000111000";

signal b18: std_logic_vector(9 downto 0):= "1000001110";

signal b19: std_logic_vector(9 downto 0):= "1111110000";

signal b20: std_logic_vector(9 downto 0):= "1000000011";

signal b21: std_logic_vector(9 downto 0):= "1000000101";

signal b22: std_logic_vector(9 downto 0):= "1000011000";

signal b23: std_logic_vector(9 downto 0):= "1000010100";

signal b24: std_logic_vector(9 downto 0):= "1000010010";

signal b25: std_logic_vector(9 downto 0):= "0111100001";

signal b26: std_logic_vector(9 downto 0):= "1111111110";

signal b27: std_logic_vector(9 downto 0):= "1111111100";

signal b28: std_logic_vector(9 downto 0):= "0000000010";

signal b29: std_logic_vector(9 downto 0):= "0000011110";

signal b30: std_logic_vector(9 downto 0):= "1111000000";

signal b31: std_logic_vector(9 downto 0):= "0000001111";

signal b32: std_logic_vector(9 downto 0):= "1000001111";

signal b33: std_logic_vector(9 downto 0):= "1001110001";

signal b34: std_logic_vector(9 downto 0):= "1011100000";

signal b35: std_logic_vector(9 downto 0):= "1111111001";

signal b36: std_logic_vector(9 downto 0):= "1001111111";

signal b37: std_logic_vector(9 downto 0):= "1000011101";

signal b38: std_logic_vector(9 downto 0):= "1011100001";

signal b39: std_logic_vector(9 downto 0):= "0000000010";

signal b40: std_logic_vector(9 downto 0):= "1100000000";

signal b41: std_logic_vector(9 downto 0):= "0111101110";

signal b42: std_logic_vector(9 downto 0):= "0111111110";

signal b43: std_logic_vector(9 downto 0):= "0010000000";

signal b44: std_logic_vector(9 downto 0):= "0111100010";

signal b45: std_logic_vector(9 downto 0):= "0100001110";

signal b46: std_logic_vector(9 downto 0):= "1100000011";

signal b47: std_logic_vector(9 downto 0):= "0011001100";

signal b48: std_logic_vector(9 downto 0):= "0000110000";

signal b49: std_logic_vector(9 downto 0):= "1100000000";

signal b50: std_logic_vector(9 downto 0):= "0011000000";

signal b51: std_logic_vector(9 downto 0):= "0000111111";

signal b52: std_logic_vector(9 downto 0):= "0010000001";

signal b53: std_logic_vector(9 downto 0):= "0100000001";

signal b54: std_logic_vector(9 downto 0):= "1111110001";

signal b55: std_logic_vector(9 downto 0):= "1000001110";

type memory is array (INTEGER range <>) of std_logic_vector (9

downto 0);

signal H : memory (0 to 5):= (b01, b06, b06, b06, b01, b00);

signal O : memory (0 to 5):= (b42, b05, b05, b05, b42, b00);

signal L : memory (0 to 5):= (b01, b09, b09, b09, b09, b00);

signal A : memory (0 to 5):= (b01, b02, b02, b02, b01, b00);

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Key Blank Directory 12 Cross Reference Sec 10Document45 pagesKey Blank Directory 12 Cross Reference Sec 10Chuck ChongNo ratings yet

- Manhattan Bus Map: The BronxDocument1 pageManhattan Bus Map: The BronxAndreuPayáFerrándizNo ratings yet

- Key Cross ReferenceDocument17 pagesKey Cross ReferenceElie GuggerNo ratings yet

- TL-WR703N SchematicDocument1 pageTL-WR703N SchematicJuan DelacostaNo ratings yet

- Student ListDocument8 pagesStudent ListAnuradha SureshNo ratings yet

- 650 Point To Point Bolt ListDocument14 pages650 Point To Point Bolt ListDanny ArimaNo ratings yet

- Result Sheet 2009 10 BEC SY Sem2 Combined DisplayedDocument5 pagesResult Sheet 2009 10 BEC SY Sem2 Combined DisplayedVarad ShastriNo ratings yet

- State Sweden Ration CardsDocument116 pagesState Sweden Ration Cardsmb69goduNo ratings yet

- Japanese H Sections PDFDocument2 pagesJapanese H Sections PDFSAGARNo ratings yet

- Hitung Coil DailyDocument27 pagesHitung Coil DailyJeh Rvw4No ratings yet

- Slewing Bearing Slewing Ring Slewing Gear Swing CircleDocument15 pagesSlewing Bearing Slewing Ring Slewing Gear Swing Circlezczc32z5No ratings yet

- PDF Raster SRGBDocument63 pagesPDF Raster SRGBMirza VukovicNo ratings yet

- F3 Mock 2Document18 pagesF3 Mock 2Sayed Zain ShahNo ratings yet

- Reinforcement DetaDocument8 pagesReinforcement DetaS RajNo ratings yet

- NYC Subway MapDocument1 pageNYC Subway Mapgregoryo59100% (1)

- Method Time MeasurementDocument24 pagesMethod Time MeasurementEvita Nuriya RNo ratings yet

- Corey Johnson 'Let's Go' Transit PlanDocument104 pagesCorey Johnson 'Let's Go' Transit PlanGersh Kuntzman100% (2)

- Hawaii County Settlement AgreementDocument21 pagesHawaii County Settlement AgreementHonolulu Star-AdvertiserNo ratings yet

- Sort AmentDocument30 pagesSort AmentNugzarSheliaNo ratings yet

- 2 Train TimetableDocument10 pages2 Train TimetableMichaelNo ratings yet

- Conexpanduri - ROCASTDocument5 pagesConexpanduri - ROCASTAnonymous eD1l6o9ZsW0% (1)

- Haitian Flag Day FlyerDocument1 pageHaitian Flag Day Flyerbklcb14No ratings yet

- MA Graphic Design Information Design Elective Supporting MaterialDocument148 pagesMA Graphic Design Information Design Elective Supporting MaterialEleanor MaclureNo ratings yet

- CAMSTARDocument76 pagesCAMSTARruben neri ruizNo ratings yet

- U Bolt Lisega - 2Document4 pagesU Bolt Lisega - 2Mario AlcasarNo ratings yet

- Master Pengolahan BatimetriDocument355 pagesMaster Pengolahan BatimetriYadi SuryadiNo ratings yet

- Etabs ReportDocument361 pagesEtabs ReportGautam PaulNo ratings yet

- Tabla de RatioDocument33 pagesTabla de RatioLuis Antonio GuerraNo ratings yet

- PE4H VER24 SchematicDocument2 pagesPE4H VER24 SchematicB Huerta MuñozNo ratings yet

- 1 Comparison TableDocument18 pages1 Comparison TableamirNo ratings yet