Professional Documents

Culture Documents

Parallel FFT

Uploaded by

tasos1970Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Parallel FFT

Uploaded by

tasos1970Copyright:

Available Formats

RAD3 IP Cores Series: Parallel N-Point FFT/IFFT

Product Brief

Parallel N-Point FFT/IFFT

Core

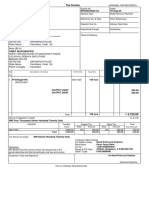

Parallel N-Point Fast Fourier Transform

Clock

PFFT/PIFFT Block

Reset

Input Valid Input Stage Output

Buffer Memory Buffer Output Valid

FFT /IFFT Mode

Scaling Select

FFT Radix

Control Elements

Input Dat a Output Dat a

1 t o P input 1 to P out put

samples samples

IP Core Names • Integration documentation and user

guide

R3PFFT – Parallel N-point FFT/IFFT

Overview

Features

• Extremely high throughput through The Parallel FFT/IFFT core is targeted for

programmable parallelization of input applications in broadband networking, high-

data samples. The core allows 1,2, 4, speed wireless and image/data processing

.., P (P<=N) samples to be computed where extremely high data throughput is

in parallel for increased data required.

throughput

• Ultra high speed (>3.2 Gsps) The FFT or inverse FFT is performed on the N

continuous time operation complex valued input samples. The value of

• Configurable number of points, N N can be any power of two. In addition, 1 to P

• Programmable input and output (P<=N) samples can be processed in parallel.

wordlengths and internal precision If 1 sample per cycle operation is chosen the

• Area efficient design core is equivalent to the SCFFT. The input,

output, and internal wordlengths are

selectable.

Deliverables

• Synthesizable RTL source code in Processor core is optimized for minimum area

VHDL or Verilog and maximum throughput. The design is

• Comprehensive verification test bench targeted for use in ASICs and FPGAs.

and vectors in VHDL or Verilog

• Matlab C based bit-correct simulation

model and SNR calculator

RAD3 Communications Inc. web: www.rad3comm.com

3553 – 31 Street NW, Suite 253 email: sales@rad3comm.com

Calgary, AB, Canada

T2L 2K7

RAD3 IP Cores Series: Parallel N-Point FFT/IFFT

Performance The SNR of the block is dependent on the

chosen internal wordlength and output

The PFFT/IFFT core is able to perform an N- wordlength.

point FFT/IFFT in N/P clock cycles where P

represents the number of samples computed The equivalent gate count for the logic area

in parallel. The throughput is P complex (including RAM requirements) of several

samples per clock cycle. The PFFT/IFFT core PFFTs is shown in Table 1. These FFTs range

processes data continuously with no pauses. from 64-point to 4096-point FFTs for 16-bit

data paths and values of P (data points

Maximum clock speed depends on the computed in parallel) ranging from 1 to 16.

application process and pipelining choices Note, that a target clock speed of 100 MHz

(and hence the final design real estate) but up was chosen for the benchmarks although

to 300 MHz for a 0.13 micron ASIC process speeds >300 MHz are easily achievable.

have been achieved. In order to achieve

higher clock rates the latency of the system It is worthwhile to note that the gate count

may increase as pipelining stages are added scales in less than linear fashion as the

in the arithmetic. number of parallel samples increases. For

example a 64-point FFT in which 16 samples

Signal scaling is controllable by the Scaling are computed in parallel requires only 7.3

Select input signal and for a 64-point FFT times as much area as a 64-point single data

could be chosen to yield any power of 2 sample per cycle FFT core.

scaling between 1 and 64 (i.e. 1, 2, 4, 8, …,

64).

Table 1: Gate Count for various N-point 16-bit Parallel FFT’s in 0.13µ TSMC Process

Points- Parallel Throughput Gate

N Samples - P (usec)1 Count

64 1 0.512 35,365

2 0.256 57,377

4 0.128 97,718

8 0.064 161,609

16 0.032 260,070

128 1 1.024 51,192

2 0.512 80,627

256 1 2.048 63,429

2 1.024 103,641

512 1 4.096 85,578

2 2.048 130,068

1024 1 8.192 134,245

2 4.096 180,903

4 2.048 281,094

4096 1 16.384 324,984

2 8.192 405,666

4 4.096 544,860

Note 1. Clock Rate = 200MHz

RAD3 Communications Inc. web: www.rad3comm.com

3553 – 31 Street NW, Suite 253 email: sales@rad3comm.com

Calgary, AB, Canada

T2L 2K7

RAD3 IP Cores Series: Parallel N-Point FFT/IFFT

The PFFT has also been synthesized for the Note that it is possible to decrease the FPGA

Virtex-5 series of FPGAs. Table 2 shows the hardware requirements for the PFFT

slice count, Block RAMs, and multiplier blocks implementations shown above if a lower clock

used for the FPGA implementation operating rate is desired. The multiplier blocks can be

at a nominal 100 MHz with 16-bit datapath. replaced with slice based multipliers and the

Note that speeds above 300 MHz are easily Block RAMs can be replaced with CLB RAMs

attainable on Virtex-5 devices. at the expense of a potentially lower clock

rate.

Table 2: Hardware Requirements for N-point 16-bit Parallel FFT’s in a Xilinx Virtex-5 FPGA

Points- Parallel Throughput Slices RAM’s Mult’s

1

N Samples - P (usec)

64 1 0.64 690 1 4

2 0.32 1509 0 8

4 0.16 2017 0 16

2

8 0.08 3323 0 28

1024 1 10.24 1542 7 12

2 5.12 2145 10 20

4 2.56 4032 12 40

Note 1. Clock Rate = 100MHz

Note 2. RAM’s replaced by Flip-Flop’s

Specifications subject to change without notice. Information furnished by RAD3 is believed to

be accurate and reliable. However, no responsibility is assumed by RAD3 for its use. All

company and product names are trademarks or registered trademarks of their respective owners.

All rights reserved. © 2009 RAD3 Communications Inc.

RAD3 Communications Inc. web: www.rad3comm.com

3553 – 31 Street NW, Suite 253 email: sales@rad3comm.com

Calgary, AB, Canada

T2L 2K7

You might also like

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- (McQuay Incorporated) Geothermal Heat Pump Design ManualDocument70 pages(McQuay Incorporated) Geothermal Heat Pump Design Manualtpqnhat100% (1)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Design of A Water-CO2 EvaporatorDocument78 pagesDesign of A Water-CO2 Evaporatortasos1970No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Co2 Pump TestingDocument3 pagesCo2 Pump Testingtasos1970No ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Thermoelectric Module Construction For Low Temperature Gradient Power GenerationDocument4 pagesThermoelectric Module Construction For Low Temperature Gradient Power Generationtasos1970No ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Echotek Series 1800GTDocument4 pagesEchotek Series 1800GTtasos1970No ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Polyphase Channelizer TransformationDocument17 pagesPolyphase Channelizer Transformationtasos1970No ratings yet

- Channel Spectral CharacteristicsDocument42 pagesChannel Spectral Characteristicstasos1970No ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Fpga Based Power Efficient Channelizer For Software Defined Radio MegDocument6 pagesFpga Based Power Efficient Channelizer For Software Defined Radio Megtasos1970No ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- A Comparison of FFT and Polyphase ChannelizersDocument49 pagesA Comparison of FFT and Polyphase Channelizerstasos1970No ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- FPGAs in Digital CommunicationsDocument25 pagesFPGAs in Digital Communicationstasos1970No ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- ControllingDocument8 pagesControllingAnjo Pasiolco Canicosa100% (2)

- Mcquillin Murphy ResumeDocument1 pageMcquillin Murphy Resumeapi-253430225No ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- CL Commands IVDocument626 pagesCL Commands IVapi-3800226100% (2)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Masters of Death: The Assassin ClassDocument5 pagesMasters of Death: The Assassin Classjbt_1234No ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Lana Del Rey NewestDocument11 pagesLana Del Rey NewestDorohy Warner MoriNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Checklist For HR Audit Policy and ProceduresDocument3 pagesChecklist For HR Audit Policy and ProcedureskrovvidiprasadaraoNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Motivate! 2 End-Of-Term Test Standard: Units 1-3Document6 pagesMotivate! 2 End-Of-Term Test Standard: Units 1-3Oum Vibol SatyaNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Jamaica's Unemployment Aims, Causes and SolutionsDocument23 pagesJamaica's Unemployment Aims, Causes and Solutionsnetzii300067% (3)

- Bhagavad Gita: Chapter 18, Verse 47Document3 pagesBhagavad Gita: Chapter 18, Verse 47pankaj kararNo ratings yet

- Understanding electromagnetic waves and radioactivityDocument7 pagesUnderstanding electromagnetic waves and radioactivityJayesh VermaNo ratings yet

- Vaccination Consent Form: Tetanus, Diphtheria / Inactivated Polio Vaccine (DTP) & Meningococcal ACWY (Men ACWY)Document2 pagesVaccination Consent Form: Tetanus, Diphtheria / Inactivated Polio Vaccine (DTP) & Meningococcal ACWY (Men ACWY)meghaliNo ratings yet

- Questions DR JekyllDocument4 pagesQuestions DR JekyllMaRieNo ratings yet

- Otis, Elisha Graves REPORTDocument7 pagesOtis, Elisha Graves REPORTrmcclary76No ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Wave of WisdomDocument104 pagesWave of WisdomRasika Kesava100% (1)

- The Power of Compounding: Why It's the 8th Wonder of the WorldDocument5 pagesThe Power of Compounding: Why It's the 8th Wonder of the WorldWaleed TariqNo ratings yet

- European Vacancy and Recruitment Report 2012Document200 pagesEuropean Vacancy and Recruitment Report 2012Joaquín Vicente Ramos RodríguezNo ratings yet

- Sagnik CVDocument3 pagesSagnik CVSagnik GangulyNo ratings yet

- PAPC - Internal Notes PDFDocument4 pagesPAPC - Internal Notes PDFHrushi Km GowdaNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Annex-4-JDVP Certificate of Learners MasteryDocument1 pageAnnex-4-JDVP Certificate of Learners MasteryZINA ARRDEE ALCANTARANo ratings yet

- Lecture1 SEODocument24 pagesLecture1 SEOUsman AnwarNo ratings yet

- Dalit LiteratureDocument16 pagesDalit LiteratureVeena R NNo ratings yet

- Creating Early Learning Environments PDFDocument25 pagesCreating Early Learning Environments PDFkrisnahNo ratings yet

- Orbit BioscientificDocument2 pagesOrbit BioscientificSales Nandi PrintsNo ratings yet

- Respiration NotesDocument2 pagesRespiration NotesBriana TaylorNo ratings yet

- Enneagram Type-2Document18 pagesEnneagram Type-2pundirNo ratings yet

- Multigrade Teaching NotesDocument4 pagesMultigrade Teaching Notesqw938No ratings yet

- MASM Tutorial PDFDocument10 pagesMASM Tutorial PDFShashankDwivediNo ratings yet

- Toyota TPMDocument23 pagesToyota TPMchteo1976No ratings yet

- PeripheralDocument25 pagesPeripheralMans FansNo ratings yet

- Nurses Assigned in Covid-19 Isolation Facilities. in This ConnectionDocument4 pagesNurses Assigned in Covid-19 Isolation Facilities. in This ConnectionDan HizonNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)