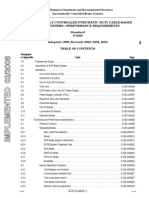

Professional Documents

Culture Documents

VishaySiliconix MOSFETBasics

Uploaded by

wenjunchen94539Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VishaySiliconix MOSFETBasics

Uploaded by

wenjunchen94539Copyright:

Available Formats

AN608

Vishay Siliconix

Power MOSFET Basics:

Understanding Gate Charge and Using It To

Assess Switching Performance

Jess Brown

INTRODUCTION

This is the second in a series of application notes that define The voltage VGS is the actual voltage at the gate of the device,

the fundamental behavior of MOSFETs, both as standalone and it is this point that should be considered when analyzing

devices and as switching devices implemented in a the switching behavior of the device.

switchmode power supply (SMPS). The first application note1

provided a basic description of the MOSFET and the If a step input is applied at VGS_APP, then the following holds

terminology behind the device, including definitions and true:

physical structure. This application note goes into more detail

on the switching behavior of the MOSFET when used in a

VGS_APP * VGS

practical application circuit and attempts to enable the ig + (1)

reader/designer to choose the right device for the application Rg

using the minimum available information from the datasheet.

The note goes through several methods of assessing the ig + igs)igd (2)

switching performance of the MOSFET and compares these

methods against practical results. Several definitions used

dVGS

within the text are drawn from application note AN605. igs + Cgs (3)

dt

SWITCHING THE MOSFET IN ISOLATION and since VDS is fixed

Using Capacitance dVGS

igd + Cgd (4)

dt

To get a fundamental understanding of the switching behavior

of a MOSFET, it is best first to consider the device in isolation therefore

and without any external influences. Under these conditions,

an equivalent circuit of the MOSFET gate is illustrated in

VGS_APP * VGS dVGS dV (5)

Figure 1, where the gate consists of an internal gate resistance + Cgs )Cgd GS

(Rg), and two input capacitors (Cgs and Cgd). With this simple Rg dt dt

equivalent circuit it is possible to obtain the output voltage

response for a step gate voltage. and

VDS

dVGS dt

+ (6)

VGS_APP * VGS ǒCgs)CgdǓR g

Igd

Cgd

giving

Ig Rg

VGS_APP

Cgs * lnǒV GS_APP * V GSǓ + t )k (7)

VGS

ǒCgs)C gdǓRg

Igs

VGS + VGS_APP*ke*tń(Cgs)Cgd)Rg

(8)

FIGURE 1. An equivalent MOSFET gate circuit showing just Cgs,

Cgd and Rg. @ t = 0, VGS = 0, therefore

1. AN605 Power MOSFET Basics: Understanding MOSFET Characteristics

ǒ

VGS + VGS_APP 1 * e*tń(Cgs)Cgd)Rg Ǔ (9)

Associated with the Figure of Merit. Doc. No. 71933.

Document Number: 73217 www.vishay.com

02-Dec-04 1

AN608

Vishay Siliconix

This gives an indication of how long the actual gate voltage

(VGS) takes to get to the threshold voltage. For illustration

purposes, a more practical circuit is shown in Figure 2, where

an additional resistance is placed between VDS and Cgd. In this

instance, the step response gets very complicated and the

equation (Equation 10) becomes very difficult to solve.

VDS

Rgd

Igd

Cgd

Ig Rg

VGS_APP

Cgs

VGS

Igs

FIGURE 2. An equivalent MOSFET circuit showing just Cgs,

Cgd and Rg, plus Rgd.

FIGURE 3. Graphs of plots of equations 9 (standard) and 10

(complex).

VGS_APP

VGS + VGS_APP * (A * B) (10)

2 Ǹk Plotting equations 9 and 10 in Figure 3 shows that there is only

about a 1ns difference in the time the gate voltage takes to get

to the threshold voltage of 1 V. Therefore it can be argued that

to adopt the less complex approach does not impinge

where

significantly on the accuracy of the gate voltage transient.

However, the point has been made that any calculated

ȡ

A +ȧǒCR ) ǸkǓe

tǒCR*ǸkǓ

ȣ switching times will be less than the actual transients seen by

ȧ the MOSFET.

*

2C gdR gdC gsR g

Ȣ Ȥ

k

As shown above, when the MOSFET is considered with

additional parasitics, it becomes increasingly difficult to

manipulate these equations manually for such a practical

circuit. Therefore a method of analyzing a practical circuit is

ȡ

B +ȧǒCR * ǸkǓe

tǒCR)ǸkǓ

ȣ required. If these second-order, or parasitic, components are

ȧ

*

2C gdR gdC gsR g

ignored, then it is possible to come up with formulas for the

Ȣ Ȥ

k

turn-on and turn-off time periods of the MOSFET. These are

given in Equations 11 through to 16 and the resulting

waveforms are shown in Figures 4 and 5. These equations are

CRk + CgsRg ) CgdR g ) C gdRgd based on those developed by B J Baliga2, where Rg is the

internal gate resistance, Rg_app is the external gate resistance,

and Vth is the MOSFET threshold voltage, and VGP is the gate

plateau voltage.

k + C 2gsR2g ) 2CgsR2gC gd * 2C gdRgdCgsR g

) C 2gdR2g ) 2C2gdRgR gd ) C 2gdR2gd 2. B.J. Baliga, Power Seminconductor Devices.

www.vishay.com Document Number: 73217

2 02-Dec-04

AN608

Vishay Siliconix

In this instance, t4 and t6 can be calculated accurately, but it is

ȡ ȣ the formula for t5 which is more difficult to solve, since during

t1 + (R g ) Rg_app)(Cgs ) Cgd ) lnȧ 1

V th ȧ (11) this time period VDS will change, causing Cgs to also change.

Ȣ1 * V

GS_APP Ȥ Therefore some method is required to calculate t3 and t5

without using the dynamic Cgd.

ȡ ȣ

t1 + (R g ) Rg_app)(Cgs ) Cgd) ln ȧ1 * 1

V ȧ (12)

Ȣ V

GP

GS_APP Ȥ IDS

(VDS * VF)(Rg ) Rg_app)C gd

t3 + (13) VDS

VGS_APP * VGP

VF is the voltage across the MOSFET when conducting full

load current and VDS is the voltage across the MOSFET when

it is off.

This gives an accurate t1 and t2 when using datasheet values,

but the time period t3 is difficult to calculate since Cgd changes VGS

with VDS.

t4 t5 t6

IDS FIGURE 5. Turn-off transient of the MOSFET.

Using Gate Charge to Determine Switching Time

VGS

Looking at the gate charge waveform3 in Figure 6, Qgs is

defined as the charge from the origin to the start of the Miller

VGP

Plateau (VGP); Qgd is defined as the charge from VGP to the

end of the plateau; and Qg is defined as the charge from the

Vth VDS origin to the point on the curve at which the driving voltage VGS

equals the actual gate voltage of the device.

t1 t3

t2

3

Qg

Gate-Source Voltage (V)

FIGURE 4. Turn-on transient of the MOSFET.

Qgd VGS

1

Qgs 2

VGP Miller

Plateau

Using the same principles for turn-off, the formulas for the

switching transients are given below:

ǒ Ǔ

Gate Charge (nC)

VGS_APP

t4 + (Rg ) Rg_app)(Cgd ) Cgs) ln (14)

VGP

FIGURE 6. Sketch showing breakdown of gate charge.

t5 + (Rg ) Rg_app)Cgd ǒ

V DS * V F

VGP

Ǔ (15)

t6 + (Rg ) Rg_app)(Cgd ) Cgs) ǒ Ǔ V GP

Vth

(16)

3. Gate Charge Principles and Usage, Power Electronics Europe.

Issue 3, 2002. Technology.

Document Number: 73217 www.vishay.com

02-Dec-04 3

AN608

Vishay Siliconix

The rise in VGS during t2 (Figure 4) is brought about by

charging Cgs and Cgd. During this time VDS does not change tir + ǒRg ) Rg_appǓǒCiss @Vds Ǔ

ǒ Ǔ

and as such Cgd and Cds stay relatively constant, since they (17)

vary as a function of VDS. At this time Cgs is generally larger gfs(V GS_APP * V th)

ln

than Cgd and therefore the majority of drive current flows into g fsǒVGS_APP * VthǓ * IDS

Cgs rather than into Cgd. This current, through Cgd and Cds,

depends on the time derivative of the product of the It is difficult to use a value of Cgd for the fall time period of VDS

capacitance and it’s voltage. The gate charge can therefore be (tvf=t3). Therefore if the data sheet value of gate charge is used

assumed to be Qgs. (Qgd_d) and divided by the voltage swing seen on the drain

connection (VDS_D minus VF_D) then this effectively gives a

The next part of the waveform is the Miller Plateau. It is

value for Cgd based on the datasheet transient.

generally accepted that the point at which the gate charge

figure goes into the plateau region coincides with the peak

Q gd_d (VDS * VF)(Rg ) R g_app)

value of the peak current. However, the knee in the gate tvf +

charge actually depends on the product4 (CgdVGD) with

respect to time. This means if there is a small value of drain

ǒ

(VDS_D * VF_D) VGS_APP * VTH ) ǒ I

DS

g fs

ǓǓ

(18)

current and large value of output impedance, then IDS can

actually reach its maximum value after the left knee occurs. Similarly for the turn-off transition, the voltage rise time (tvr = t5)

However, it can be assumed that the maximum value of the is:

current will be close to this knee point and throughout this

application note it is assumed that the gate voltage at the knee Q gd_d (VDS * VF)(R g ) R g_app)

tvr +

point corresponds to the load current, IDS.

ǒV Ǔ

I

(19)

DS

(VDS_D * VF_D) th ) g fs

The slope of the Miller Plateau is generally shown to have a

zero, or a near-zero slope, but this gradient depends on the

division of drive current between Cgd and Cgs. If the slope is and the current fall time (tif = t6) is:

non-zero then some of the drive current is flowing into Cgs. If

the slope is zero then all the drive current is flowing into Cgd. ȡǒV I

DS

th ) g fs

Ǔȣ

This happens if the Cgd VGD product increases very quickly tif + (Rg ) Rg_app)(Ciss @V

DS ) lnȧ ȧ (20)

and all the drive current is being used to accommodate the Vth

change in voltage across Cgd. As such, Qgd is the charge Ȣ Ȥ

injected into the gate during the time the device is in the Miller

Plateau.

COMPARING EQUATIONS WITH DATASHEET VALUES

It should be noted that once the plateau is finished (when VDS

reaches its on-state value), Cgd becomes constant again and The definition of the turn-on and turn-off times given in the

the bulk of the current flows into Cgs again. The gradient is not datasheet can be seen in Figure 7. These definitions can be

as steep as it was in the first period (t2), because Cgd is much equated to the equations described above and are shown

larger and closer in magnitude to that of Cgs. here:

COMBINATION OF GATE CHARGE AND td(on) [ t1 ) tir (21)

CAPACITANCE TO OBTAIN SWITCHING TIMES

tr [ tvf (22)

The objective of this note is to use datasheet values to predict td(off) [ t4 (23)

the switching times of the MOSFET and hence allow the

estimation of switching losses. Since it is the time from the end tf [ tvr (24)

of t1 to the end of t3 that causes the turn-on loss, it is necessary

to obtain this time (Figure 4). Combining 11 and 12 it is possible V tr td(off)

to obtain the rise time of the current (tir = t2 − t1) and because

VDS stays constant during this time then it is possible to use the VDS VGS

specified datasheet value of Ciss at the appropriate VDS value. 10% 10% 10%

Assuming the transfer characteristic is constant, then VGP can

be substituted for Vth + IDS/gfs, hence

10% 10% 10%

td(on) tf t

4. Ibid. FIGURE 7. Sketch showing definition of turn-on and turn-off times.

www.vishay.com Document Number: 73217

4 02-Dec-04

AN608

Vishay Siliconix

TABLE 1. and 9. These switching transients are for the Si4892DY

Worked Example for Switching Transients: Si4892DY implemented on the high-side of a buck converter

configuration. The circuit parameters were:

Calculations Min Typ Max Unit

VDS = 5 V, IDS = 5 A, VGS_APP = 5 V, and Rg_app = 10 W

Rg 0.6 0.8 1

Ω

Rg_app 5.4 6 6.6

Ciss@Vds 620 775 930

pF

Ciss@0 V 880 1100 1320

gfs 21.6 27 32.4 S

VGS_APP 9 10 11

V

Vth 0.8 1.4 1.8

IDS 0.9 1 1.1 A

Qgd_d 2.8 3.5 4.2 nC

VDS_D 13.5 15 16.5 V

IDS_D 11.2 12.4 13.6 A

rDS(on) 0.008 0.01 0.012 Ω

VF 0.0072 0.01 0.0132

VF_D 0.09 0.12 0.16 V

FIGURE 8. Measured current and voltage turn-on switching

VDS 13.5 15 16.5

transient.

t1 (Eqn 11) 0.28 0.79 1.6

tir (Eqn 17) 0.01 0.02 0.05

tvf (Eqn 18) 1.4 2.8 5.5

t4 (Eqn 14) 8.4 14.5 26.0

tvr (Eqn 19) 7.5 16.7 47.7

ns

tif (Eqn 20) 0.06 0.14 0.44

td(on) 0.29 0.81 1.7

tr 1.4 2.8 5.5

td(off) 8.4 14.5 26

tf 7.5 16.7 47.7

Datasheet

td(on) 10 20

tr 11 20

ns

td(off) 24 50

ns

tf 10 20 FIGURE 9. Measured current and voltage turn-off switching

ns transient.

The minimum switching transients were calculated using the

appropriate value of the parameters, which resulted in TABLE 2. Measured vs. Calculated

producing the shortest switching transient value. In some Calculations Min Typ Max Unit

circumstances this meant that the maximum value of a

tir (Eqn 17) 0.18 0.44 1.1

parameter was used to calculate the minimum switching

transient and vice versa for the maximum switching transients. tvf (Eqn 18) 1.6 3.7 8.4

ns

tvr (Eqn 19) 3.5 7.9 22

COMPARING EQUATIONS WITH MEASURED tif (Eqn 20) 0.95 1.0 1.5

SWITCHING TRANSIENTS

Measured

tir 16 20 24

The datasheet switching transients are measured with a

resistive load and are not truly representative of a practical tvf 8.8 11 13.2

ns

circuit. As such the device will not behave according to the tvr 10.4 13 15.6

ideal operation described above. Therefore, actual switching

tif 28 35 42

waveforms were measured, and these are shown in Figures 8

Document Number: 73217 www.vishay.com

02-Dec-04 5

AN608

Vishay Siliconix

Limitations of the Driving Circuit If Equation 25 is subtracted from VGS and solved for t, the tir

transient is:

Table 2 shows the comparison between the calculations and

the measured transients. It can be seen that the voltage tir + ǒRg ) Rg_appǓCiss @V

DS

transients are relatively close. However, the switching times of

the MOSFET are affected not only by the parasitic elements,

but also by the driving circuit. Under the conditions described ȡǒV Ǔ

GS_APP * V th )

ǒVGS_APP*VthǓgfsL ȣ (26)

lnȧ ȧ

above, the author has assumed that the gate circuit does not ǒRg)Rg_appǓCiss @V DS

limit the switching performance of the power MOSFET. For

example, with a MOSFET p-channel and n-channel driver, it is

ȧ ǒVGS_APP * VGPǓ ȧ

possible that the theoretical current into the gate will be larger Ȣ Ȥ

than that which the driver is able to supply. There are several

ways in which a MOSFET driver can be realized and this goes Applying the same principle for tif results in a current transient

beyond the study of this application note. The formulas as follows:

described in the text are used to gauge the switching times and

therefore estimate the switching losses without navigating tif + ǒRg ) Rg_appǓCiss @V

DS

complex formulas, models and expensive simulation software.

ȡV ǒ ȣ

(27)

g fsL

1)

ǒRg)Rg_appǓCiss @V DS

lnȧ ȧ

The major discrepancy is between the calculated and actual GP

current transients. These calculations are an order of ȧ ȧ

magnitude less than the actual transients. Therefore, further ȧ V th

ȧ

consideration has to be taken for the current rise and fall times

and this is described below.

Ȣ Ȥ

TABLE 3.

Current Transients Measured vs. Calculated with Package Inductance

The discrepancy between the calculated and the measured Calculations Min Typ Max Unit

occurs because the calculations assume an ideal situation. tir (Eqn 26) 4.7 8.1 13.2

One major parameter that can be considered into the tvf (Eqn 18) 1.6 3.7 8.4

equations is the package inductance of the MOSFET. This will ns

tvr (Eqn 19) 3.5 7.9 22

slow the current transient and can be taken into account with tif (Eqn 27) 8.1 17.9 32.8

relative ease if a few assumptions are made.

Measured

tir 16 20 24

Since the load current will generally be much larger than the

tvf 8.8 11 13.2

gate current, it is assumed that all the current through the ns

tvr 10.4 13 15.6

package inductance will be IDS. Therefore it can be shown that

the voltage across the package inductance of the MOSFET tif 28 35 42

during turn-on will be:

CONCLUSION

ǒVGS_APP * VthǓgfsL

VL +

ǒRg ) Rg_appǓCiss @V DS This application note shows good approximations for the rise

(25)

and fall times of the power MOSFET, when evaluated in

isolation. Datasheet values for the formulas derived can be

e *tń

ǒRg)Rg_appǓǒCiss @V DSǓ

used to get a reasonable indication of the switching

performance of the MOSFET as well as the switching losses.

However, as illustrated in Figure 3, the ideal switching

This is the voltage that occurs from the current transient and transients will always be shorter than those actually achieved,

as such subtracts from the gate voltage and hence slows down so the maximum parameters from the datasheet should

the current transient. always be used to give realistic results.

www.vishay.com Document Number: 73217

6 02-Dec-04

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Agilent 6811B User GuideDocument91 pagesAgilent 6811B User Guidewenjunchen94539No ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Agilent 6811B Quick GuideDocument20 pagesAgilent 6811B Quick Guidewenjunchen94539No ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Cmos Logic DataDocument450 pagesCmos Logic DataseleneedithNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- 2N3904Document7 pages2N3904api-3697683No ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- DTC DescriptorDocument3 pagesDTC DescriptorEngine Tuning UPNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Laboratory Activity #6Document3 pagesLaboratory Activity #6Jan Andrea Salicobay HermosoNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- TCE ComprehensionDocument142 pagesTCE ComprehensionJaydithya KumarNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Tales From The Tone Lounge - The Ultimate JCM800Document7 pagesTales From The Tone Lounge - The Ultimate JCM800JivReyNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Thiết Bị Merlin Gerin: Domae MCB, RCCBDocument14 pagesThiết Bị Merlin Gerin: Domae MCB, RCCBNgoc Nguyen KimNo ratings yet

- Mega Himel Pricelist 2021Document38 pagesMega Himel Pricelist 2021Fritz NatividadNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Nas MCQDocument7 pagesNas MCQPankaj KaleNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Ime Ee101Document4 pagesIme Ee101OsamaFaisalNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- ECEN 2632 Chapter 3Document5 pagesECEN 2632 Chapter 3tyutyuNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- AAR Spec S-4200Document58 pagesAAR Spec S-4200wizlish100% (1)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Service Manual Minarc Evo 150/180: Kemppi OyDocument31 pagesService Manual Minarc Evo 150/180: Kemppi OyCesar ObesoNo ratings yet

- Unit-2 QuestionsDocument3 pagesUnit-2 Questionsabhioptimus00No ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- 2016 - Programming in Arduino PDFDocument34 pages2016 - Programming in Arduino PDFMihai Bogdan100% (1)

- Sect. 3.4 How To Obtain The Input Port of The ModelDocument5 pagesSect. 3.4 How To Obtain The Input Port of The ModelPiero TorpocoNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- EEreviewerDocument80 pagesEEreviewerE-4296CASTILLOasistNo ratings yet

- Ee 201 - Basic Electrical EngineeringDocument4 pagesEe 201 - Basic Electrical EngineeringAshutosh Prasad YadavNo ratings yet

- Problem Set Zener DiodesDocument3 pagesProblem Set Zener DiodesSiva PrasadNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Optimal Planning Large Passive-Harmonic-Filters Set at High Voltage LevelDocument9 pagesOptimal Planning Large Passive-Harmonic-Filters Set at High Voltage LevelAlfredo Lopez CordovaNo ratings yet

- Application Guide For High Voltage Accessories PDFDocument182 pagesApplication Guide For High Voltage Accessories PDFpham thang100% (1)

- Practicing Electronics Technicians Handbook PDFDocument46 pagesPracticing Electronics Technicians Handbook PDFShung Tak ChanNo ratings yet

- EE TSGENCO ScheduleDocument6 pagesEE TSGENCO SchedulePrasad NarvaneniNo ratings yet

- Beee Worksheet 1Document9 pagesBeee Worksheet 120BCS7140No ratings yet

- Exp 03Document11 pagesExp 03Tahshin AbrarNo ratings yet

- (Top View) : 5 SD 4 FB 3 GND 2 OutputDocument13 pages(Top View) : 5 SD 4 FB 3 GND 2 OutputTulus PrasetyoNo ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Análisis de Circuitos Lineales 2da Edicion Raymond A. DeCarlo, Pen-Min Lin PDFDocument946 pagesAnálisis de Circuitos Lineales 2da Edicion Raymond A. DeCarlo, Pen-Min Lin PDFroy9302No ratings yet

- EE018-Earthing and Earth Electrode Resistance-Th-Inst PDFDocument29 pagesEE018-Earthing and Earth Electrode Resistance-Th-Inst PDFSameera KodikaraNo ratings yet

- Samsung srl3616b 3626b 3916b 3926b 3928b Web Neb NMB Neb NMB PDFDocument51 pagesSamsung srl3616b 3626b 3916b 3926b 3928b Web Neb NMB Neb NMB PDFZdravko Rusev0% (1)

- NSTIC Sci - Manual Part 1 PDFDocument95 pagesNSTIC Sci - Manual Part 1 PDFLycie Nablo - LaoyonNo ratings yet

- Chapter 9 CapacitorsDocument11 pagesChapter 9 CapacitorsnNo ratings yet

- Fire Alarm - Thermistor Circuit DiagramDocument8 pagesFire Alarm - Thermistor Circuit DiagramChandan Kumar Sharma0% (1)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)