Professional Documents

Culture Documents

Di

Uploaded by

zakari tairuOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Di

Uploaded by

zakari tairuCopyright:

Available Formats

design

Edited by Bill Travis and Anne Watson Swager

ideas

Centronics port generates narrow pulse widths

Darvinder Oberoi, CEDTI, Jammu, India

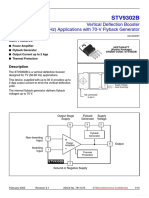

P1

ariable-pulse-width signals are

V

1

VCC 5V

useful in control circuitry for 14

Figure 1 2

positioning and holding pur- 15

poses in robotics and power electronics. 3 R2

J1

+

Frequently, the need arises for pulses with 16 1k

1

4 DESIRED PULSE

width less than 1 msec. Delays less than 17

2

3

1 msec are usually not available in most 5

R1

2

programming languages, so generating 18 Q1

SL100

6 10k

such pulses can be a problem. To gener- CENTRONICS 19

ate a fractional-millisecond delay you can PORT 7

20

use a PC’s 8254 16-bit timer (Counter 2), 8

which normally controls the PC’s speak- 21

er. The desired pulse is available at the 9

22

PC’s Centronics port (Figure 1) through 10

a buffer stage, which protects the port 23

from overload damage. Counter 2 oper- 11

24

ates at a clock frequency of 1.193181 12

MHz. To generate a pulse width less than 25

13

1 msec, you operate Counter 2 in mode

2 as a rate generator. You do this by set-

ting the control-word value to 0B4h and You can use the Centronics port on your PC to generate narrow pulse widths.

by writing this data to the control-regis-

ter port, address 43h. Initially, Counter 2 LISTING 1—TURBO C11 LISTING FOR PULSE GENERATION

contains FFFFh at address 042h. Bit 0 of (Continued on next page)

port 61h is at logic 1 to enable the count-

er, and bit 0 of the printer port (in this

case, 0378h, printer_port) is at logic 0.

Listing 1 contains the software necessary

for controlling the pulse-generation

process.

Setting bit 0 of port 61h enables

Counter 2. The counter decrements by

Centronics port generates

narrow pulse widths ......................................97

Preprocessor for rotary encoder

uses PAL ........................................................100

Inverters form three-phase VCO ..............102

Power inverter is bidirectional ..................104

Design Ideas Entry Blank ..........................106

www.ednmag.com August 2, 2001 | edn 97

design

ideas

LISTING 1—TURBO C11 LISTING

one every 0.8380958 msec. Before the FOR PULSE GENERATION (Continued)

generation of the pulse, it’s necessary to

compute Counter 2’s required count (re-

quired_count) to generate a pulse of de-

sired duration (desired_time). When the

counter is enabled, a “while” loop reads

back the counter’s count through port

42h in two read cycles. This count (count-

er_data) data helps to compute the

counts that have elapsed (count_

elapsed), and, once the required count

arrives, the software exits this read loop.

The software disables the counter by set-

ting bit 0 of port 61h to logic 0. The pulse

goes low for the desired time (for exam-

ple, 10 msec Off_Time). This cycle of

pulse generation with a desired width re-

peats until you press the “Q” or “q” key.

The software performs all its calculations

during the pulse’s off (low) time.

The software in Listing 1 uses Turbo

C11, Version 3. You can download List-

ing 1 from the Web version of this arti-

cle at www.ednmag.com. Using this soft-

ware, you can increase or reduce the

pulse width (desired_time) in variable

time steps (for example, 50 msec per

Time_Step) by using the numeric key-

pad’s keys 6 and 4, respectively. By press-

ing Key 5, you can fix the pulse’s duration

at a nominal value (for example, 500

msec Neutral_Time). Key 8 fixes the

pulse’s duration at the maximum desired

pulse width (for example, 750 msec

Max_Time). Key 2 fixes the pulse’s min-

imum desired width (for example, 250

msec Min_Time). The hardware we used

for testing the software is a P-II system

running at 400 MHz, with 32 Mbytes of

RAM, operating in MS-DOS mode.

Is this the best Design Idea in this

issue? Vote at www.ednmag.com/edn

mag/vote.asp.

98 edn | August 2, 2001 www.ednmag.com

design

ideas

Preprocessor for rotary encoder uses PAL

David Rathgeber, Alles Corp, Toronto, ON, Canada

otary encoders usu- the negative-going direction

R ally provide quadra-

ture pulses that indi-

cate both the amount of

LISTING 1—PAL SOFTWARE FOR ENCODER

PREPROCESSOR

outputs, and two other outputs

serve as D registers. A single

chip can thus condition two

rotation and the direction encoders with inputs and out-

(Figure 1). A microcon- puts left over for miscellaneous

troller can calculate the ro- encoding tasks. The design

tation direction and keep works as follows: The two ex-

track of angular movement. tra outputs serve as D-type

Many microcontrollers’ in- registers, with an encoder in-

terrupt inputs, such as those put as the data and the strobe

on the Zilog Z86C90, can serving as the clock. When an

detect only a falling edge. input (A or B in Figure 2)

Some with programmable changes, the corresponding de-

edge detection, such as the layed output (ADEL or BDEL)

Zilog Z86E30, can function changes on the next strobe.

with either rising or falling Therefore, the delayed outputs

edges but not both. Howev- mirror the inputs, with the de-

er, for maximum resolu- lay depending on the strobe’s

tion, it is desirable to look at frequency. An examination of

each rising and falling edge. the diagram in Figure 2 reveals

In these cases, you need four unique patterns that relate

four inputs to read the en- to forward encoder rotation

coder. Further, when you and four that relate to reverse

read the two inputs, you can rotation. Listing 1 shows the

assess the direction of rota- PAL software, in Synario for-

tion only by referring to the previous This design uses an AMD PALCE- mat. You can download the PAL software

read operation. The microcontroller thus 16V8Z that requires minimal supply cur- from the Web version of this article at

must keep track of the previous state of rent and costs less than $1. In addition to www.ednmag.com.

each input. You can use a simple PAL or the two encoder inputs, the scheme re-

other programmable-logic chip to pre- quires a strobe, which occurs much more

condition the encoder outputs to pro- frequently than the encoder edges. This

duce a single falling-edge output for each design uses the DS pin on the microcon- Is this the best Design Idea in this

rising and falling edge for each rotation troller, but you could probably use the issue? Vote at www.ednmag.com/edn

direction. crystal clock as well. Two PAL outputs are mag/vote.asp.

A

Figure 1 Figure 2

ADEL

ENCODER

OUTPUT A B

ENCODER

OUTPUT B BDEL

FORWARD ROTATION REVERSE ROTATION

FORWARD REVERSE

INTERRUPT INTERRUPT

To determine the direction of rotation, it’s necessary to detect both

rising and falling edges of the encoder outputs. A PAL produces unique patterns for forward and reverse rotation.

100 edn | August 2, 2001 www.ednmag.com

design

ideas

Inverters form three-phase VCO

Al Dutcher, AL Labs, West Deptford, NJ

ou sometimes need an inexpensive

Y VCO that can produce even-

ly spaced three-phase out-

puts over a wide frequency range. You

Figure 1

VDD

VDD

could use tracking all-phase filters with U04 U04 U04

2408 1208

only one oscillator, but this technique is 07

50k

difficult to implement and offers limited 2N3906

1N4148 1N4148 1N4148

range. Other methods, such as using a 680 680

DSP, are feasible, but they’re complex and

1N4148 1N4148 1N4148 ACTIVE CURRENT MODE

expensive. The inspiration for the VCO OR RESISTIVE CONTROL

in Figure 1 came from Texas Instru-

ments’ application notes of years ago, de- 100 nF 100 nF 100 nF

5V

tailing the use of unbuffered U-type in-

verters for use in ring oscillators. The

application note’s circuit consists of only

the inverters. The circuit generates rela-

tively squarish waveforms. Any ring os- A ring-type oscillator generates 3-phase outputs over a wide frequency range.

cillator’s operation depends on the fact

that an odd number of

inversions exists around

the loop. Any odd 400

Figure 2

number of inverters

would work. The feedback is

200

inverting, or negative. The

feedback creates an initial

bias equilibrium at the tran- VOLTAGE (mV) 0

sition voltage for the gates.

Loop gain greater than

unity is a necessary condi- 2200

tion for oscillation. Un-

buffered inverters typically 2400

have a gain of 15 or there- 3.5 4.1 4.7 5.3 5.9 6.5

abouts at dc and approxi- TIME (mSEC)

mately 7 with capacitive

loads. Three inverters thus The circuit in Figure 1 generates 12088-spaced, 600-mV p-p outputs.

have a total gain of more

than 340, which is plenty for oscillation. With no added capacitors, the circuit of ond, they allow the gates to operate as

At high frequencies, the inverters exhib- Figure 1 can operate at frequencies as current diverters, alternately charging

it a lagging phase shift arising from prop- high as tens of megahertz using and discharging the capacitors. The rate

agation delay. Enough lagging shift added 74ACU04 gates. Added capacitors can at which the capacitors discharge de-

to the inversions ultimately turns the to- drop the frequency to usable levels. The pends on the common supply current to

tal inversion into noninversion. The cir- frequency equates to IDD/3C. For lower the inverters. This rate and, hence, the os-

cuit of Figure 1 starts out with the 1808 frequency applications, 74HCU04 gates cillation frequency is proportional to the

inversion and adds 608 of lag for 2408 per are suitable, because they’re less sensitive operating current. The range of frequen-

stage. Three stages of 2408 works out to to layout considerations. cies over which the circuit can operate is

7208 total. This figure represents two The diodes in Figure 1 perform two more than 1000-to-1 (supply current

complete trips around the phase circle for tasks. First, they limit the excursions of from 10 mA to 10 mA). Note that at the

noninversion. Noninversion implies re- the gates to 600 mV p-p, so that the gates low-current, low-frequency end of the

generation, which begets oscillation. always operate in their linear region. Sec- range, the circuit cannot supply much

102 edn | August 2, 2001 www.ednmag.com

design

ideas

signal current and might need buffering. put so that the amplifier delays track at

Figure 2 shows the three-phase 1207 higher frequencies. In principle, you can

Figure 3

waveforms. The concept doesn’t 907

extract any set of phase angles by the ju-

work well with normal ac- or HC- 07 dicious adjustment of component am-

DIFFERENCE

buffered gates, because they have far too plitudes in the external circuits. The cir-

much gain and would drive the nodes cuit’s main drawback is that it does not

into square waves. The ACU and HCU 2407 have a high-Q resonator attached, so

types are somewhat obscure, but they phase noise could be a problem. When

nonetheless have multiple sources. Don’t Vector subtraction of two outputs produces a you incorporate the circuit into a rela-

forget to ground the inputs of the re- 908 quadrature signal. tively tight PLL circuit, the performance

maining three gates of these hex devices. improves considerably. The capabilities

Floating inputs are verboten with all connect a differential amplifier to the 120 of this oscillator allow it to lock over a

CMOS devices. and 2408 outputs. It rejects the common- wide range of frequencies.

The circuit generates three equally mode, 1808 components. The difference

spaced outputs. Because it generates sub- between these two outputs is at 908, and

stantially sinusoidal outputs, you can eas- it tracks well over the range of the oscil- Is this the best Design Idea in this

ily obtain quadrature-spaced outputs by lator. You can use the same type of dif- issue? Vote at www.ednmag.com/edn

trigonometric means (Figure 3). You can ferential amplifier to amplify the 08 out- mag/vote.asp.

Power inverter is bidirectional

Tom Napier, North Wales, PA

f you want to swap charge in either

I direction between unevenly

loaded positive and negative

battery buses, you need an inverting dc

Figure 1

POSITIVE

INPUT/OUTPUT

47k

RATIO ADJUST

NEGATIVE

OUTPUT/INPUT

transformer. One implementation is the 50k

symmetrical flyback converter shown in

Figure 1. The circuit can generate a neg- 10k T1

ative output from a positive supply or a

positive output from a negative supply.

8

When the circuit starts up, the substrate VCC

diode of the output FET bootstraps the DISC RST 4

+ 555

output voltage to the point where syn- (CMOS) 6.8 mF

6.8 mF

chronous switching takes over. When the 6 THRES OUT 3

+

gate-switching signal is symmetrical, the

output voltage is approximately 295% of 2 TRIG CON

the input voltage, and the efficiency is GND

1

greater than 80%. You can obtain voltage 1000 pF IRF520 IRF9530

step-up or step-down by adjusting the

switching ratio.

When I used the circuit between two

4V lead-acid batteries, a comparator ad-

justed the switch ratio to drive charge in An inverter circuit swaps charges between opposite-polarity batteries.

the desired direction. The circuit auto-

matically replaces charge drained from can add gates to the drive circuit to turn age. My prototype supplies approxi-

one battery to the other. In a short-bat- off both FETs whenever the battery volt- mately 100 mA.

tery-life application, the 2.5-mA standby ages balance. The minimum input volt-

current from each battery may be negli- age is a function of the gate thresholds Is this the best Design Idea in this

gible. Using lower-gate-capacitance, of the FETs. The 69V rating of the issue? Vote at www.ednmag.com/edn

FETs can reduce losses. Alternatively, you CMOS 555 timer sets the maximum volt- mag/vote.asp.

104 edn | August 2, 2001 www.ednmag.com

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Thundercat - Art of Approaching 2nd EditionDocument180 pagesThundercat - Art of Approaching 2nd Editionanon-34060094% (16)

- Multistage AmplifierDocument18 pagesMultistage AmplifierSai SadiqNo ratings yet

- Auditor RotationDocument48 pagesAuditor Rotationzakari tairuNo ratings yet

- Hacking Made EasyDocument1 pageHacking Made Easyzakari tairuNo ratings yet

- Electronics GuideDocument22 pagesElectronics GuideFernandes KennethNo ratings yet

- Master Ching Hai's BookletDocument104 pagesMaster Ching Hai's BookletKgosima NcubeNo ratings yet

- Voltage Level Translation Guide: Auto-Direction Sensing Direction Controlled Application-SpecificDocument10 pagesVoltage Level Translation Guide: Auto-Direction Sensing Direction Controlled Application-SpecificMendozaeu JonnyNo ratings yet

- Unit 3.1 Miller EffectDocument3 pagesUnit 3.1 Miller EffectchettiyathNo ratings yet

- NSK OscillatorDocument9 pagesNSK OscillatorJose BerrospiNo ratings yet

- 555 Full PWM CircuitDocument2 pages555 Full PWM CircuitNash_HoleNo ratings yet

- Data Sheet 74 HC 157Document7 pagesData Sheet 74 HC 157Emmanuel Mariano GómezNo ratings yet

- Transceivers Architectures For Mobile & Wireless ApplicationsDocument53 pagesTransceivers Architectures For Mobile & Wireless Applicationsrjost0% (1)

- UNIT3Document41 pagesUNIT3Azliana Mohd TaibNo ratings yet

- Integrated Power Solution For TFT-LCD: Global Mixed-Mode Technology IncDocument1 pageIntegrated Power Solution For TFT-LCD: Global Mixed-Mode Technology IncVeicon VecNo ratings yet

- Sony KV-25X5Document8 pagesSony KV-25X5todorloncarskiNo ratings yet

- D D D D D D D D D: DescriptionDocument37 pagesD D D D D D D D D: DescriptionAlberto MiglinoNo ratings yet

- 12V To 120V DC DC Converter Using Power Electronics For Higher Efficiency and Reliable Operation PDFDocument23 pages12V To 120V DC DC Converter Using Power Electronics For Higher Efficiency and Reliable Operation PDFAndy Espinosa GutiérrezNo ratings yet

- DLDforFall2017 18Document58 pagesDLDforFall2017 18Ramzan AliNo ratings yet

- Secondary Side Synchronous Rectification Control: Implementation and SR Features For Flyback Tomáš TichýDocument62 pagesSecondary Side Synchronous Rectification Control: Implementation and SR Features For Flyback Tomáš TichýLeonardo OrtizNo ratings yet

- Principles of Digital Techniques On Web PDFDocument5 pagesPrinciples of Digital Techniques On Web PDFmdwalunjkar3095No ratings yet

- Assignment 1 - Soution PDFDocument4 pagesAssignment 1 - Soution PDFPrathib VpNo ratings yet

- Digital Voltmeter Using Icl7107Document3 pagesDigital Voltmeter Using Icl7107syed_hafeez_2100% (1)

- Peripheral-Interfacing of 8085 - Free 8085 Microprocessor LectureDocument3 pagesPeripheral-Interfacing of 8085 - Free 8085 Microprocessor Lecturebaibhavvvv0% (1)

- Interpretation of Result 5&6Document4 pagesInterpretation of Result 5&6Jan ClarosNo ratings yet

- OscillatorsDocument13 pagesOscillatorsNafis Mustakin100% (1)

- STV9302B: Vertical Deflection Booster For 2-A TV (50-60 HZ) Applications With 70-V Flyback GeneratorDocument15 pagesSTV9302B: Vertical Deflection Booster For 2-A TV (50-60 HZ) Applications With 70-V Flyback GeneratorTecnico GenioNo ratings yet

- SRAM and DRAMDocument2 pagesSRAM and DRAMBiju AngaleesNo ratings yet

- Graf - Encyclopedia of Electronic Circuits - Vol 5Document765 pagesGraf - Encyclopedia of Electronic Circuits - Vol 5Mansour Alazmi100% (3)

- 2 KM FM Transmitter Circuit Diagram, Working and ApplicationsDocument27 pages2 KM FM Transmitter Circuit Diagram, Working and Applicationsinfluemento agborNo ratings yet

- Opa1632 Used in AMB Laboratories SchematicsDocument35 pagesOpa1632 Used in AMB Laboratories SchematicscosNo ratings yet

- Psoc 3 and Psoc 5Lp Clocking Resources: Clock SourcesDocument10 pagesPsoc 3 and Psoc 5Lp Clocking Resources: Clock SourcesAngelo TatlonghariNo ratings yet

- Transmission Line XDocument21 pagesTransmission Line XKifaru Micro-electronicsNo ratings yet

- EED LabDocument7 pagesEED LabVINITA AGARWALNo ratings yet

- 555 Timer 40khz IRDocument2 pages555 Timer 40khz IRapi-3712130No ratings yet

- Bandgap Second Order Curvature Correction in ProductionDocument23 pagesBandgap Second Order Curvature Correction in ProductionRichu GuptaNo ratings yet