Professional Documents

Culture Documents

SDR in Direction Finding RFDesign 0105

Uploaded by

vaibhawamishra32Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SDR in Direction Finding RFDesign 0105

Uploaded by

vaibhawamishra32Copyright:

Available Formats

Software-Defined Radio

SDR platform enables reconfigurable direction

finding system

A software-defined radio (SDR) transceiver platform is used to implement a

reconfigurable direction finding (DF) system. This article will describe the

intended data flow and data rate requirements of a typical DF system, map the

DF software components to the SDR platform, and demonstrate the availability

of resources for more complex implementations.

By Jyothsna Rajan

D irection finding (DF) is the process of

obtaining the angle of arrival bearings

of radio signal emitters. DF has multiple

system or tracing a signal interference source

or locating a hostile target.

Most DF methods inherently use the

nae, arranged in a known configuration, to

calculate its bearing.

A typical DF system must allow the user

military and commercial applications, such phase of the incident signal wave front and to perform spectral analysis over a predefined

as remotely guiding an aircraft navigation its relative time-of-arrival at multiple anten- frequency band, select a signal of interest

Figure1. Direction finding demonstration system processing blocks.

36 http://www.rfdesign.com January 2005

■ channelize the data to extract the signal/s

of interest:

■ provide high-speed data transfer capabil-

ity; and

■ simultaneously process channel data from

multiple receivers to deduce the angle of

arrival (AOA).

Although a variety of available processing

boards and I/O modules can cater to one

or more of the above functions, there are

few systems that can provide all of the

functionality in a seamlessly integrated

environment. One system that is capable of

combining the above-mentioned fundamental

functions is Spectrum’s flexComm™

SDR-3000 integrated development system.

This commercial off-the-shelf (COTS)

platform was recently used to demonstrate

a software-defined DF system. Using this

example, this paper will discuss the architec-

ture of the SDR-3000 system, describe the

intended data flow and data rate require-

Figure 2. Software task mapping. ments of a typical DF system, map the

Figure 2. Software task mapping. DF software components to the SDR-3000

hardware components and demonstrate the

and then locate the source. This requires a characteristic variations, environmental availability of resources for more complex

system that can: effects, etc.; implementations.

■ digitize received analog IF signals; ■ perform windowing and digital filtering;

■ synchronize data from multiple receivers; ■ execute FFT algorithms on the sampled Why SDR-3000?

■ calibrate data to account for component data; The SDR-3000 provides a hardware

Circle 29 or visit freeproductinfo.net/rfd

38 http://www.rfdesign.com January 2005

PowerPC™; and

■ baseband processing board (PRO-3500)

with two onboard Motorola MPC7410

PowerPCs and an IBM 405GP PowerPC.

The system provides the combined high-

speed logic execution capability of the

Virtex-II FPGAs with the algorithm execu-

tion capability of PowerPC MPC7410

G4 processors. A multi-input transition

module (TM1-3xxx) enables the system

to simultaneously receive inputs from

different receivers, digitize and then transmit

the data to the signal conditioning board

(PRO-3100) via a high-speed digital IF

fabric at rates up to 1.28 Gbps. Spectrum’s

flexFabric communications architecture,

based on RapidIO™ technology, facilitates

interprocessor communications throughout

the system for high-speed deterministic

data flows, while PCI-based communications

is used for “soft real-time” payload data

and control. In addition, the PRO-3100

and the PRO-3500 boards are network

Figure 3. GUI display. enabled, allowing the SDR-3000 to easily

operate as part of a larger system.

architecture and system configuration that ■ multi-input transition module (TM1-3xxx);

enables users to combine all of the ■ signal conditioning board (PRO-3100) Application framework

fundamental functions required in a DF with four user-programmable Xilinx® A basic application was developed to

application. The standard SDR-3000 system Virtex-II™ XC2V6000 field-programmable demonstrate the capability of the SDR-3000

consists of: gate arrays (FPGAs) and an IBM 405GP to operate independently or as part of a

Circle 31 or visit freeproductinfo.net/rfd

40 http://www.rfdesign.com January 2005

bins is displayed. The zoom feature on

the GUI allows the user to increase the

bin resolution on the display. During opera-

tion, the user selects a frequency of

interest from the base spectral display, and

continually zooms in until the display resolu-

tion is one bin per pixel.

Using the mouse, the user can then

select the signal of interest, and the GUI

transmits the pixel index of the selected SOI

to a processor that uses the zoom-level

and the display width to identify the bin

Figure 4. DFDS(S) system configuration. number. A bin extractor, executing on the

FPGA, extracts the in-phase (I) and quadra-

larger DF system. This application enabled of channel data storage memory to 64 Mbytes/ ture (Q) data corresponding to the

the user to: input mandates that the signal of interest required bin for each of the four inputs

■ receive and process inputs coherently be on air for a minimum of 2.5 seconds and forwards it to an MPC7410 on the

from four high-frequency (HF) antennae in order to be detected and its AOA calcu- PRO-3500. This processor first calculates

channels; lated. The same channel data is used to the phase for each input and then calculates

■ calibrate the input channels; calculate the power spectral density (PSD) the AOA of the SOI from the phase data

■ display a composite power spectrum on for each channel. Since the aim of this for the individual inputs. This AOA value

a host computer; first stage is merely to identify a strong is then transmitted to the GUI for display

■ select a signal of interest (SOI) from a signal within the operating frequency range, on the compass rose.

spectral display; and the data corresponding to a channel is

■ calculate the AOA and display it on a summed across the four inputs and then Data flow in the basic DF

compass rose. displayed. Spectral averaging is used to application

To provide portability across OS and provide data at a rate sufficient to meet the Figure 1 shows the signal data path

operation in a distributed environment, a display update rates. and processing blocks implemented in the

CORBA-enabled client-server design was The GUI displays the PSD data for DF application. Two of the user-program-

used. A JAVA-based GUI acted as a client, the entire range (0 MHz to 40 MHZ). Since mable FPGAs are used to service sampled

and applications running on the MPC7410 the spectral display is only capable of data from four antennae and buffer the

processors acted as servers. displaying 800 to 1000 horizontal pixels, data for bin extraction in their local

The design emphasis was to demonstrate each pixel represents data from multiple SDRAMs. A bin extraction module within

the ability to use the SDR-3000 system FFT bins or frequency channels, with each FPGA calculates the bin number

as a direction finder and not to develop the highest PSD value within the set of corresponding to the selected SOI and

a sophisticated DF system in its entirety.

Accordingly, greater attention is paid

to implementing typical DF application

tasks and meeting functional requirements.

Concept of operation

The current design uses the IF sampling

conversion technique [1] using an ADC

operating at 80 MSPS. Signal amplifiers

and low-pass filter at the front end limit

the operational frequency range between

10 MHz and 40 MHz.

For this application, the system used

FFT cores from RF Engines Ltd. (RFEL),

a technology partner that specializes in

advanced FPGA IP cores. RFEL’s FFT

core, capable of servicing two simultaneous

inputs, is used to channelize the data

into 2.5 kHz wide channels. The digital

filters in the FFT core have a cut-off

frequency of 40 MHz and an 80%

passband distributed evenly about the center

frequency, giving an operating frequency

range of 4 MHz to 36 MHz. The software

and hardware characteristics modify the net

frequency range to 10 MHz to 32 MHz.

Sixty four MB of SDRAM memory is used

to store channel data for about 2.5 seconds

for each of the four inputs. The restriction Figure 5. DFDS(T) system configuration.

42 http://www.rfdesign.com January 2005

Table 1.

User-programmable FPGA 1 (processes the spectral data)

Device utilization summary: need for unnecessary high-speed bulk data

Number of External IOBs 184 out of 824 22% transfers without compromising system

Number of LOCed External IOBs 184 out of 184 100% performance."

Number of MULT18X18s 4 out of 144 2%

DF and calibration algorithms

Number of RAMB16s 45 out of 144 31% The DFCP incorporates a DF algorithm

Number of SLICEs 2862 out of 33792 8% suitable for use with fixed antenna systems.

Number of BUFGMUXs 8 out of 16 50% It uses the phase of the incident signal at

Number of DCMs 4 out of 12 33%

an antenna to detect the AOA. This simple

algorithm calibrates the DF data but

User-programmable FPGA 0 and 2 (implements the decimation/FFT core) does not compensate for multipath effects.

Device utilization summary: The DFCP also has the ability to average

Number of External IOBs 203 out of 824 24% a user-defined number of sequential DF

measurements before passing it on to

Number of LOCed External IOBs 203 out of 203 100%

the host.

Number of MULT18X18s 84 out of 144 58% The data from the four antennae traverse

Number of RAMB16s 136 out of 144 94% through different cables and hardware

Number of SLICEs 14787 out of 33792 43% components (filters, amplifiers, ADC/DAC)

prior to the DDC stage. The system must

be calibrated to compensate for relative

extracts the FFT data for that bin from The DF/calibration controller (DFCC) phase and amplitude imbalance caused by

the delay buffer. A third user-programmable and spectral data controller (SDC) are physical and electrical properties of the

FPGA is used to calculate the PSD for used to configure the FPGA application cables and hardware components. Calibra-

spectral analysis. A spectral averaging resources in response to commands from tion is mandatory the first time the system is

module on this FPGA allows the user the GUI. The controller blocks communicate powered on and must be repeated whenever

to control the rate at which the PSD data with the servers over the network using there is a change in hardware, cables, antenna

is sent to the PPC7410 processing nodes. TCP/IP sockets. configuration or at extended time periods

On the PRO-3500, one PPC7410 node The processing blocks described earlier to account for component degradation due

is used to execute the DF and calibration can be implemented on any of the available to aging. The current design assumes that

algorithms while the second node is used 405GP or PPC7410 processing nodes. calibration and DF processing are mutually

to scale spectral data corresponding to Different placement schemes were evaluated, exclusive functions and consequently uses

the zoom level selected on the spectral each requiring different intertask data a different set of firmware images for the

display. communication methods. The primary metrics user-programmable FPGAs for performing

used for comparison included, but are off-line calibration. Each time the DF

Task classification and mapping not limited to, the following: algorithm is executed on a selected data

Figure 2 shows the major software ■ data throughput (high, low); bin, run-time calibration uses the calibration

task breakdown for the basic DF application, ■ frequency of data transmission (frequent, data to compensate for inherent differences

data flow, task to processor mapping continuous, intermittent on request); introduced by the different components in

and the protocols used for intertask ■ protocol or transport medium; and the input data paths.

communication. ■ scope (within same processor, different

The graphical user interface (GUI) ex- processor on same board, processor on a Design verification

ecutes on a Windows PC and displays different board). Two configurations, varying only in

the frequency spectrum and bearing of The mapping scheme shown in Figure 2 the way the received signals are fed to the

the received signal. The GUI is written provides judicious use of resources and SDR-3000 system, were used to verify the

in JAVA and operates as a CORBA-enabled allows implementation of data manipulation system design. The DFDS(S) configuration,

client interacting with the CORBA-enabled techniques that eliminate the need for shown in Figure 4, uses a single signal source

DF and spectral data servers on the unnecessary high-speed bulk data transfers but different cable lengths to simulate the

PPC7410 nodes. Figure 3 shows a typical without compromising system performance. phase difference between signal incidents

display on the GUI. Many different software partitioning and at the different antennae.

The DF and calibration processor (DFCP) mapping schemes were evaluated. Of DFDS(T) configuration, uses antennae

task reads the selected bins of interest from these, the current software task mapping arranged in a rectangular array as shown

the bin extraction module on the FPGA scheme, shown in Figure 2, provides the in Figure 5, to receive CB radio frequency

and calculates the AOA. maximum processor idle times and free band- signals emitted by a COTS CB radio. The

The DF and calibration server (DFCS) width on the interboard and intraboard four COTS HF omni antennae were mounted

services DF and calibration-related data communication bus. at optimum spacing for operation up to

requests and configuration commands from "Many different software partitioning and 32 MHz.

the GUI. The spectral data server (SDS) mapping schemes were evaluated. Of these, All functions and operational features

services spectral display-related data the current software task mapping scheme, of the DFDS(S) were satisfactorily tested

requests and configuration commands. shown in Figure 2, provides the maximum in the presence of the end user. Cables

The spectral data processor (SDP) con- processor idle times and free bandwidth on of pre-calculated lengths were used to

tinuously fetches spectral data from the the interboard and intraboard communica- simulate signal source at cardinal points

user-programmable FPGAs and scales it tion bus through judicious use of resources. (N, S, E, W) and at ±45 from them (NE,

for display using the most recent zoom index This allows implementation of data NW, SE, SW). Testing covered the

and display area pixel count. manipulationtechniques that eliminate the entire operating frequency range from

44 http://www.rfdesign.com January 2005

10 MHz to 32 MHz. The simulated system processing power, speed, and design and

displayed AOA to an accuracy of ±5. operational flexibility required to perform

DFDS(T) was tested in a parking the complex functions. Furthermore, the

lot setting exhibiting a minimal level of team was able to design, develop, procure

multipath. The spectral display successfully equipment, and test and validate the

showed peaks at frequencies equal to DF system on this platform in only four

that of received signals. The AOA display months.

for this case exhibited ±25 accuracy. The system can be expanded to accommo-

This ambiguity was expected, as the test date more input channels by adding addi-

environment was not completely multipath- tional transition module and PRO-3100

free and reflection-free while the implemented pairs. Channel data must be synchronized

DF algorithm assumed such ideal across all the transition modules. To

conditions. handle the increased data volume and

channelization requirements, additional

Capability demonstration and FPGA cores and software tasks may need

system acceptance to be incorporated and the software task

All system requirements were either mapping either re-partitioned or new soft-

met or exceeded. Despite using a simple ware tasks added.

DF algorithm, the DFDS(T) was able to This platform can also be used to

display AOA to within ±5 when tested efficiently perform multiple simultaneous

out in the open. System resource usage DFs on multiple signals of interest. This

statistics clearly depicted that sufficient may require the use of different channelization

resources were available to expand the techniques and probably, implementation of

system to include more inputs or use wideband and narrowband channelization.

more complicated algorithms. The delivered As an example, a user could implement

system, configured as a stand-alone unit, a beam former to scan a wide frequency

could be easily transported, set up and range, automatically detect signals with power

operated. above a preset threshold, and then use

Resource usage statistics for the narrowband channelization to extract the

user-programmable FPGAs are shown in signal of interest. RFD

Table 1.

The majority of user-programmable References

FPGA 0 and 2 slices are used up by 1. L. Pucker, “Channelization Techniques

RFEL’s FFT core with very little usage for Software-Defined Radio,” Proceedings

by application processing code. Most of of the SDR Forum Technical Conference,

FPGA 1 is still unused. This leaves an November 2003.

entire user-programmable FPGA and

associated SDRAM for any additional pro-

cessing and delay buffer implementation.

Depending on the size of the FFT/DDC

core used, more optimal designs can be ABOUT THE AUTHOR

developed to implement additional process- Jyothsna Rajan is an Applications

ing on these FPGAs, such as IFFT, mod/ Engineer with Spectrum Signal

demod or decoding. Processing Inc. in Burnaby, B.C.,

In the current design, the 7410s continu- Canada. With more than 13 years

ally extracts bin data and spectral data of experience, her areas of expertise

from the PRO-3100. With this processing, include digital signal processing and

the 7410 used for DF and calibration is lightly real-time embedded systems software

loaded while the 7410 used for spectral for distributed communications and

data processing is occupied most of the control. She received her Bachelor

time. However, with minor software modifi- of Engineering from Karnataka

cations that allow the two processors to Regional Engineering College in

process data only upon request from the India and a Masters in Electrical

user, the processor idle time can be consider- Engineering, specializing in DSP/

ably increased. communications from the University

of Saskatchewan in Saskatoon,

Conclusion Canada. Prior to joining Spectrum,

A direction finding system demands she worked under the aegis of

a high degree of functionality. Today, Telecommunications Research Lab

COTS platforms are sophisticated enough at Saskatoon developing a portable

for DF applications as successfully demon- wideband microseismic system for

strated with the flexComm SDR-3000. fault location in underground mines.

The platform provided the necessary

Circle 35 or visit freeproductinfo.net/rfd

46 http://www.rfdesign.com January 2005

You might also like

- BAN Body Area Antenna PresentationDocument21 pagesBAN Body Area Antenna PresentationYingying Chok100% (1)

- 2005 04 05 Hydrofest 3 - AcousticsDocument69 pages2005 04 05 Hydrofest 3 - AcousticsSt3fandragos4306No ratings yet

- Wearable Textile Antenna Design in Body Centric Wireless Communications A Systematic Literature ReviewDocument5 pagesWearable Textile Antenna Design in Body Centric Wireless Communications A Systematic Literature ReviewPadmavathy Velayudham100% (1)

- Datasheet SRM3006 EN PDFDocument20 pagesDatasheet SRM3006 EN PDFMark LionNo ratings yet

- IIT-BHU Literature Review of Direction Finding AntennasDocument29 pagesIIT-BHU Literature Review of Direction Finding AntennasVaishali SinghNo ratings yet

- How To Measure LTEDocument13 pagesHow To Measure LTEfarrukhmohammedNo ratings yet

- SHIELDED EQUIPMENT ENCLOSURE DESIGN GUIDEDocument15 pagesSHIELDED EQUIPMENT ENCLOSURE DESIGN GUIDELéo FelerNo ratings yet

- Range Resolution Improvement of FMCW RadarsDocument104 pagesRange Resolution Improvement of FMCW RadarsLe Duy Trung0% (1)

- Signal ProcessingDocument7 pagesSignal ProcessingZee DeckardNo ratings yet

- CSTD-104-439 - Simulation of Wearable Antennas For Body Centric Wireless Communications (Repaired)Document56 pagesCSTD-104-439 - Simulation of Wearable Antennas For Body Centric Wireless Communications (Repaired)Sandhya PandeyNo ratings yet

- The DSE Radio Direction Finder PDFDocument4 pagesThe DSE Radio Direction Finder PDFlazarosNo ratings yet

- 725 Intro-F12Document98 pages725 Intro-F12Mahaboob SubahanNo ratings yet

- Low-Loss, Broadly-Tunable Cavity Filter Operating at UHF FrequenciesDocument4 pagesLow-Loss, Broadly-Tunable Cavity Filter Operating at UHF FrequenciesDo SonNo ratings yet

- Complete Design of A Microstrip Line CouplerDocument6 pagesComplete Design of A Microstrip Line CouplerJoe MullerNo ratings yet

- Intro To Comms With Ni UsrpDocument156 pagesIntro To Comms With Ni UsrpAnonymous 4bUl7jzGq100% (1)

- Direction of Arrival Estimation Using MUSIC AlgorithmDocument14 pagesDirection of Arrival Estimation Using MUSIC AlgorithmilgisizalakasizNo ratings yet

- Slot Antenna: A Radiator Made By Cutting A SlotDocument9 pagesSlot Antenna: A Radiator Made By Cutting A SlotMarcos Marcelon Alcantara Abueva IIINo ratings yet

- Wearable Textile Antennas Examining The Effect of Bending On Their PerformanceDocument6 pagesWearable Textile Antennas Examining The Effect of Bending On Their PerformanceKhaleda AliNo ratings yet

- Translation Radio Direction Finding PDFDocument73 pagesTranslation Radio Direction Finding PDFKevin WoodNo ratings yet

- Group Report Arduino Radar ShieldDocument12 pagesGroup Report Arduino Radar ShieldMustafa PehlivanNo ratings yet

- Digital Phased Arrays ChallangesDocument17 pagesDigital Phased Arrays ChallangesVivek KadamNo ratings yet

- Real Time Implementation of Adaptive Beam Former For Phased Array Radar Over DSP KitDocument10 pagesReal Time Implementation of Adaptive Beam Former For Phased Array Radar Over DSP KitAI Coordinator - CSC JournalsNo ratings yet

- Spectrum Sensing and Blind Automatic Modulation Classification in Real TimeDocument75 pagesSpectrum Sensing and Blind Automatic Modulation Classification in Real TimeHamidNo ratings yet

- Linear Technology-Understanding IP2 and IP3 Issues in Direct Conversion Receivers For WCDMA Wide Area BasestationsDocument5 pagesLinear Technology-Understanding IP2 and IP3 Issues in Direct Conversion Receivers For WCDMA Wide Area BasestationsMichael GrahamNo ratings yet

- Direction Finding PresentationDocument35 pagesDirection Finding PresentationFoolraserNo ratings yet

- MIMO Signal Processing ConsiderationsDocument4 pagesMIMO Signal Processing Considerationsfiqur1No ratings yet

- Mti Radar PDFDocument102 pagesMti Radar PDFHưng Nguyễn ĐìnhNo ratings yet

- 2X8 Multilayer Microstrip Patch Array AntennaDocument12 pages2X8 Multilayer Microstrip Patch Array AntennazfliezblogspotcomNo ratings yet

- OFDM Basics TutorialDocument3 pagesOFDM Basics Tutorialhisoni85No ratings yet

- Radar Data and Relationships: Radar Bands Linear DB ScaleDocument2 pagesRadar Data and Relationships: Radar Bands Linear DB ScaleSusana RojasNo ratings yet

- Radar 2009 A - 11 Waveforms and Pulse CompressionDocument58 pagesRadar 2009 A - 11 Waveforms and Pulse Compressionkamal__singhNo ratings yet

- SARDocument204 pagesSARArash MazandaraniNo ratings yet

- Digital Communication - CioffiDocument101 pagesDigital Communication - CioffiLuigi LuongoNo ratings yet

- Introduction To RadarMWJDocument52 pagesIntroduction To RadarMWJTeddy112No ratings yet

- HFSS Spiral InductorDocument56 pagesHFSS Spiral Inductora3_productNo ratings yet

- Ime-To-Igital - Onverter: 28 January 2014 Document-No: AN034 - en - PDF V1.3Document28 pagesIme-To-Igital - Onverter: 28 January 2014 Document-No: AN034 - en - PDF V1.3AbdullahNo ratings yet

- Ultra Wide BandDocument34 pagesUltra Wide Bandapi-19937584No ratings yet

- Infinitesimal Dipole Antennas2Document35 pagesInfinitesimal Dipole Antennas2Anonymous XV3SIjz8bNo ratings yet

- P-I-N Diode HandbookDocument137 pagesP-I-N Diode HandbookChangjian LiNo ratings yet

- Fractal-based quad-band antenna loaded with L-shaped slot and metamaterialDocument19 pagesFractal-based quad-band antenna loaded with L-shaped slot and metamaterialViswa GopalNo ratings yet

- Understanding Phase Locked Dro Design AspectsDocument8 pagesUnderstanding Phase Locked Dro Design AspectsWill ChangNo ratings yet

- FEKO User ManualDocument446 pagesFEKO User ManualsalehgazyNo ratings yet

- Evaluation of Transmit Diversity in MIMO-radar Direction FindingDocument21 pagesEvaluation of Transmit Diversity in MIMO-radar Direction Findingpadroking11No ratings yet

- جزوه درس رادارDocument121 pagesجزوه درس رادارbahram bahramiNo ratings yet

- Implementing Embedded Multi-Target TrackingDocument7 pagesImplementing Embedded Multi-Target TrackingqasimNo ratings yet

- Design of FMCW Radars For Active Safety Applications PDFDocument5 pagesDesign of FMCW Radars For Active Safety Applications PDFAnonymous LoJy6ERXdNo ratings yet

- High Range-Resolution TechniquesDocument54 pagesHigh Range-Resolution TechniquesZamanundaIEEENo ratings yet

- Multi Radar Tracker MRTDocument4 pagesMulti Radar Tracker MRTZayd Iskandar Dzolkarnain Al-HadramiNo ratings yet

- Communications Receivers DSP Software Radios and Design PDFDocument2 pagesCommunications Receivers DSP Software Radios and Design PDFSeanNo ratings yet

- Models - Rf.circular Waveguide FilterDocument10 pagesModels - Rf.circular Waveguide FilterDr-Mandeep SinghNo ratings yet

- Optimum Array Processing: Part IV of Detection, Estimation, and Modulation TheoryFrom EverandOptimum Array Processing: Part IV of Detection, Estimation, and Modulation TheoryNo ratings yet

- Electrical Overstress (EOS): Devices, Circuits and SystemsFrom EverandElectrical Overstress (EOS): Devices, Circuits and SystemsNo ratings yet

- High Efficiency RF and Microwave Solid State Power AmplifiersFrom EverandHigh Efficiency RF and Microwave Solid State Power AmplifiersRating: 1 out of 5 stars1/5 (1)

- Understanding UMTS Radio Network Modelling, Planning and Automated Optimisation: Theory and PracticeFrom EverandUnderstanding UMTS Radio Network Modelling, Planning and Automated Optimisation: Theory and PracticeMaciej NawrockiNo ratings yet

- Smart Material Systems and MEMS: Design and Development MethodologiesFrom EverandSmart Material Systems and MEMS: Design and Development MethodologiesNo ratings yet

- ZedBoard GSwEL GuideDocument12 pagesZedBoard GSwEL Guidevaibhawamishra32No ratings yet

- Digital Systems Design Using VHDLDocument476 pagesDigital Systems Design Using VHDLImran BashaNo ratings yet

- VHDL FirDocument21 pagesVHDL FirSiva ChaitanyaNo ratings yet

- Dev RefDocument417 pagesDev Refvaibhawamishra32No ratings yet

- Gerber AltiumDocument10 pagesGerber Altiumvaibhawamishra32No ratings yet

- Classa 20wcu2n3055Document6 pagesClassa 20wcu2n3055Constantin CatalinNo ratings yet

- Cifra Club - Justin Timberlake - Can't Stop The FeelingDocument3 pagesCifra Club - Justin Timberlake - Can't Stop The FeelingMateus PavanNo ratings yet

- RFID Based Book Shelving SystemDocument5 pagesRFID Based Book Shelving SystemSunil HalkatiNo ratings yet

- Design of UG Pits & Sumps - FinalDocument30 pagesDesign of UG Pits & Sumps - FinalARAVINDRAJ V RNo ratings yet

- Kabalikat TEN CODESDocument1 pageKabalikat TEN CODESآكوجوي63% (8)

- Knocking On Heaven's DoorDocument1 pageKnocking On Heaven's DoortubbypandaNo ratings yet

- Study On Customer Retention by Indian Shopping MallsDocument63 pagesStudy On Customer Retention by Indian Shopping Mallsx2et020% (1)

- Al Jarreau We Re in This Love Together Score Tabs ChordsDocument4 pagesAl Jarreau We Re in This Love Together Score Tabs ChordsRon MasisNo ratings yet

- P.E.2 Rhythmic Activities Definition of Terms:: Physical Reaction To Rhythm or MusicDocument5 pagesP.E.2 Rhythmic Activities Definition of Terms:: Physical Reaction To Rhythm or MusicAngel Chane OstrazNo ratings yet

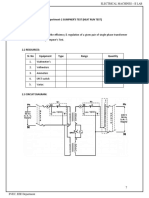

- 2.sumpner's Test On A Pair of Single Phase TransformersDocument5 pages2.sumpner's Test On A Pair of Single Phase Transformerschandrakanth100% (2)

- Grupo 15 - AA1Document3 pagesGrupo 15 - AA1LIRLLEY JHADE CISNEROS PALACIOSNo ratings yet

- Music Express Age 5-6 GLOSSARYDocument1 pageMusic Express Age 5-6 GLOSSARYLouieIsmaelNo ratings yet

- AlankaaramsDocument3 pagesAlankaaramsAnonymous UJFK2jk5g100% (1)

- Itsumo Nando Demo: PianoDocument5 pagesItsumo Nando Demo: PianoKaustubh RaneNo ratings yet

- English AssignmentDocument16 pagesEnglish AssignmentYuliaPholepellLouiwisNo ratings yet

- System Information ReportDocument11 pagesSystem Information ReportMalik FaisalNo ratings yet

- Detroit Red WingsDocument3 pagesDetroit Red WingsYaasheikh PdmNo ratings yet

- Skripta I Revised NEWDocument72 pagesSkripta I Revised NEWNina Iris SekulovićNo ratings yet

- Dancing in The Moonlight - Saxophone Quartet-Soprano SaxophoneDocument2 pagesDancing in The Moonlight - Saxophone Quartet-Soprano SaxophoneJoão SalcedasNo ratings yet

- Class D Amplifier DesignDocument3 pagesClass D Amplifier DesignkovachjkNo ratings yet

- Analysis of Experimental Dynamic Soil-Pile Interaction by Approximate Numerical SolutionsDocument10 pagesAnalysis of Experimental Dynamic Soil-Pile Interaction by Approximate Numerical SolutionsMohamed MamdohNo ratings yet

- DV-260-S DVD Player Service Manual SectionsDocument90 pagesDV-260-S DVD Player Service Manual SectionsJhefone Neira VelasquezNo ratings yet

- 0262 - God of Carnage ScriptDocument25 pages0262 - God of Carnage Scriptpaul50% (2)

- Rep Assessment RubricDocument2 pagesRep Assessment Rubricapi-350015368No ratings yet

- Repertorio Cuarteto de CuerdasDocument9 pagesRepertorio Cuarteto de CuerdasMariano BassaniNo ratings yet

- 129 Gloria, Ehre Sei GottDocument1 page129 Gloria, Ehre Sei GottMartin JessernigNo ratings yet

- IMSLP558076-PMLP4595-Mozart-Horn Concerto K495-Horn in Fa PDFDocument5 pagesIMSLP558076-PMLP4595-Mozart-Horn Concerto K495-Horn in Fa PDFMatheus BarcielaNo ratings yet

- Sunflower - Post Malone Swae LeeDocument3 pagesSunflower - Post Malone Swae LeeAngela Hall100% (1)

- Lussy - A Short Treatise On Musical Rhythm-RedDocument93 pagesLussy - A Short Treatise On Musical Rhythm-RedianchulapaNo ratings yet

- 01 - TER36075 - V3.1 SG English Ed1Document892 pages01 - TER36075 - V3.1 SG English Ed1SergeyNo ratings yet