Professional Documents

Culture Documents

8255

Uploaded by

shrusuprOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8255

Uploaded by

shrusuprCopyright:

Available Formats

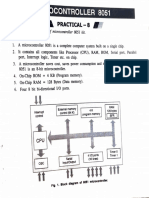

XF8255 Programmable Peripheral

Interface

September 16, 1999 Product Specification

AllianceCORE™ Facts

Core Specifics

Device Family XC4000E/XL Spartan

CLBs Used

Core 64 64

7810 South Hardy Drive, Suite 104 Core +Ext logic 64 64

Tempe, Arizona 85284 USA

Core I/O

Phone: +1 888-845-5585 (USA)

Core1 97 97

+1 480-753-5585

Core +Ext logic 38 38

Fax: +1 480-753-5899

E-mail: info@memecdesign.com System Clock fmax No External Clock2

URL: www.memecdesign.com Device Features Tbufs, global clock buffers,

Used input latches

Features Provided with Core

• Compatible with Xilinx CORE Generator tool Documentation Users guide, application notes

• Software and function compatible with Industry implementation instructions

Standard 8255 Design File Formats .ngo netlist

• 24 programmable I/O pins Viewlogic source files (schematics)

• Fully compatible with most microprocessor families available extra

• Direct bit set/reset capability easing control application Constraint Files .ucf

interface Verification Tool Machine-readable simulation

vectors for ViewLogic ViewSim,

Applications Testbenches for VHDL and Verilog

• Embedded Microprocessor Control Symbols ViewLogic, Foundation,

VHDL, Verilog

General Description Evaluation Model None

The XF8255 Programmable Peripheral Interface Core is a Reference designs & Sample designs in Viewlogic, Foun-

general purpose programmable I/O device designed for application notes dation, VHDL and Verilog

use with most microprocessors. It has 24 I/O pins which Additional Items Warranty by MDS,

may be individually programmed in two groups of 12 and netlist only version available on

used in three major modes of operation. enCORE CD-ROM

The first mode, MODE 0, is basic input/output operation Design Tool Requirements

where ports A and B are 8 bits wide and Port C is split into Xilinx Core Tools Alliance/Foundation 1.4

upper and lower halves of 4 bits each. Port A, Port B, Port C Support

upper, and Port C lower can each be independently config- Support provided by Memec Design Services.

ured as input or output. This gives a total of 16 direction

Notes:

combinations.In MODE 1 each group may be programmed

to have eight lines of input or output. Of the remaining four 1. Assuming all core signals are routed off-chip.

2. Function does not have a clock, but will, at a minimum, perform

pins, three are used for handshaking and interrupt control no wait-state operation alongside an 8 MHz 80C86.

signals. The third mode of operation, MODE 2, is only avail-

able on the Group A ports (Port A and Port C upper). It is a

bi-directional bus mode that uses eight lines for a bi-direc-

tional bus, and five lines (borrowing one from the other

group) for handshaking and interrupt control signals.

September 16, 1999 1

XF8255 Programmable Peripheral Interface

OBUFT DO(7:0)

DIO(7:0)

DI(7:0)

I/O Pad PAT

DATA BUS Port A (7:0)

TRANSFER PAO(7:0) Output Tri-State Buffer

I/O Pad

Group A PAI(7:0) Input Buffer

OE_L Group A Port A

Control (8) PAIQ(7:0)

INPUT

INPUT

LATCH

LATCH

PCT(7:4)

Port C (7:4)

PCO(7:4) Output Tri-State Buffer

I/O Pad

Group A

Port C

Upper PCI(7:4)

(4) Input Buffer

Input

RD_L_P Buffer PCI(3:0) Input Buffer

RD_L

I Pad Group B

BUFG

WCLK Port C

Read/ Lower Port C (3:0)

PCO(3:0)

WR_L_P WR_L

Write (4)

Control I/O Pad

I Pad Output Tri-State Buffer

Logic

A(1:0)_P

PCT(3:0)

A(1:0)

I Pad

PBIQ(7:0) INPUT

CS_L_P INPUT

LATCH

CS_L

I Pad Group B LATCH

Group B

Control Port B PBI(7:0) Input Buffer

(8) Port B (7:0)

RESET_P

RESET

I/O Pad

I Pad PBO(7:0) Output Tri-State Buffer

PBT

x8799

Figure 1: XF8255 Block Diagram

MDS cores are designed with the philosophy that no global the functionality. This datasheet describes both the core

elements should be embedded within the core itself. Global and the supplied external logic.

elements include any of the following components: STAR-

TUP, STARTBUF, BSCAN, READBACK, Global Buffers, Functional Description

Fast Output Primitives, IOB Elements, Clock Delay Compo- The XF8255 is partitioned into modules as shown in Figure

nents, and any of the Oscillator Macros. MDS cores only 1 and described below.

contain resources present in the CLB array. This is done to

allow flexibility in using the cores with other logic. For Read/Write Control Logic

instance, if a global clock buffer is embedded within the

core, but some external logic also requires that same clock, This logic manages all of the internal and external transfers

then an additional global buffer would have to be used. of both Data and Control or Status words.

In any instance where one of our cores generates a clock, Group A and Group B Controls

that signal is brought out of the core, then run through a

The system software programs the functional configuration

global buffer, then brought back into the core. This philoso-

of each port. Each of the Control blocks (Group A and

phy allows external logic to use that clock without using

Group B) accepts “commands” from the Read/Write Con-

another global buffer.

trol Logic, receives “control words” from the internal data

A result of this design philosophy is that the cores are not bus, and issues the proper commands to its associated

self-contained. External logic must be connected to the ports.

core in order to complete it. MDS cores include tested sam-

• Control Group A - Port A and Port C upper (C7 – C4)

ple designs that add the external logic required to complete

• Control Group B - Port B and Port C lower (C3 – C0)

2 September 16, 1999

Memec Design Services

The control word register can be both written and read. Pinout

When the control word is read, bit D7 will always be logic

“1”, as this implies control word mode information. The XF8255 may be implemented as stand-alone logic

using the provided sample designs or may be implemented

Port A: internally with the user’s design. Both versions are included

with the Core deliverables. Signal names are provided in

One 8-bit data output latch/buffer and one 8-bit data input

the block diagram shown in Figure 1, and Table 1.

latch.

Port B: Core Assumptions

One 8-bit data input/output latch/buffer and one 8-bit data Bus-Hold Capability

input buffer.

Ports A, B, and C do not have Bus-Hold capability. This

Port C: would require two OBUFTs per port pin. Since Xilinx

One 8-bit data output latch/buffer and one 8-bit data input devices only have one OBUFT per pin, it would take two Xil-

buffer (no latch for input). This port can be divided into two inx pins connected together externally for each port pin.

4-bit ports under the mode control. Workaround: Most applications don't require Bus-Hold

Each 4-bit port contains a 4-bit latch and it can be used for capability, but for those that do, a customized version of the

the control signal outputs and status signal inputs in con- XF8255 core can be developed.

junction with ports A and B.

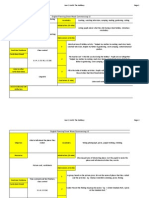

Table 1: Core Signal Pinout

Signal

Signal Description

Direction

DI[7:0] Input Data bus input.

DO[7:0] Output Data bus output.

RESET Input RESET: A high on this input clears the control register and all ports (A, B, C) are set to

the input mode.

CS_L Input CHIP SELECT: An active low input used to enable the XF8255 onto the data bus for

CPU communications.

RD_L Input READ: Read is an active low input control signal used by the CPU to read status infor-

mation or data via the data bus.

WR_L Input WRITE: Write does the CPU to load control words and data into the XF8255 use an

active low input control signal.

WCLK Input Write clock. This is the clock input to all clock registers. It is usually sourced from a glo-

bal clock buffer (BUFG).

A[1:0] Input PORT ADDRESS: These input signals, in conjunction with the RD_L and WR_L inputs,

control the selection of the three ports or the control word register. A0 and A1 are nor-

mally connected to the least significant bits of the address bus A0, A1.

PAI[7:0] Input Port A 8-bit input buffer.

PAO[7:0] Output Port A output register

These four signals comprise Port A

PAIQ[7:0] Input Port A 8-bit input latch.

PAT Output Port A output enable.

PBI[7:0] Input Port B 8-bit input buffer.

PBO[7:0] Output Port B output register.

These four signals comprise Port B

PBIQ[7:0] Input Port B 8-bit input latch.

PBT Output Port B output enable.

PCI[7:0] Input Port C 8-bit input.

PCO[7:0] Output Port C 8-bit Output register. These three signals comprise Port C

PCT[7:0] Output Port C 8-bit output enables.

September 16, 1999 3

XF8255 Programmable Peripheral Interface

Core Modifications any other third-party right. No license is granted by implica-

tion or otherwise under any patent or patent rights of

The XF8255 is designed to meet or exceed the AC Specifi- Memec Design Services.

cations of the industry standard 8255. However, in most

cases the Timespecs can be tightened significantly. In all Memec Design Services products are not intended for use

cases, a post-route timing analysis should be performed to in life support appliances, devices, or systems. Use of a

verify performance. Implementation and other customizing Memec Design Services product in such application with-

is available through Memec Design Services. out the written consent of the appropriate Memec Design

Services officer is prohibited.

Verification Methods All trademarks, registered trademarks, or servicemarks are

Complete functional and timing simulation has been per- property of their respective owners.

formed on the XF8255 using ViewSim ModelSim – VHDL,

Silos3 - Verilog. (Simulation vectors used for verification are Related Information

provided with the core.)

Xilinx Programmable Logic

Recommended Design Experience For information on Xilinx programmable logic or develop-

ment system software, contact your local Xilinx sales office,

For the source version, users should be familiar with View-

or:

Logic Workview Office schematic entry and Xilinx design

flows. For the netlist version, users should be familiar with Xilinx, Inc.

Workview office, Xilinx Foundation, Verilog simulation/syn- 2100 Logic Drive

thesis or VHDL simulation/synthesis. San Jose, CA 95124

Phone: +1 408-559-7778

Users should also have experience with microprocessor

Fax: +1408-559-7114

systems.

URL: www.xilinx.com

Additional Support For general Xilinx literature, contact:

Memec Design Services supplies a Xilinx-based FPGA Phone: +1 800-231-3386 (inside the US)

Development Module that can be used to hardware test this +1 408-879-5017 (outside the US)

and other MDS cores. To purchase this, or obtain more E-mail: literature@xilinx.com

information, contact MDS directly. TM

For AllianceCORE specific information, contact:

Ordering Information Phone: +1 408-879-5381

E-mail: alliancecore@xilinx.com

The XF8255 Programmable Peripheral Interface Core is

URL: www.xilinx.com/products/logicore

provided under license from Memec Design Services for /alliance/tblpart.htm

use in Xilinx programmable logic devices and Xilinx Hard-

Wire gate arrays. Please contact MDS for pricing and more

information.

Information furnished by Memec Design Services is

believed to be accurate and reliable. Memec Design Ser-

vices reserves the right to change specifications detailed in

this data sheet at any time without notice, in order to

improve reliability, function or design, and assumes no

responsibility for any errors within this document. Memec

Design Services does not make any commitment to update

this information.

Memec Design Services assumes no obligation to correct

any errors contained herein or to advise any user of this

text of any correction, if such be made, nor does the Com-

pany assume responsibility for the functioning of unde-

scribed features or parameters. Memec Design Services

will not assume any liability for the accuracy or correctness

of any support or assistance provided to a user.

Memec Design Services does not represent that products

described herein are free from patent infringement or from

4 September 16, 1999

You might also like

- 8085 - Study Material PDFDocument86 pages8085 - Study Material PDFshubhamNo ratings yet

- MW - DVB-T/H - P DVB Terrestrial/Handheld Modulator CoreDocument7 pagesMW - DVB-T/H - P DVB Terrestrial/Handheld Modulator Corepangeran_avicNo ratings yet

- Real-Time Labview Platform: Technical DocumentationDocument20 pagesReal-Time Labview Platform: Technical Documentationmetidji brahimNo ratings yet

- PB Aes z7pzsdr Ad9361 Som G v1Document2 pagesPB Aes z7pzsdr Ad9361 Som G v1Rakesh KhannaNo ratings yet

- Ultra-Low Power Single-Chip USB 2.0 To 10/100M Ethernet ControllerDocument16 pagesUltra-Low Power Single-Chip USB 2.0 To 10/100M Ethernet ControllereugeneNo ratings yet

- MTS-86C 10102Document1 pageMTS-86C 10102Tinsae HailuNo ratings yet

- PCF 8574 ADocument38 pagesPCF 8574 ADilu_VarmaNo ratings yet

- PCF8574A Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionDocument38 pagesPCF8574A Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionmercyjohnNo ratings yet

- A29l160atv 70FDocument42 pagesA29l160atv 70Farond5318No ratings yet

- Architecture OF MC-1Document33 pagesArchitecture OF MC-1Unique ProNo ratings yet

- Microcontroller Exp To Write 6 To 8Document12 pagesMicrocontroller Exp To Write 6 To 8ee210150900103No ratings yet

- System Overview and ArchitectureDocument47 pagesSystem Overview and Architecturesasa hhNo ratings yet

- Batch Weighing MachineDocument21 pagesBatch Weighing MachinePriyansh MehtaNo ratings yet

- Technical Note #19: Tested RS-485 AdaptersDocument3 pagesTechnical Note #19: Tested RS-485 AdaptersbrunotavesNo ratings yet

- Microprocessor Micro Controller TrainerDocument4 pagesMicroprocessor Micro Controller TrainerHOD ECE KNCETNo ratings yet

- Hitachi PLCDocument8 pagesHitachi PLCTeck Soon TeoNo ratings yet

- Microcontroller and Embedded System Designs (EE-328-F) : Lab Manual Vi SemesterDocument43 pagesMicrocontroller and Embedded System Designs (EE-328-F) : Lab Manual Vi SemesterabNo ratings yet

- Product Obsolete or Under Obsolescence: Xc1700E, Xc1700El, and Xc1700L Series Configuration PromsDocument13 pagesProduct Obsolete or Under Obsolescence: Xc1700E, Xc1700El, and Xc1700L Series Configuration PromsLaboratorio GTO Perú S.A.C.No ratings yet

- Eex4436 Assignment 01. 416960756Document18 pagesEex4436 Assignment 01. 416960756RusHan SenavirathnaNo ratings yet

- 8086 AshishDocument57 pages8086 AshishPARASURAM NAIK MNo ratings yet

- P44T en TMDocument728 pagesP44T en TMCjdavies49No ratings yet

- Module 2 AVR ATMega32 ArchitectureDocument44 pagesModule 2 AVR ATMega32 ArchitectureehsanNo ratings yet

- PCF8574 Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionDocument41 pagesPCF8574 Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionAndre BinaknasanaNo ratings yet

- PCF8574 Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 DescriptionDocument41 pagesPCF8574 Remote 8-Bit I/O Expander For I C Bus: 2 1 Features 3 Descriptionzbhp z100% (1)

- Pcf8574 DatasheetDocument44 pagesPcf8574 DatasheetSütő László BalázsNo ratings yet

- Quartus II Training 2Document91 pagesQuartus II Training 2bojan 2No ratings yet

- 8051 MicrocontrollerDocument76 pages8051 MicrocontrollerRohan TomarNo ratings yet

- WWW Mikroe Com Chapters View 67 Chapter 4 At89s8253 MicroconDocument51 pagesWWW Mikroe Com Chapters View 67 Chapter 4 At89s8253 Microconramnag4No ratings yet

- Soc Projects in Be-Co: Greg DanilukDocument27 pagesSoc Projects in Be-Co: Greg DanilukLachari AchrafNo ratings yet

- h2hc2014 Reversing Firmware Radare SlidesDocument46 pagesh2hc2014 Reversing Firmware Radare SlidesntcaseNo ratings yet

- The 8051 ArchitectureDocument80 pagesThe 8051 ArchitectureManoj GadgeNo ratings yet

- Quartus II TrainingDocument91 pagesQuartus II TrainingRodrigo CorreaNo ratings yet

- Max 4 Max 41103016080000 13130251 002 Elau ManualDocument22 pagesMax 4 Max 41103016080000 13130251 002 Elau ManualLyes TAGGUEBNo ratings yet

- BGC-8088 Microengineer SpecificationDocument2 pagesBGC-8088 Microengineer SpecificationJarinNo ratings yet

- stand-IO EDocument14 pagesstand-IO EAtaNo ratings yet

- Intel (Microprocessor)Document8 pagesIntel (Microprocessor)Anirudh KhattriNo ratings yet

- LAB1Document42 pagesLAB1farheen khosoNo ratings yet

- Seminar ON Embedded SystemDocument35 pagesSeminar ON Embedded SystemDivanshu Mahajan0% (1)

- I2C To Parallel Port Converter For 7-Segment Interface Pcf8574Document36 pagesI2C To Parallel Port Converter For 7-Segment Interface Pcf8574DHANAPRAKAASHNo ratings yet

- Altera Epf8282alc84 4Document62 pagesAltera Epf8282alc84 4lim hyNo ratings yet

- Atmel 42005 8 and 16 Bit AVR Microcontrollers XMEGA E ManualDocument447 pagesAtmel 42005 8 and 16 Bit AVR Microcontrollers XMEGA E ManualpapuaoshiNo ratings yet

- Io System Irc5Document24 pagesIo System Irc5Kristal NewtonNo ratings yet

- FPGA: FPGA Digital Circuit Design Trainer Based Altera/XilinxDocument4 pagesFPGA: FPGA Digital Circuit Design Trainer Based Altera/Xilinx임영준No ratings yet

- B35apo - Lecture07 Io 1Document122 pagesB35apo - Lecture07 Io 1dukeNo ratings yet

- 01-09 System DescriptionDocument19 pages01-09 System Description46zct9bzh9No ratings yet

- USER MANUAL Mab - 51Document93 pagesUSER MANUAL Mab - 51Pushpinder Singh KhalsaNo ratings yet

- And The For Reference.: 16 Mbit (2 M X 8-Bit/1 M X 16-Bit), 3 V Boot Sector FlashDocument53 pagesAnd The For Reference.: 16 Mbit (2 M X 8-Bit/1 M X 16-Bit), 3 V Boot Sector FlashRepararelcd LcdNo ratings yet

- ds030 Fadec 011323Document2 pagesds030 Fadec 011323hamid mirNo ratings yet

- 3350-1 DS 20210720-DatasheetDocument16 pages3350-1 DS 20210720-Datasheetfernando david diaz ruiz diazNo ratings yet

- Avr A & A: Rchitecture SsemblyDocument45 pagesAvr A & A: Rchitecture SsemblyFengxing ZhuNo ratings yet

- 89s51 DatasheetDocument27 pages89s51 DatasheetazizboysNo ratings yet

- Programmable Logic Controller: Six Weeks Industrial Training in Automation Systems From Sofcon (Bhopal)Document19 pagesProgrammable Logic Controller: Six Weeks Industrial Training in Automation Systems From Sofcon (Bhopal)Kapil SinghNo ratings yet

- PLC Presentation NewDocument27 pagesPLC Presentation Newgautamjoshi83% (6)

- VC19PDFDocument1 pageVC19PDFevasiveNo ratings yet

- DataSheet ERTEC200P-2 V1 0Document80 pagesDataSheet ERTEC200P-2 V1 0dupirulitoNo ratings yet

- Part 1 PIC Microcontroller SystemsDocument30 pagesPart 1 PIC Microcontroller SystemsSashikanth BethaNo ratings yet

- 8255 ReportDocument12 pages8255 Reportapi-26100966No ratings yet

- Embedded Controller Forth For The 8051 FamilyFrom EverandEmbedded Controller Forth For The 8051 FamilyRating: 4 out of 5 stars4/5 (1)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Handout Pragmatics w05Document2 pagesHandout Pragmatics w05Sara EldalyNo ratings yet

- IO Planning in EDI Systems: Cadence Design Systems, IncDocument13 pagesIO Planning in EDI Systems: Cadence Design Systems, Incswams_suni647No ratings yet

- 300 Young AmyDocument7 pages300 Young Amyd4n_c4rl0No ratings yet

- ProxSafe Flexx16 ModuleDocument20 pagesProxSafe Flexx16 ModuleChristophe DerenneNo ratings yet

- Second Language Acquisition (SLA)Document28 pagesSecond Language Acquisition (SLA)man_dainese96% (26)

- Year 3 Unit 9 The HolidaysDocument8 pagesYear 3 Unit 9 The HolidaysmofardzNo ratings yet

- Curious George Thinking - Cerca Con GoogleDocument1 pageCurious George Thinking - Cerca Con GoogleAnna De BiaseNo ratings yet

- Dm00154093 Description of Stm32f1 Hal and Low Layer Drivers StmicroelectronicsDocument1,208 pagesDm00154093 Description of Stm32f1 Hal and Low Layer Drivers StmicroelectronicsGia Bảo DươngNo ratings yet

- Diagnostic Test ENGLISH 4Document3 pagesDiagnostic Test ENGLISH 4leigh olarte100% (1)

- INetsim SetupDocument13 pagesINetsim SetupNguyen HoangNo ratings yet

- Ccna Lab ManualDocument109 pagesCcna Lab ManualJoemon Jose100% (8)

- A Software For S-Box Performance Analysis and TestDocument4 pagesA Software For S-Box Performance Analysis and TestAgustin Aboytes100% (1)

- Muestra Eyes Open 4 WBDocument7 pagesMuestra Eyes Open 4 WBclau aNo ratings yet

- Day 1 Article WordlistDocument3 pagesDay 1 Article WordlistZulkhumor SattarovaNo ratings yet

- Grade 7 Supply List (SY1314)Document1 pageGrade 7 Supply List (SY1314)International School ManilaNo ratings yet

- Telc English b2-c1 BusinessDocument56 pagesTelc English b2-c1 BusinessTikiNo ratings yet

- WMF3 0 RC Release NotesDocument18 pagesWMF3 0 RC Release NotesTI09No ratings yet

- Assessment Portfolio Edci 3482Document6 pagesAssessment Portfolio Edci 3482api-437180364No ratings yet

- Śivāgamādimāhātmyasa Graha of Śālivā I JñānaprakāśaDocument111 pagesŚivāgamādimāhātmyasa Graha of Śālivā I JñānaprakāśasiddhantaNo ratings yet

- Template For 5 Paragraph EssayDocument11 pagesTemplate For 5 Paragraph EssayAaron GaluraNo ratings yet

- PC GSGDocument78 pagesPC GSGEima Siti NurimahNo ratings yet

- Learning Languages: Language QuizDocument4 pagesLearning Languages: Language QuizDRAGANA ĐORĐEVIĆNo ratings yet

- The Twofish Encryption AlgorithmDocument5 pagesThe Twofish Encryption AlgorithmMaysam AlkeramNo ratings yet

- Using ArchiMate To Represent ITIL MetamodelDocument6 pagesUsing ArchiMate To Represent ITIL Metamodelcgarciahe5427No ratings yet

- Imong Mama Tekstong ImpormatiboDocument6 pagesImong Mama Tekstong ImpormatiboJonel MagallanesNo ratings yet

- Lecture # 3 Insert Tab: Groups & Commands: FEBRUARY 13, 2017Document34 pagesLecture # 3 Insert Tab: Groups & Commands: FEBRUARY 13, 2017Mary Jane Blanco FioNo ratings yet

- Tarea - Activated #2Document2 pagesTarea - Activated #2Jhon Pertuz Celin100% (3)

- 46 - Shadrach, Meshach, and AbednegoDocument16 pages46 - Shadrach, Meshach, and Abednegobejja1613No ratings yet

- Build - Grow Grammar Space Beginner 3 WB KEYDocument23 pagesBuild - Grow Grammar Space Beginner 3 WB KEYSelin KozağaçNo ratings yet

- Grammar, Chapter 10 The SentenceDocument10 pagesGrammar, Chapter 10 The SentencepiaNo ratings yet