Professional Documents

Culture Documents

Fds4435Bz: P-Channel Powertrench Mosfet

Uploaded by

Kevin TateOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fds4435Bz: P-Channel Powertrench Mosfet

Uploaded by

Kevin TateCopyright:

Available Formats

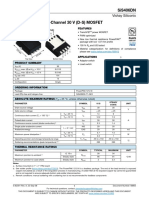

FDS4435BZ P-Channel PowerTrench® MOSFET

June 2007

FDS4435BZ

P-Channel PowerTrench® MOSFET

-30V, -8.8A, 20mΩ

Features General Description

Max rDS(on) = 20mΩ at VGS = -10V, ID = -8.8A This P-Channel MOSFET is produced using Fairchild

®

Max rDS(on) = 35mΩ at VGS = -4.5V, ID = -6.7A Semiconductor’s advanced PowerTrench process that has

Extended VGSS range (-25V) for battery applications been especially tailored to minimize the on-state resistance.

HBM ESD protection level of ±3.8KV typical (note 3) This device is well suited for Power Management and load

High performance trench technology for extremely low rDS(on) switching applications common in Notebook Computers and

High power and current handling capability Portable Battery Packs.

Termination is Lead-free and RoHS compliant

D

D

D D 5 4 G

D

D 6 3 S

D 7 2 S

G

S

S D 8 1 S

Pin 1 S

SO-8

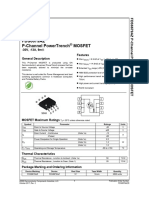

MOSFET Maximum Ratings TA = 25°C unless otherwise noted

Symbol Parameter Ratings Units

VDS Drain to Source Voltage -30 V

VGS Gate to Source Voltage ±25 V

Drain Current -Continuous TA = 25°C (Note 1a) -8.8

ID A

-Pulsed -50

Power Dissipation TA = 25°C (Note 1a) 2.5

PD W

Power Dissipation TA = 25°C (Note 1b) 1.0

EAS Single Pulse Avalanche Energy (Note 4) 24 mJ

TJ, TSTG Operating and Storage Junction Temperature Range -55 to +150 °C

Thermal Characteristics

RθJC Thermal Resistance, Junction to Case 25

°C/W

RθJA Thermal Resistance, Junction to Ambient (Note 1a) 50

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

FDS4435BZ FDS4435BZ SO-8 13’’ 12mm 2500units

©2007 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDS4435BZ Rev.C

FDS4435BZ P-Channel PowerTrench® MOSFET

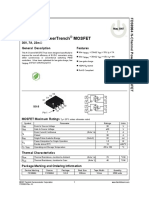

Electrical Characteristics TJ = 25°C unless otherwise noted

Symbol Parameter Test Conditions Min Typ Max Units

Off Characteristics

BVDSS Drain to Source Breakdown Voltage ID = -250µA, VGS = 0V -30 V

∆BVDSS Breakdown Voltage Temperature

ID = -250µA, referenced to 25°C -21 mV/°C

∆TJ Coefficient

IDSS Zero Gate Voltage Drain Current VDS = -24V, VGS = 0V 1 µA

IGSS Gate to Source Leakage Current VGS = ±25V, VDS = 0V ±10 µA

On Characteristics

VGS(th) Gate to Source Threshold Voltage VGS = VDS, ID = -250µA -1 -2.1 -3 V

∆VGS(th) Gate to Source Threshold Voltage

ID = -250µA, referenced to 25°C 6 mV/°C

∆TJ Temperature Coefficient

VGS = -10V, ID = -8.8A 16 20

rDS(on) Static Drain to Source On Resistance VGS = -4.5V, ID = -6.7A 26 35 mΩ

VGS = -10V, ID = -8.8A, TJ = 125°C 22 28

gFS Forward Transconductance VDS = -5V, ID = -8.8A 24 S

Dynamic Characteristics

Ciss Input Capacitance 1385 1845 pF

VDS = -15V, VGS = 0V,

Coss Output Capacitance 275 365 pF

f = 1MHz

Crss Reverse Transfer Capacitance 230 345 pF

Rg Gate Resistance f = 1MHz 4.5 Ω

Switching Characteristics

td(on) Turn-On Delay Time 10 20 ns

VDD = -15V, ID = -8.8A,

tr Rise Time 6 12 ns

VGS = -10V, RGEN = 6Ω

td(off) Turn-Off Delay Time 30 48 ns

tf Fall Time 12 22 ns

Qg Total Gate Charge VGS = 0V to -10V 28 40 nC

VDD = -15V,

Qg Total Gate Charge VGS = 0V to -5V 16 23 nC

ID = -8.8A

Qgs Gate to Source Charge 5.2 nC

Qgd Gate to Drain “Miller” Charge 7.4 nC

Drain-Source Diode Characteristics

VSD Source to Drain Diode Forward Voltage VGS = 0V, IS = -8.8A (Note 2) -0.9 -1.2 V

trr Reverse Recovery Time 29 44 ns

IF = -8.8A, di/dt = 100A/µs

Qrr Reverse Recovery Charge 23 35 nC

NOTES:

1. RθJA is determined with the device mounted on a 1in2 pad 2 oz copper pad on a 1.5 x 1.5 in. board of FR-4 material. RθJC is guaranteed by design while RθCA is determined by

the user's board design.

a. 50°C/W when mounted on b. 125°C/W when mounted on

a 1 in2 pad of 2 oz copper. a minimum pad of 2 oz copper.

2. Pulse Test: Pulse Width < 300µs, Duty cycle < 2.0%.

3. The diode connected between the gate and source serves only as protection against ESD. No gate overvoltage rating is implied.

4. Starting TJ = 25°C, L = 1mH, IAS = -7A, VDD = -30V, VGS = -10V

©2007 Fairchild Semiconductor Corporation 2 www.fairchildsemi.com

FDS4435BZ Rev.C

FDS4435BZ P-Channel PowerTrench® MOSFET

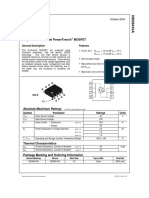

Typical Characteristics TJ = 25°C unless otherwise noted

50 4.0

VGS = -10V PULSE DURATION = 80µs

DRAIN TO SOURCE ON-RESISTANCE

VGS = -3.5V

VGS = -5V 3.5 DUTY CYCLE = 0.5%MAX

40

-ID, DRAIN CURRENT (A)

VGS = -4.5V

3.0

VGS = -4.5V

NORMALIZED

30 2.5

VGS = -4V VGS = -5V

VGS = -4V 2.0

20

VGS = -3.5V 1.5

10 VGS = -10V

PULSE DURATION = 80µs 1.0

DUTY CYCLE = 0.5%MAX

0 0.5

0 1 2 3 4 0 10 20 30 40 50

-VDS, DRAIN TO SOURCE VOLTAGE (V) -ID, DRAIN CURRENT(A)

Figure 1. On-Region Characteristics Figure 2. Normalized On-Resistance

vs Drain Current and Gate Voltage

1.6 60

ID = -8.8A PULSE DURATION = 80µs

DRAIN TO SOURCE ON-RESISTANCE

ID = -8.8A

VGS = -10V DUTY CYCLE = 0.5%MAX

SOURCE ON-RESISTANCE (mΩ)

1.4 50

rDS(on), DRAIN TO

NORMALIZED

1.2 40

TJ = 125oC

1.0 30

0.8 20

TJ = 25oC

0.6 10

-75 -50 -25 0 25 50 75 100 125 150 2 4 6 8 10

TJ, JUNCTION TEMPERATURE ( C) o

-VGS, GATE TO SOURCE VOLTAGE (V)

Figure 3. Normalized On- Resistance Figure 4. On-Resistance vs Gate to

vs Junction Temperature Source Voltage

50 100

PULSE DURATION = 80µs

-IS, REVERSE DRAIN CURRENT (A)

VGS = 0V

DUTY CYCLE = 0.5%MAX

40 10

-ID, DRAIN CURRENT (A)

VDS = -5V 1

30

0.1 TJ = 150oC TJ = 25oC

20

TJ = 150oC 0.01

TJ = -55oC

10

TJ = 25oC 0.001

TJ =-55oC

0 0.0001

1 2 3 4 5 0.0 0.2 0.4 0.6 0.8 1.0 1.2

-VGS, GATE TO SOURCE VOLTAGE (V) -VSD, BODY DIODE FORWARD VOLTAGE (V)

Figure 5. Transfer Characteristics Figure 6. Source to Drain Diode

Forward Voltage vs Source Current

©2007 Fairchild Semiconductor Corporation 3 www.fairchildsemi.com

FDS4435BZ Rev.C

FDS4435BZ P-Channel PowerTrench® MOSFET

Typical Characteristics TJ = 25°C unless otherwise noted

10 4000

-VGS, GATE TO SOURCE VOLTAGE(V)

ID = -8.8A

8 Ciss

VDD = -10V

CAPACITANCE (pF)

6 1000

VDD = -15V VDD = -20V Coss

4

2 Crss

f = 1MHz

VGS = 0V

0 100

0 5 10 15 20 25 30 0.1 1 10 30

Qg, GATE CHARGE(nC) -VDS, DRAIN TO SOURCE VOLTAGE (V)

Figure 7. Gate Charge Characteristics Figure 8. Capacitance vs Drain

to Source Voltage

-4

20 10

VDS = 0V

-Ig, GATE LEAKAGE CURRENT(A)

-IAS, AVALANCHE CURRENT(A)

-5

10 10

TJ = 125oC

-6

10

TJ = 25oC

TJ = 125oC 10

-7

TJ = 25oC

-8

10

-9

1 10

0.01 0.1 1 10 30 0 5 10 15 20 25 30

tAV, TIME IN AVALANCHE(ms) -VGS, GATE TO SOURCE VOLTAGE(V)

Figure 9. Unclamped Inductive Figure 10. Gate Leakage Current vs Gate to

Switching Capability Source Voltage

10 100

-ID, DRAIN CURRENT (A)

8

-ID, DRAIN CURRENT (A)

100us

10

VGS = -10V

1ms

6

1 10ms

VGS = -4.5V THIS AREA IS 100ms

4

LIMITED BY rDS(on)

SINGLE PULSE 1s

0.1 TJ = MAX RATED

2 o

10s

RθJA = 125 C/W DC

o

RθJA = 50 C/W TA = 25oC

0 0.01

25 50 75 100 125 150 0.1 1 10 80

o

TA, AMBIENT TEMPERATURE ( C) -VDS, DRAIN to SOURCE VOLTAGE (V)

Figure 11. Maximum Continuous Drain Figure 12. Forward Bias Safe

Current vs Ambient Temperature Operating Area

©2007 Fairchild Semiconductor Corporation 4 www.fairchildsemi.com

FDS4435BZ Rev.C

FDS4435BZ P-Channel PowerTrench® MOSFET

Typical Characteristics TJ = 25°C unless otherwise noted

100

VGS = -10V FOR TEMPERATURES

P(PK), PEAK TRANSIENT POWER (W)

ABOVE 25oC DERATE PEAK

CURRENT AS FOLLOWS:

150 – T

I = I25

A

------------------------

125

10

TA = 25oC

SINGLE PULSE

RθJA = 125oC/W

1

0.6

-3 -2 -1 0 1 2 3

10 10 10 10 10 10 10

t, PULSE WIDTH (s)

Figure 13. Single Pulse Maximum Power Dissipation

2

DUTY CYCLE-DESCENDING ORDER

1

D = 0.5

NORMALIZED THERMAL

0.2

IMPEDANCE, ZθJA

0.1

0.05

0.02

0.01 PDM

0.1

t1

t2

SINGLE PULSE NOTES:

DUTY FACTOR: D = t1/t2

RθJA = 125oC/W

PEAK TJ = PDM x ZθJA x RθJA + TA

0.01

-3 -2 -1 0 1 2 3

10 10 10 10 10 10 10

t, RECTANGULAR PULSE DURATION (s)

Figure 14. Transient Thermal Response Curve

©2007 Fairchild Semiconductor Corporation 5 www.fairchildsemi.com

FDS4435BZ Rev.C

TRADEMARKS

The following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use and is not

intended to be an exhaustive list of all such trademarks.

ACEx® Green FPS™ Power247® SuperSOT™-8

Build it Now™ Green FPS™ e-Series™ POWEREDGE® SyncFET™

CorePLUS™ GTO™ Power-SPM™ The Power Franchise®

CROSSVOLT™ i-Lo™ PowerTrench®

CTL™ IntelliMAX™ Programmable Active Droop™

Current Transfer Logic™ ISOPLANAR™ QFET® TinyBoost™

EcoSPARK® MegaBuck™ QS™ TinyBuck™

®

MICROCOUPLER™ QT Optoelectronics™ TinyLogic®

Fairchild® MicroFET™ Quiet Series™ TINYOPTO™

Fairchild Semiconductor® MicroPak™ RapidConfigure™ TinyPower™

FACT Quiet Series™ MillerDrive™ SMART START™ TinyPWM™

FACT® Motion-SPM™ SPM® TinyWire™

FAST® OPTOLOGIC® STEALTH™ μSerDes™

FastvCore™ OPTOPLANAR® SuperFET™ UHC®

®

FPS™ SuperSOT™-3 UniFET™

FRFET® PDP-SPM™ SuperSOT™-6 VCX™

Global Power ResourceSM Power220®

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS

HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE

APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS

PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S

WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR

SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support,

which, (a) are intended for surgical implant into the body or device, or system whose failure to perform can be

(b) support or sustain life, and (c) whose failure to perform reasonably expected to cause the failure of the life support

when properly used in accordance with instructions for use device or system, or to affect its safety or effectiveness.

provided in the labeling, can be reasonably expected to

result in a significant injury of the user.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Advance Information Formative or In Design This datasheet contains the design specifications for product

development. Specifications may change in any manner without notice.

Preliminary First Production This datasheet contains preliminary data; supplementary data will be

published at a later date. Fairchild Semiconductor reserves the right to

make changes at any time without notice to improve design.

No Identification Needed Full Production This datasheet contains final specifications. Fairchild Semiconductor

reserves the right to make changes at any time without notice to improve

design.

Obsolete Not In Production This datasheet contains specifications on a product that has been

discontinued by Fairchild Semiconductor. The datasheet is printed for

reference information only.

Rev. I31

© 2007 Fairchild Semiconductor Corporation www.fairchildsemi.com

You might also like

- Fds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesDocument6 pagesFds6679Az P-Channel Powertrench Mosfet: - 30V, - 13A, 9M General Description FeaturesEdgxr DxnielNo ratings yet

- FDS6679AZ DatasheetDocument6 pagesFDS6679AZ DatasheetMarivaldo NascimentoNo ratings yet

- Fdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MDocument5 pagesFdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MKakatuar KakatuaNo ratings yet

- Onsemiconductor Fds6679az Datasheets 0664Document6 pagesOnsemiconductor Fds6679az Datasheets 0664Yohandris FernandezNo ratings yet

- Fdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MDocument5 pagesFdc658Ap: Single P-Channel Logic Level Powertrench Mosfet - 30V, - 4A, 50MfaberjetNo ratings yet

- 294937Document8 pages294937พ่อโกรธ พ่อต้องยิ้มNo ratings yet

- Fds6575 Single P-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6575 Single P-Channel, Logic Level, Powertrench MosfetsilictronicNo ratings yet

- Datasheet - HK Fds9431a10 4643859Document5 pagesDatasheet - HK Fds9431a10 4643859jim campbellNo ratings yet

- FDM S3672Document7 pagesFDM S3672chudungk57No ratings yet

- Fds6680as 106791Document9 pagesFds6680as 106791Mhd DamNo ratings yet

- Fdmc6679Az: P-Channel Powertrench MosfetDocument7 pagesFdmc6679Az: P-Channel Powertrench MosfetMahmoud ElrefaeyNo ratings yet

- 9435GM-P-Channel 30-V (D-S) MOSFETDocument8 pages9435GM-P-Channel 30-V (D-S) MOSFETtsromailNo ratings yet

- N-Channel Powertrench Mosfet: 30V, 8.5A, 23M General Descriptions FeaturesDocument6 pagesN-Channel Powertrench Mosfet: 30V, 8.5A, 23M General Descriptions FeaturesjokophpNo ratings yet

- Onsemi FairchildDocument6 pagesOnsemi Fairchildpratik gautamNo ratings yet

- 4435 FairchildSemiconductorDocument6 pages4435 FairchildSemiconductorYared TarikuNo ratings yet

- P-Channel 30-V (D-S) MOSFET: Features Product SummaryDocument8 pagesP-Channel 30-V (D-S) MOSFET: Features Product SummaryYANISSE BADNo ratings yet

- 2424 FDMS86300Document7 pages2424 FDMS86300Ivkan MarsovskiNo ratings yet

- N-Channel Power Trench Mosfet: Features General DescriptionDocument8 pagesN-Channel Power Trench Mosfet: Features General DescriptionRicardo VieiraNo ratings yet

- Fds8880 N-Channel Powertrench: MosfetDocument12 pagesFds8880 N-Channel Powertrench: MosfetDavid J. Pinto ApazaNo ratings yet

- Fdms7698: N-Channel Powertrench MosfetDocument7 pagesFdms7698: N-Channel Powertrench MosfetAdrian Kim BabelaNo ratings yet

- Fdc642P: Single P-Channel 2.5V Specified Powertrench MosfetDocument5 pagesFdc642P: Single P-Channel 2.5V Specified Powertrench MosfetdistefanoNo ratings yet

- Fds6612A: Single N-Channel, Logic-Level, Powertrench MosfetDocument8 pagesFds6612A: Single N-Channel, Logic-Level, Powertrench MosfetCarlos Manuel PeraltaNo ratings yet

- Fds6676As: 30V N-Channel Powertrench SyncfetDocument8 pagesFds6676As: 30V N-Channel Powertrench SyncfetManuel LeaNo ratings yet

- Fds6681Z: 30 Volt P-Channel Powertrench MosfetDocument6 pagesFds6681Z: 30 Volt P-Channel Powertrench MosfetShamim DhaliNo ratings yet

- Si4413ADY: Vishay SiliconixDocument9 pagesSi4413ADY: Vishay SiliconixShamim DhaliNo ratings yet

- N-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesDocument6 pagesN-Channel Powertrench Mosfet: 30V, 7A, 23M General Description FeaturesLuis CarlosNo ratings yet

- Fds6690As: 30V N-Channel Powertrench SyncfetDocument8 pagesFds6690As: 30V N-Channel Powertrench SyncfetManuel LeaNo ratings yet

- Pin Description Features: Shenzhen Tuofeng Semiconductor Technology Co., LTDDocument8 pagesPin Description Features: Shenzhen Tuofeng Semiconductor Technology Co., LTDDary CalaçaNo ratings yet

- Fdc658P Single P-Channel, Logic Level, Powertrench Mosfet: General Description FeaturesDocument5 pagesFdc658P Single P-Channel, Logic Level, Powertrench Mosfet: General Description Featuresgabriel6276No ratings yet

- Fdn358P: Single P-Channel, Logic Level, Powertrench MosfetDocument5 pagesFdn358P: Single P-Channel, Logic Level, Powertrench MosfetAlex KarimNo ratings yet

- Irf 9410Document7 pagesIrf 9410FaisaludinNo ratings yet

- FDMC7692: N-Channel Power Trench MosfetDocument6 pagesFDMC7692: N-Channel Power Trench MosfetHerdhis VegaNo ratings yet

- General Description Product Summary: 30V P-Channel MOSFETDocument5 pagesGeneral Description Product Summary: 30V P-Channel MOSFETStoica VictorNo ratings yet

- Fairchild - Semiconductor FDMC8884 DatasheetDocument7 pagesFairchild - Semiconductor FDMC8884 DatasheetmirandowebsNo ratings yet

- P-Channel 2.5V Specified Powertrench Mosfet: General Description FeaturesDocument5 pagesP-Channel 2.5V Specified Powertrench Mosfet: General Description FeaturesNagaraju NSNo ratings yet

- MDS3604 P-Channel Trench MOSFET -30V -11A 12.1mΩDocument6 pagesMDS3604 P-Channel Trench MOSFET -30V -11A 12.1mΩjay rNo ratings yet

- Fdms7682: N-Channel Powertrench MosfetDocument8 pagesFdms7682: N-Channel Powertrench MosfetGustavo RodriguezNo ratings yet

- FDD8447LDocument6 pagesFDD8447Lsorsa1No ratings yet

- P-Channel 60 V (D-S) MOSFET: Features Product SummaryDocument9 pagesP-Channel 60 V (D-S) MOSFET: Features Product SummaryMie Hijau Tanpa PengawetNo ratings yet

- FDMS0310AS FairchildSemiconductorDocument8 pagesFDMS0310AS FairchildSemiconductorThisal DamsikaNo ratings yet

- Fds6690A Single N-Channel, Logic Level, Powertrench MosfetDocument8 pagesFds6690A Single N-Channel, Logic Level, Powertrench MosfetEsmir MarinNo ratings yet

- Irf 7416 GPBFDocument9 pagesIrf 7416 GPBFKrista TranNo ratings yet

- Si4835BDY: Vishay SiliconixDocument6 pagesSi4835BDY: Vishay SiliconixabdelbakiNo ratings yet

- Onsemiconductor Nds8410a Datasheets 3577Document5 pagesOnsemiconductor Nds8410a Datasheets 3577Google EyeNo ratings yet

- FDD8880Document11 pagesFDD8880DannyNo ratings yet

- Si4435Dy: 30V P-Channel Powertrench MosfetDocument5 pagesSi4435Dy: 30V P-Channel Powertrench MosfetBedjo TjahmricanNo ratings yet

- Sis406Dn: Vishay SiliconixDocument13 pagesSis406Dn: Vishay SiliconixIvo MFNo ratings yet

- 4925B Dual MosfetDocument8 pages4925B Dual MosfetRaj ChoudharyNo ratings yet

- FDMC 8884Document7 pagesFDMC 8884Kholit LitNo ratings yet

- Fds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDocument6 pagesFds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDenis SilvaNo ratings yet

- Fds6690A: Single N-Channel, Logic-Level, Powertrench MosfetDocument6 pagesFds6690A: Single N-Channel, Logic-Level, Powertrench Mosfetmuhammad atifNo ratings yet

- General Description Product Summary: 30V P-Channel MOSFETDocument5 pagesGeneral Description Product Summary: 30V P-Channel MOSFETKarlita GaspitoNo ratings yet

- Si4848DY: Vishay SiliconixDocument8 pagesSi4848DY: Vishay SiliconixFrancisco Wilson Bezerra FranciscoNo ratings yet

- Si4804BDY: Vishay SiliconixDocument6 pagesSi4804BDY: Vishay Siliconixban4444No ratings yet

- Si4948BEY: Vishay SiliconixDocument8 pagesSi4948BEY: Vishay SiliconixCatalin Constantin PopaNo ratings yet

- Datasheet - PHPDocument4 pagesDatasheet - PHPAmadeus JkNo ratings yet

- FDS9435A FairchildSemiconductorDocument6 pagesFDS9435A FairchildSemiconductormuhammad FikriNo ratings yet

- fdc642p f085 PDFDocument7 pagesfdc642p f085 PDFChelaru ValentinNo ratings yet

- Si4447ADY: Vishay SiliconixDocument9 pagesSi4447ADY: Vishay SiliconixLeandro De VegaNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Ceramic InstallationDocument49 pagesCeramic InstallationKevin Tate100% (1)

- Introduction To Programming Using JavaDocument23 pagesIntroduction To Programming Using JavaKevin Tate100% (1)

- Introduction to Programming Using Java Version 5.0Document699 pagesIntroduction to Programming Using Java Version 5.0Ogal Victor100% (1)

- RSeries ProductBriefDocument5 pagesRSeries ProductBriefKevin TateNo ratings yet

- Px865pec Pro (2.0) Eg102Document23 pagesPx865pec Pro (2.0) Eg102Kevin TateNo ratings yet

- 2nd GeDocument2 pages2nd GeDarío AsteteNo ratings yet

- AMD Embedded SolutionsDocument10 pagesAMD Embedded SolutionsKevin TateNo ratings yet

- AMI POST Procedures - PC Analyzer, Debug Card, POST Card, POST CODE, PC DiagnostiDocument2 pagesAMI POST Procedures - PC Analyzer, Debug Card, POST Card, POST CODE, PC DiagnostiKevin TateNo ratings yet

- AmDg Series Soc Product BriefDocument3 pagesAmDg Series Soc Product BriefKevin TateNo ratings yet

- Aptio V Status CodesDocument13 pagesAptio V Status CodesKevin TateNo ratings yet

- AMDGSeriesSOCProductBrief 2Document3 pagesAMDGSeriesSOCProductBrief 2Kevin TateNo ratings yet

- IP 2395 DirectionsDocument7 pagesIP 2395 DirectionsKevin TateNo ratings yet

- Texas Instruments DaVinci OMAP3530 Learning Centre MCU User Manuals Texas - Instruments - User - Guide - 1Document24 pagesTexas Instruments DaVinci OMAP3530 Learning Centre MCU User Manuals Texas - Instruments - User - Guide - 1Kevin TateNo ratings yet

- 2nd GeDocument2 pages2nd GeDarío AsteteNo ratings yet

- SPF-28731 ADocument6 pagesSPF-28731 AKevin TateNo ratings yet

- Serial 1-Wire interface using 74LS05 chipDocument1 pageSerial 1-Wire interface using 74LS05 chipVioleta Pesic NogoNo ratings yet

- PIC32 PinoutDocument1 pagePIC32 PinoutKevin Tate100% (1)

- IP-2372, IP-2376, IP-2377 - DirectionsDocument6 pagesIP-2372, IP-2376, IP-2377 - DirectionsKevin TateNo ratings yet

- KLP6 POST Diagnostic Test Card ManualDocument36 pagesKLP6 POST Diagnostic Test Card ManualsocraticusNo ratings yet

- Notebook Combo-Debug-Card User GuideDocument4 pagesNotebook Combo-Debug-Card User GuideKevin TateNo ratings yet

- RJK 0351 Dpa DatasheetDocument7 pagesRJK 0351 Dpa DatasheetKevin TateNo ratings yet

- 555 Timer Ic - An170Document19 pages555 Timer Ic - An170acidreign100% (1)

- PA2089 DirectionsDocument2 pagesPA2089 DirectionsKevin TateNo ratings yet

- BDMaster GUIDE Extract Encapsulated BiosDocument14 pagesBDMaster GUIDE Extract Encapsulated BiosKevin TateNo ratings yet

- Benq LDP6100Document122 pagesBenq LDP6100zdravkorr100% (1)

- BDE0003 CatalogDocument162 pagesBDE0003 CatalogKevin TateNo ratings yet

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MDocument11 pagesFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateNo ratings yet

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Document11 pagesN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateNo ratings yet

- Samsung Camera i-Launcher GuideDocument8 pagesSamsung Camera i-Launcher GuideKevin TateNo ratings yet

- Singer 2802868Document114 pagesSinger 2802868Edenia JolvinoNo ratings yet

- Chery Amulet 1,6 Engine Service ManualDocument76 pagesChery Amulet 1,6 Engine Service ManualG x HxhNo ratings yet

- Music and Therapy Bun2Document17 pagesMusic and Therapy Bun2PanteaAlisaNo ratings yet

- PackageCare Maintenance ChecklistDocument1 pagePackageCare Maintenance ChecklistBùi ViệtNo ratings yet

- Soil Chemistry KeywordsDocument8 pagesSoil Chemistry Keywordssobe64 sNo ratings yet

- April 12th Test PDFDocument32 pagesApril 12th Test PDFهخه •No ratings yet

- Shrimp ReceipeDocument2 pagesShrimp Receipedonna blazoNo ratings yet

- Commercial Law Review Midterm - Without AnswersDocument1 pageCommercial Law Review Midterm - Without AnswersTorni JoNo ratings yet

- Come Back To Your Senses Use Your Body: Psychologyt LsDocument1 pageCome Back To Your Senses Use Your Body: Psychologyt LsMarina Moran100% (1)

- Top 50 Most Delicious Taco Reci - Julie HatfieldDocument267 pagesTop 50 Most Delicious Taco Reci - Julie HatfieldMazhar Aslam100% (2)

- Pre-Final Exam in Audit 2-3Document5 pagesPre-Final Exam in Audit 2-3Shr BnNo ratings yet

- English Sds Turalik 52Document13 pagesEnglish Sds Turalik 52Muhammad ArifudinNo ratings yet

- Land Tenure SystemsDocument140 pagesLand Tenure SystemsjoeclintNo ratings yet

- Wheat Sourdough Fermentation - Effects of Time and Acidification On Fundamental Rheological PropertiesDocument9 pagesWheat Sourdough Fermentation - Effects of Time and Acidification On Fundamental Rheological PropertiesmaurodiloretoNo ratings yet

- MKT421 New Product Development PDFDocument26 pagesMKT421 New Product Development PDFNass AzwadiNo ratings yet

- Salary Exchange... A Tax Efficient Way To Boost Your Plans For The FutureDocument4 pagesSalary Exchange... A Tax Efficient Way To Boost Your Plans For The FutureStandard Life UKNo ratings yet

- Herbal MedicineDocument38 pagesHerbal MedicineBurei KouNo ratings yet

- Business Plan Hair DyeDocument12 pagesBusiness Plan Hair Dyercool_rahul0039341No ratings yet

- Mcimt NDT Kids at 1Document12 pagesMcimt NDT Kids at 1api-485106673No ratings yet

- Flashcards - CP4 Preparation of A Standard Solution and Titration - Edexcel IAL Chemistry A-LevelDocument37 pagesFlashcards - CP4 Preparation of A Standard Solution and Titration - Edexcel IAL Chemistry A-LevelTravel UnlimitedNo ratings yet

- Synovial Joints StructureDocument20 pagesSynovial Joints StructureJayricDepalobosNo ratings yet

- Pensions Reforms at NSSFDocument4 pagesPensions Reforms at NSSFcliffmogere2348No ratings yet

- Candidates applied for Medical Officer post on contract basisDocument11 pagesCandidates applied for Medical Officer post on contract basiszephyrNo ratings yet

- Better - Call - Saul - 4x10 WINNERDocument70 pagesBetter - Call - Saul - 4x10 WINNERMarcos Valdés GarridoNo ratings yet

- Pengaruh Ukuran Potongan Kopra Dalam Proses Pengeringan: Effect of The Copra Cut Size in The Drying ProcessDocument5 pagesPengaruh Ukuran Potongan Kopra Dalam Proses Pengeringan: Effect of The Copra Cut Size in The Drying ProcessAlexia Desi Ratnasari Loi 1841100210No ratings yet

- Torc 4 Abscohort1 - CompressDocument13 pagesTorc 4 Abscohort1 - CompressFaye MartinezNo ratings yet

- 342Mass&HeatModule (3) Soln071118 OlefinPlantDocument12 pages342Mass&HeatModule (3) Soln071118 OlefinPlantmanuelNo ratings yet

- E 242 - 95 R00 - Rti0mi1sruq - PDFDocument5 pagesE 242 - 95 R00 - Rti0mi1sruq - PDFLeón SuárezNo ratings yet

- SEN Code of Practice 2001Document148 pagesSEN Code of Practice 2001Matt GrantNo ratings yet

- Accessibility POC: October 26, 2017Document7 pagesAccessibility POC: October 26, 2017Ramesh BodukaniNo ratings yet

- Trangia Worksheet IntroDocument2 pagesTrangia Worksheet Introjames.mccooeyNo ratings yet