Professional Documents

Culture Documents

7 ED0 F3 CFD 01

Uploaded by

Daniel PeixotoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

7 ED0 F3 CFD 01

Uploaded by

Daniel PeixotoCopyright:

Available Formats

CONTROLE PREDITIVO DE CORRENTE APLICADO A UM CONTROLADOR DE

CARGA DE BATERIAS BASEADO EM CONVERSOR CC-CC BIDIRECIONAL

Universidade Federal de Juiz de Fora

Faculdade de Engenharia

Programa de Ps-Graduao em Engenharia Eltrica

Autor: Augusto de Caux Henriques Damasceno

Orientadores: Prof. Pedro Gomes Barbosa

Prof. Henrique Antnio Carvalho Braga

JUIZ DE FORA, MG - BRASIL

JUNHO 2008

CONTROLE PREDITIVO DE CORRENTE APLICADO A UM CONTROLADOR DE

CARGA DE BATERIAS BASEADO EM CONVERSOR CC-CC BIDIRECIONAL

AUGUSTO DE CAUX HENRIQUES DAMASCENO

DISSERTAODE MESTRADOSUBMETIDAAOCORPODOCENTE DOPROGRAMA

DE PS-GRADUAO EM ENGENHARIA ELTRICA DA FACULDADE DE ENGE-

NHARIA DA UNIVERSIDADE FEDERAL DE JUIZ DE FORA COMO PARTE DOS RE-

QUISITOS NECESSRIOS PARA A OBTENO DO GRAU DE MESTRE EM ENGE-

NHARIA ELTRICA.

Aprovada por:

Prof. Pedro Gomes Barbosa, D.Sc.

Prof. Henrique Antnio Carvalho Braga, Dr.Eng.

Prof. Francisco Jos Gomes, Dr.

Prof. Jose Andres Santisteban Larrea, D.Sc.

JUIZ DE FORA, MG - BRASIL

JUNHO 2008.

Deus e aos meus pais,

Vicente e Ana Ceclia.

iii

Agradecimentos

Deus, pela inteligncia, sade e fora de vontade;

Aos meus pais, Vicente e Ana Ceclia, pelo afeto, dedicao, compreenso e conselhos, aos

meus irmos Gustavo e Filipe, pela grande amizade, Ana Luisa pelo amor e carinho;

Ao Prof. Pedro Gomes Barbosa, pela dedicao, amizade e pela boa vontade de transmitir

seus conhecimentos;

Ao Prof. Henrique Antnio Carvalho Braga, pelo interesse em ajudar, pelo apoio tcnico e

compreenso;

Ao Prof. Carlos Augusto Duque, pelo apoio tcnico e pela ateno;

Aos amigos pelo companheirismo e compartilhamento de seus conhecimentos;

Aos desenvolvedores do ATP/EMTP, Dia, Gimp, L

A

T

E

X, Miktex e LEd que tornaram possvel

esta dissertao.

Universidade Federal de Viosa (UFV) por ter me acolhido durante cinco anos.

Universidade Federal de Juiz de Fora (UFJF) pelo suporte oferecido durante estes dois

anos.

Coordenao de Aperfeioamento de Pessoal de Nvel Superior (CAPES) por fornecer

suporte de acesso ao portal do IEEE.

E ao Conselho Nacional de Desenvolvimento Cientco e Tecnolgico (CNPq) pelo incen-

tivo nanceiro.

iv

A imaginao mais importante que o conhecimento.

A. Einstein.

v

Resumo da Dissertao apresentada ao Programa de Ps-Graduao em Engenharia Eltrica

da UFJF como parte dos requisitos necessrios para obteno do grau de Mestre em Enge-

nharia Eltrica (M.Eng.)

CONTROLE PREDITIVO DE CORRENTE APLICADO A UM CONTROLADOR DE

CARGA DE BATERIAS BASEADO EM CONVERSOR CC-CC BIDIRECIONAL

Augusto de Caux Henriques Damasceno

Junho 2008

Orientadores: Prof. Pedro Gomes Barbosa

Prof. Henrique Antnio Carvalho Braga

rea de Concentrao: Instrumentao e Controle

Este trabalho investiga a utilizao do controle preditivo digital no modo corrente para

controlar um conversor CC-CC bidirecional conectado ao sistema de gerao fotovoltaico. O

conversor CC-CC, com controle digital no modo corrente, opera como um sistema de carga

de bateria de alta performance, possibilitando o prolongamento de sua vida til por utilizar

um controle de carga preciso, com constante monitoramento e rpida proteo. A modela-

gem digital do conversor e o controle so apresentados e discutidos. Resultados de simulao

so usados para validar os procedimentos do projeto do controle. O controle digital no modo

corrente foi implementado em um DSP TMS320F2812 da Texas Instruments.

vi

Abstract of the Dissertation presented to the Program of Electrical Engineering of UFJF as a

partial fulllment of the requirements for Master of Electrical Engineer Degree (M.Eng.)

PREDICTIVE CURRENT MODE CONTROLE APPLIED TO A BATTERY CHARGE

SYSTEM BASED ON BIDIRECTIONAL DC-DC CONVERTER

Augusto de Caux Henriques Damasceno

June 2008

Advisors: Prof. Pedro Gomes Barbosa

Prof. Henrique Antnio Carvalho Braga

Concentration Area: Instrumentation and Control

This work investigates the utilization of a predictive digital current-mode controller for

a bidirectional DC-DC converter connected to a photovoltaic electric generation system.

The DC-DC converter, with the digital current control, operates as a high performance

battery charger system, enabling long battery life by providing precision charging control,

constant monitoring and fast protection. Digital modeling of the converter and the controller

are presented and discussed. Simulation results are used to validate the design controller

procedures. The digital currentmode control was implemented in the TMS320F2812 DSP

of Texas Instruments.

vii

Sumrio

1 Introduo 1

1.1 Identicao do problema . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.2 Motivao do estudo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1.3 Contribuies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.4 Objetivos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.5 Organizao do texto . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Sistema Fotovoltaico Baseado em Estrutura Descentralizada 6

2.1 Consideraes iniciais sobre a utilizao de baterias em sistemas PV . . . . 6

2.2 Baterias chumbo-cido . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.3 Processo de carga da bateria . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3.1 Estimao do estado de carga e vida til da bateria . . . . . . . . . 11

2.3.2 Algoritmo de carga/descarga . . . . . . . . . . . . . . . . . . . . . 12

2.4 Topologia do conversor bidirecional . . . . . . . . . . . . . . . . . . . . . 13

2.5 Ondulaes CA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.6 Modelagem de conversores estticos . . . . . . . . . . . . . . . . . . . . . 17

2.7 Concluses parciais . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3 Controle de Conversores Estticos 19

3.1 Controle modo tenso . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.2 Controle modo corrente . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.2.1 Controle modo corrente de pico . . . . . . . . . . . . . . . . . . . 22

3.2.2 Controle modo corrente de pico com compensao em rampa . . . 22

3.2.3 Controle modo corrente mdia . . . . . . . . . . . . . . . . . . . . 23

3.3 Implementao do controlador digital . . . . . . . . . . . . . . . . . . . . 23

3.3.1 Processamento digital de sinais de tempo contnuo . . . . . . . . . 24

3.3.2 Amostragem sncrona . . . . . . . . . . . . . . . . . . . . . . . . 26

3.4 Malhas de controle para o conversor bidirecional . . . . . . . . . . . . . . 30

3.4.1 Malha interna - controle preditivo digital modo corrente . . . . . . 30

3.4.2 Malha externa - controle proporcional-integral . . . . . . . . . . . 33

3.5 Robustez e consideraes de projeto . . . . . . . . . . . . . . . . . . . . . 37

3.5.1 Variao da indutncia do conversor bidirecional . . . . . . . . . . 37

3.5.2 Resoluo dos ADCs e DPWMs . . . . . . . . . . . . . . . . . . . 38

3.6 Concluses parciais . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

viii

4 Simulaes Digitais 41

4.1 Amostragem sncrona e controle preditivo . . . . . . . . . . . . . . . . . . 41

4.1.1 Amostragem Timer Underow com defasagem de um ciclo . . . . . 42

4.1.2 Amostragem Timer Underow com defasagem de dois ciclos . . . . 44

4.1.3 Amostragem Timer Period Match com defasagem de dois ciclos . . 45

4.2 Robustez do controle preditivo . . . . . . . . . . . . . . . . . . . . . . . . 46

4.3 Controle da malha externa . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.4 Resoluo dos ADCs e DPWMs . . . . . . . . . . . . . . . . . . . . . . . 50

4.5 Conversor operando no modo bidirecional . . . . . . . . . . . . . . . . . . 51

4.6 Concluses parciais . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

5 Implementao Experimental 54

5.1 Circuitos de interface entre o conversor e o DSP . . . . . . . . . . . . . . . 55

5.1.1 Circuito de condicionamento de sinal . . . . . . . . . . . . . . . . 57

5.1.2 Circuito de condicionamento do sinal de disparo . . . . . . . . . . 58

5.2 Controle de corrente . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.3 Variao da tenso do barramento CC . . . . . . . . . . . . . . . . . . . . 61

5.4 Bateria interligada ao sistema PV . . . . . . . . . . . . . . . . . . . . . . . 62

5.5 Concluses parciais . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6 Conversores Interleaved 67

6.1 Consideraes iniciais . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.2 Simulaes no programa ATP/EMTP . . . . . . . . . . . . . . . . . . . . . 69

6.3 Concluses parciais . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

7 Concluses 72

7.1 Concluses nais . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

7.2 Propostas de trabalhos futuros . . . . . . . . . . . . . . . . . . . . . . . . 73

A Produo Cientca 78

A.1 Publicaes em Anais de Congressos Nacionais . . . . . . . . . . . . . . . 78

B Tcnicas de Modelagem 79

B.1 Mdia de espao de estados . . . . . . . . . . . . . . . . . . . . . . . . . . 79

B.2 Modelo de circuito equivalente . . . . . . . . . . . . . . . . . . . . . . . . 81

C Programando em ATP e DSP 83

C.1 Algoritmo em MODELS/ATP . . . . . . . . . . . . . . . . . . . . . . . . 83

C.2 Registradores do DSP TMS320F2812 . . . . . . . . . . . . . . . . . . . . 85

C.3 Algoritmo em Linguagem C/DSP . . . . . . . . . . . . . . . . . . . . . . 86

ix

Lista de Figuras

2.1 Sistema PV em estrutura descentralizada. . . . . . . . . . . . . . . . . . . 7

2.2 Custos do sistema PV - fonte: IEA2002. . . . . . . . . . . . . . . . . . . . 8

2.3 Banco de baterias chumbo-cido com seis clulas em srie. . . . . . . . . . 9

2.4 Estgios de carga para a bateria chumbo-cido. . . . . . . . . . . . . . . . 12

2.5 Algoritmo de carga/descarga da bateria. . . . . . . . . . . . . . . . . . . . 13

2.6 Topologias de conversores CC-CC PWM no isolados: (a) buck e (b) boost. 14

2.7 Conversor bidirecional CC-CC PWM. . . . . . . . . . . . . . . . . . . . . 15

2.8 Forma de onda da corrente no indutor para o conversor bidirecional. . . . . 15

3.1 Diagrama de blocos de malha fechada. . . . . . . . . . . . . . . . . . . . . 19

3.2 Diagrama do controle modo tenso. . . . . . . . . . . . . . . . . . . . . . 20

3.3 Diagrama do CPM de pico. . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.4 Diagrama do CPM com compensao em rampa. . . . . . . . . . . . . . . 22

3.5 Diagrama do CPM mdia. . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.6 Diagrama de blocos do controle digital. . . . . . . . . . . . . . . . . . . . 24

3.7 Circuito esquemtico do S/H - TMS320F2812. . . . . . . . . . . . . . . . 24

3.8 Sinais no S/H. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.9 Representao espectral de um sinal amostrado. . . . . . . . . . . . . . . . 26

3.10 Hardware DPWM e interrupes. . . . . . . . . . . . . . . . . . . . . . . . 27

3.11 DPWM - modulao trailing edge. . . . . . . . . . . . . . . . . . . . . . . 27

3.12 DPWM - modulao leading edge. . . . . . . . . . . . . . . . . . . . . . . 28

3.13 DPWM - modulao trailing triangle. . . . . . . . . . . . . . . . . . . . . 28

3.14 DPWM - modulao leading triangle. . . . . . . . . . . . . . . . . . . . . 28

3.15 Malhas de controle para o conversor bidirecional. . . . . . . . . . . . . . . 30

3.16 Forma de onda da corrente no indutor com controle preditivo. . . . . . . . . 31

3.17 Modelagem da malha interna como fonte de corrente. . . . . . . . . . . . . 32

3.18 Diagrama de blocos do PI. . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.19 Lugar das razes para o projeto do controle. . . . . . . . . . . . . . . . . . 36

4.1 Diagrama esquemtico do conversor bidirecional no ATPDraw. . . . . . . . 42

4.2 Amostragem realizada na subida e controle preditivo de um ciclo. . . . . . 43

4.3 Amostragem realizada na subida e controle preditivo de dois ciclos. . . . . 44

4.4 Amostragem realizada na descida e controle preditivo de dois ciclos. . . . . 45

4.5 Indutncia da planta alterada para 100 H. . . . . . . . . . . . . . . . . . . 46

4.6 Comparao das razes cclicas para desvios no parmetro L. . . . . . . . . 46

4.7 Indutncia da planta alterada para 250 H. . . . . . . . . . . . . . . . . . . 47

4.8 Comparao das razes cclicas para desvios no parmetro L. . . . . . . . . 47

4.9 Lugar das razes para f

a

= 2500 Hz. . . . . . . . . . . . . . . . . . . . . . 48

4.10 Controle de tenso: malha externa a 2500 Hz. . . . . . . . . . . . . . . . . 48

x

4.11 Lugar das razes para f

a

= 1250 Hz. . . . . . . . . . . . . . . . . . . . . . 49

4.12 Controle de tenso: malha externa a 1250 Hz. . . . . . . . . . . . . . . . . 49

4.13 Corrente no indutor para ADC de 12 bits e DPWM de 10 bits. . . . . . . . 50

4.14 Corrente no indutor para ADC de 8 bits e DPWM de 7 bits. . . . . . . . . 50

4.15 Esquemtico do conversor operando como bidirecional no ATPDraw. . . . . 51

4.16 Inverso da corrente no indutor com controle preditivo de um ciclo. . . . . 52

4.17 Inverso da corrente no indutor com controle preditivo de dois ciclos. . . . 52

5.1 Diagrama esquemtico do circuito de interface. . . . . . . . . . . . . . . . 55

5.2 Prottipo de 3 kW do conversor bidirecional. . . . . . . . . . . . . . . . . 56

5.3 DSP, placa de condicionamento de sinal e placa de sinal de disparo. . . . . 56

5.4 Circuito de condicionamento de sinal. . . . . . . . . . . . . . . . . . . . . 57

5.5 Circuito do sinal de disparo. . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.6 Sinal de disparo do dispositivo S

2

e corrente no indutor. . . . . . . . . . . . 59

5.7 Circuito esquemtico da aquisio de v

GE2

e i

L

. . . . . . . . . . . . . . . . 59

5.8 Variao na corrente de referncia de 3 A para 5 A e vice-versa. . . . . . . 60

5.9 Variao da carga: corrente constante. . . . . . . . . . . . . . . . . . . . . 60

5.10 Circuito esquemtico da aquisio de v

BB

e i

L

. . . . . . . . . . . . . . . . 61

5.11 Variao em degrau da tenso no barramento CC. . . . . . . . . . . . . . . 61

5.12 Circuito esquemtico da aquisio de v

CC

e i

L

. . . . . . . . . . . . . . . . 62

5.13 Variao senoidal em 120Hz da tenso do barramento CC. . . . . . . . . . 62

5.14 Tenso no barramento CC e corrente no indutor. . . . . . . . . . . . . . . . 63

5.15 Circuito esquemtico da aquisio de v

BB

e i

L

. . . . . . . . . . . . . . . . 63

5.16 Tenso na bateria e corrente no indutor quando em estgio de descarga. . . 64

5.17 Tenso na bateria e corrente no indutor quando em estgio de carga. . . . . 64

5.18 Tenso na bateria e corrente no indutor. . . . . . . . . . . . . . . . . . . . 65

5.19 Tenso na bateria e corrente no indutor. . . . . . . . . . . . . . . . . . . . 65

6.1 Estrutura interleaved do conversor bidirecional. . . . . . . . . . . . . . . . 68

6.2 Forma de onda das correntes com dois conversores interleaved. . . . . . . . 68

6.3 Esquemtico da simulao do conversor interleaved no ATPDraw. . . . . . 69

6.4 Correntes em interleaved para trs conversores. . . . . . . . . . . . . . . . 70

6.5 Comparao entre o conversor simples e o interleaved. . . . . . . . . . . . 70

6.6 DFT da corrente para conversores interleaved. . . . . . . . . . . . . . . . . 71

B.1 Circuito equivalente para conversores estticos. . . . . . . . . . . . . . . . 81

xi

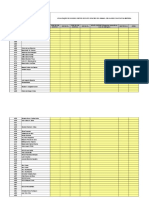

Lista de Tabelas

1.1 Projeo dos custos para sistemas de armazenamento de energia. . . . . . . 2

2.1 Parametros da bateria chumbo-cido - EnerSystem. . . . . . . . . . . . . . 9

3.1 Correlao entre diferentes mtodos de modulao e CPM. . . . . . . . . . 29

4.1 Parmetros das simulaes no ATP/EMTP. . . . . . . . . . . . . . . . . . . 42

5.1 Parmetros referentes ao circuito de condicionamento de sinal. . . . . . . . 57

B.1 Parmetros do circuito equivalente para alguns conversores. . . . . . . . . . 82

B.2 Parmetros da funo de transferncia de pequenos sinais. . . . . . . . . . 82

xii

Lista de Abreviaturas e Siglas

A/D Analgico/Digital

ADC Conversor A/D

Ah Ampre-hora

ATP programa de transitrios eletromagnticos alternativo (do ingls, Alternative

Transients Program)

C Capacidade

CAES armazenamento de energia em ar comprimido (do ingls, Compressed Air Energy

Storage)

CCM modo de conduo contnua (do ingls, Continuous Conduction Mode)

CI Circuito Integrado

CPM controle modo corrente (do ingls, Current Programmed Mode)

D/A Digital/Analgico

DAC Conversor D/A

DCM modo de conduo descontnua (do ingls, Discontinuous Conduction Mode)

DPWM modulao por largura de pulso digital (do ingls, Digital Pulse Width Modulation)

DSP processador digital de sinal (do ingls, Digital Signal Processor)

EM administrador de eventos (do ingls, Event Manager)

EMI interferncia eletromagntica (do ingls, Electromagnetic Interference)

ESR resistncia srie equivalente (do ingls, Equivalent Series Resistance)

EMTP programa de transitrios eletromagnticos (do ingls, Electromagnetic Transients

Program)

EV veculos eltricos (do ingls, Electric Vehicle)

IGBT transistor bipolar com gate isolado (do ingls, Insulated Gate Bipolar Transistors)

MPPT seguidor de mxima potncia (do ingls, Maximum Power Point Tracking)

xiii

PCB placa de circuito impresso (do ingls, Printed Circuit Board)

PWM modulao por largura de pulso (do ingls, Pulse Width Modulation)

PFC correo de fator de potncia (do ingls, Power Factor Correction)

PI compensador proporcional-integral

PIE interrupes perifricas (do ingls, Peripheral Interrupt Expansion)

PV clulas fotovoltaicas (do ingls, Photovoltaic cells)

SGD Sistemas de Gerao Dispersa

SLI partida, iluminao e ignio (do ingls, Starting, Lighting and Ignition)

SMD componentes de montagem supercial (do ingls, Supercial Monting Device)

SMES sistemas de armazenamento de energia em bobinas supercondutoras (do ingls,

Superconducting Magnetic Energy Storage Systems)

S/H amostrador/retentor (do ingls, Sample/Hold)

SoC estado de carga (do ingls, State of Charge)

TACS pacote de anlise transitria de sistemas de controle (do ingls, Transient Analysis

of Control Systems)

UPS fonte de alimentao ininterrupta (do ingls, Uninterruptible Power Supply)

xiv

Captulo 1

Introduo

Nas ltimas dcadas, engenheiros e cientistas tm investigado a utilizao de siste-

mas de gerao baseados em clulas fotovoltaicas (do ingls, Photovoltaic cells) (PV) como

alternativa para atender demanda de energia eltrica de centros comerciais e industriais ou

reas residenciais [1]. O interesse na utilizao desses mdulos PV tem sido motivado por

fatores como: (i) a reduo dos custos dos painis PV, (ii) baixas perdas por transmisso,

j que o sistema de gerao PV pode ser instalado prximo ao centro de carga, (iii) baixa

manuteno, devido a robustez dos painis PV e ausncia de partes mecnicas e (iv) o fato

dos painis PV gerarem uma energia limpa [2] e [3].

1.1 Identicao do problema

Apesar das vantagens citadas anteriormente, os sistemas PV no so capazes de ga-

rantir um fornecimento contnuo

1

de energia eltrica para uma carga j que as clulas PV

no conseguem gerar energia eltrica durante a noite ou longos perodos nublados. Dessa

maneira, quando se deseja garantir um fornecimento contnuo de energia eltrica para uma

carga deve-se prever a instalao de um sistema de armazenamento de energia em paralelo

com o sistema PV. Uma segunda considerao que deve ser feita aqui que a irradiao

solar que atinge os painis solares PV num determinado perodo pode no ser suciente para

gerar a quantidade de energia eltrica que uma carga ou sistema eltrico demanda do sistema

de gerao. Neste caso o sistema de armazenamento forneceria a quantidade de energia que

falta. No obstante, no se pode esquecer a situao em que a energia eltrica gerada nos

painis PV maior que aquela consumida pela carga ou sistema eltrico. Neste caso, o

excedente da energia eltrica gerada pelos painis solares poderia ser armazenada para uso

posterior.

1

O termo contnuo est grafado entre aspas no texto pois o fornecimento de energia eltrica para uma carga

ir depender da capacidade do elemento armazenador durante os perodos em que os painis PV no recebem

irradiao solar.

1

Pelo exposto, tem-se que os elementos acumuladores ou armazenadores de energia

so fundamentais para garantir um funcionamento autnomo dos sistemas de gerao de

energia eltrica baseados em clulas PV.

A Tabela 1.1 apresenta uma comparao das capacidades e dos custos, por kW e

por kWh, de armazenadores de energia de diferentes tecnologias [4]. Dentre aqueles base-

ados em tecnologias j amadurecidas encontram-se desde o armazenamento de energia por

bombeamento de gua e o armazenamento de energia em ar comprimido (do ingls, Com-

pressed Air Energy Storage) (CAES), para o armazenamento de energia em larga escala, at

o armazenamento de energia em volantes de inrcia (do ingls, ywheels) e os acumuladores

eletroqumicos. J entre os elementos armazenadores baseados em tecnologias emergentes

pode-se citar os supercapacitores, que so normalmente indicados para sistemas relativa-

mente pequenos, e os sistemas de armazenamento de energia em bobinas supercondutoras

(do ingls, Superconducting Magnetic Energy Storage Systems) (SMES).

Tabela 1.1: Projeo dos custos para sistemas de armazenamento de energia.

Sistemas Faixas de potncia (MW) US$/kW US$/kWh

Acumuladores eletroqumicos 0,5100 100200 150-300

Supercapacitor 110 300 3600

Volante de inrcia 110 200500 100800

SMES 101000 3001000 3003000

CAES 501000 5001000 1015

Bombeamento de gua 1001000 6001000 1015

A anlise da Tabela 1.1 permite observar que os acumuladores eletroqumicos esto

entre os dispositivos de armazenamento mais baratos disponveis atualmente no mercado.

Alm de serem uma tecnologia bastante dominada tem-se a vantagem de poder associar

vrios elementos em srie e paralelo para alimentar sistemas eltricos desde alguns W at

centenas de kW de capacidade. de se observar que tecnologias como o bombeamento de

gua e o CAES apresentam um baixo custo por kWh e um alto custo por kW o qual limita

a sua utilizao em sistemas PV.

1.2 Motivao do estudo

As baterias ou acumuladores eletroqumicos so dispositivos que convertem energia

qumica em energia eltrica a partir de uma reao de oxidao-reduo. Em muitos mode-

los, essas reaes eletroqumicas so reversveis, ou seja, pode-se entregar energia eltrica

nos terminais da bateria, a partir de um circuito externo, e convert-la em energia qumica

em seus elementos ativos, o que caracteriza o processo de recarga.

Diferentemente de outros tipos de reaes no eletroqumicas, como oxidao ou

combusto, onde os eltrons so transferidos diretamente ou s se produz calor, respectiva-

mente, os acumuladores eletroqumicos convertem a energia qumica diretamente em energia

2

eltrica e vice-versa. Portanto no esto sujeitas s limitaes comuns s mquinas trmicas

devido a segunda lei da termodinmica (Ciclo de Carnot). Logo as baterias so capazes de

ter uma maior ecincia na converso de grandes quantidades de energia.

Normalmente as baterias utilizadas em aplicaes PV devem ter caractersticas di-

ferentes quando comparadas com as baterias utilizadas em outras aplicaes como fonte de

alimentao ininterrupta (do ingls, Uninterruptible Power Supply) (UPS), ou veculos el-

tricos (do ingls, Electric Vehicle) (EV), pois no possvel obter o mesmo ciclo de carga

e descarga, ou seja, em cada uma das situaes as exigncias para as cargas e descarga so

distintas necessitando-se de tipos diferentes de baterias. Nas aplicaes PV, a reduo da

vida til das baterias contribui signicativamente para o aumento dos custos do sistema de

gerao que em muitos casos chega a 40 % do custo total. Assim, um aumento no tempo

de vida das baterias alm de melhorar a conabilidade do sistema resulta numa signicativa

reduo dos custos operacionais do sistema [5].

O tipo de acumulador eletroqumico mais empregado atualmente nos sistemas de ge-

rao PV so as baterias chumbo-cido. Estas baterias tm sido as mais utilizadas por apre-

sentarem uma grande capacidade de armazenamento de energia combinado com um custo

inicial mais baixo. Por outro lado a vida til dessas baterias pode ser estendida evitando-se

condies de operaes crticas como longos perodos de sobrecarga ou descargas profun-

das [5].

As baterias chumbo-cido apresentam vantagens como (i) tcnicas de fabricao sim-

ples e de baixo custo, (ii) o fato de utilizar um tecnologia consolidada, convel e bem com-

preendida, (iii) quando usadas corretamente, so durveis e tm uma boa conabilidade, (iv)

a auto-descarga est entre as mais baixas dos sistemas de baterias recarregveis e (v) so

capazes de altas taxas de descarga. J suas principais limitaes so: (i) baixa densidade de

energia, pobre relao peso/energia, o que as limita para uso em aplicaes embarcadas, (ii)

nmero limitado de ciclos de descarga profundas, sendo compatvel com aplicaes auxili-

ares que requerem esses tipos de descargas ocasionalmente, (iii) contm eletrlito cido e

elementos que usam o chumbo como metal ativo, o que a torna agressiva ao meio ambiente,

(iv) h restries quanto ao transporte de uidos chumbo-cido, preocupaes ambientais re-

lativas ao derramamento e ao descontrole trmico ocorrido com o carregamento imprprio.

A vida til das baterias chumbo-cido determinada principalmente pelo modo de

carga e de descarga a que so submetidas. Um melhor desempenho deste processo pode ser

alcanado utilizando-se o mtodo de carga por mltiplos estgios proposto pelos fabrican-

tes [6]. Uma maneira de realizar o processo de carga das baterias pelo mtodo de mltiplos

estgios compreende a utilizao de um conversor CC-CC que possa ser controlado no modo

de corrente e no modo de tenso. Alm disso esse conversor CC-CC deve possuir uma ca-

racterstica bidirecional para permitir tanto a carga quanto a descarga das baterias. Logo, h

a necessidade da elaborao do controle para tal processo pois dependendo da demanda da

carga, da insolao e da condio de carga da bateria ser mais conveniente carreg-la ou

descarreg-la.

Controles analgicos para prover a carga e descarga de baterias so amplamente co-

3

nhecidos [7], mas com os recentes avanos nas tecnologias de microprocessador e proces-

sador digital de sinal (do ingls, Digital Signal Processor) (DSP), incluindo o aumento da

capacidade de processamento e diminuio dos custos, a utilizao do controle digital vem

se tornando cada vez mais vivel. Em geral, aceitvel que o controlador digital oferea

mais funcionalidades se comparado aos controladores analgicos.

1.3 Contribuies

As contribuies deste trabalho so:

i. Emprego do controle digital aplicado ao processo de carga de baterias;

ii. Desenvolvimento de algoritmos em MODELS para simulao de controles digitais em

programa de transitrios eletromagnticos alternativo (do ingls, Alternative Transi-

ents Program) (ATP)/programa de transitrios eletromagnticos (do ingls, Electro-

magnetic Transients Program) (EMTP);

iii. Desenvolvimento de algoritmos em linguagem C para o controle digital, utilizando-se

o DSP TMS320F2812.

iv. Desenvolvimento de um prottipo para utilizao na usina PV presente no campus da

Universidade Federal de Juiz de Fora.

1.4 Objetivos

Este trabalho busca atingir os seguintes ns:

i. Modelar e simular o conversor bidirecional CC-CC como controlador de carga da ba-

teria em ATP/EMTP;

ii. Investigar a utilizao do controle digital preditivo modo corrente para controlar o

processo de carga/descarga do banco de baterias;

iii. Implementar o controle digital preditivo no DSP TMS320F2812;

iv. Desenvolver um prottipo do conversor bidirecional CC-CC de 3 kW para ser usado

em um sistema de gerao PV;

v. Interligar o prottipo ao sistema PV.

vi. Propor a utilizao de conversores interleaved bidirecionais CC-CC com modulao

por largura de pulso (do ingls, Pulse Width Modulation) (PWM), a m de minimizar

as ondulaes de tenso e corrente na bateria;

4

1.5 Organizao do texto

O texto desta dissertao est organizado em sete captulos, incluindo os captulos de

Introduo e de Concluses Finais alm de trs apndices.

O Captulo 2 descreve o sistema de gerao de energia PV no qual inserido o banco

de baterias. A bateria chumbo-cido, o processo de carga, a topologia do conversor bidireci-

onal e temas relacionados so apresentados.

O Captulo 3 apresenta alguns detalhes sobre o controle de conversores estticos,

mostrando suas peculiaridades tanto para o controle analgico quanto para o digital. So

discutidos alguns fatores importantes na aplicao de controladores digitais aos conversores

estticos como por exemplo a amostragem sncrona, resoluo do Conversor A/D (ADC) e

erros de quantizao.

No Captulo 4 so mostrados os resultados alcanados com a modelagem digital do

conversor CC-CC bidirecional PWM no programa ATP/EMTP. A simulao parte de uma

metodologia adotada para a implementao do sistema que possibilita encontrar erros e testar

as tcnicas de amostragens e de controle.

O Captulo 5 mostra detalhes da construo de um prottipo de 3 kW de um conver-

sor CC-CC bidirecional PWM usado como controlador de carga de um banco de baterias.

So apresentados os resultados alcanados em testes realizados com carga resistiva e com a

interligao da bateria ao sistema PV.

No Captulo 6 investigada uma topologia interleaved de conversor CC-CC bidireci-

onal PWM com um controlador preditivo digital de corrente. Resultados de simulaes so

usados para demonstrar a viabilidade e o desempenho dinmico da topologia estudada.

No Captulo 7 so apresentadas as concluses gerais deste trabalho e algumas suges-

tes para trabalhos futuros que podem resultar na continuidade desta pesquisa.

No Apndice A so listados os artigos derivados deste programa de mestrado.

O Apndice B apresenta de forma sucinta a tcnica de modelagem matemtica base-

ada na mdia de espao de estados que fundamental para o entendimento da modelagem

de conversores estticos.

Finalmente, no Apndice C so apresentados os algoritmos implementados no ambi-

ente MODELS ATP/EMTP e linguagem C, usado para programar o DSP TMS320F2812 da

Texas Instruments. Alm dos algoritmos desenvolvidos, apresentada uma breve descrio

dos registradores do processador utilizado.

5

Captulo 2

Sistema Fotovoltaico Baseado em

Estrutura Descentralizada

De uma maneira genrica os sistemas de gerao PV podem ser classicados, de

acordo com o esquema de conexo e funes dos conversores estticos, em (i) topologia

centralizada e (ii) topologia descentralizada. Alm disso, esses sistemas podem tambm ser

classicados de acordo como tipo de conexo rede eltrica, como sistemas (a) no-isolados

ou conectados e (b) isolados ou no-conectados rede bsica de distribuio de energia.

Ainda sobre a conexo dos sistemas PV rede CA, estes tambm podem ser conectados

diretamente ou atravs de transformadores. Apesar de maior rea necessria para a instalao

do sistema PV, os transformadores de conexo fornecem uma proteo adicional para os

painis PV e conversores, que cam isolados galvanicamente da rede CA.

A Figura 2.1 mostra o diagrama esquemtico genrico de um sistema de energia re-

novvel PV descentralizado. Nessa gura pode-se observar as diversas partes que compem

o sistema PV: (i) painis fotovoltaicos, (ii) baterias, (iii) conversores CC-CC e (iv) converso-

res CC-CA. Na estrutura descentralizada cada conversor tem uma funo distinta e possvel

fornecer energia eltrica para cargas CA ou at mesmo cargas CC.

2.1 Consideraes iniciais sobre a utilizao de baterias em

sistemas PV

As aplicaes de sistemas de gerao PV conectados rede eltrica ou Sistemas de

Gerao Dispersa (SGD), baseado em clulas fotovoltaicas, tm crescido nos ltimos anos

nos pases industrializados [8]. A norma IEEE Std-929-2000 apresenta diversas recomenda-

es para interconexo de sistemas fotovoltaicos rede eltrica [9]. Essas recomendaes

tratam desde assuntos importantes tais como o fenmeno chamado ilhamento, onde parte da

rede de distribuio ca energizada pelo SGD quando o sistema CA est fora de servio, at

6

C A

C C

C C

C C

C C

C C

Banc o de Bat er i as

I nv er s or

Co n v e r s o r

Bi di r eci onal

Co n v e r s o r

Bo o s t

P V

Ba r r a me n t o CC Re d e CA o u Ca r g a

Figura 2.1: Sistema PV em estrutura descentralizada conectado ou no a rede eltrica bsica.

nveis tolerveis de harmnicos gerados pelos conversores. Na maioria das aplicaes desse

tipo no so usadas baterias para armazenar parte da energia convertida nas clulas fotovol-

taicas. Ou seja, toda a energia eltrica convertida nos painis PV injetada diretamente na

rede CA.

J os sistemas PV isolados ou no-conectados tm como caracterstica bsica o for-

necimento de energia a cargas ou sistemas isolados. Esses sistemas so economicamente

viveis quando a distncia entre uma rede existente e a carga a ser alimentada muito longa.

Como toda a energia consumida pela carga deve ser fornecida pelo sistema de gerao PV,

devem ser utilizadas baterias chumbo-cido para garantir desde algumas horas at alguns

dias de fornecimento contnuo de energia eltrica. Estima-se que aproximadamente 80% de

todas as aplicaes de mdulos PV so de sistemas no conectados rede CA. Existem tam-

bm os sistemas hbridos onde o sistema de gerao PV conectado em paralelo com outras

fontes de energia como por exemplo diesel-geradores ou geradores elicos.

Atualmente, os dispositivos de armazenamento usados nos sistemas PV possuem um

custo relativo inicial de cerca de 13 % do custo total da instalao do sistema, como ilus-

trado na Figura 2.2. Contudo os custos operativos desses dispositivos podem chegar a 46 %

do custo total quando so considerados os custos de manuteno. Portanto deve-se dar pri-

oridade no desenvolvimento de controladores de carga ecazes e conveis para reduzir os

custos do sistema como um todo, que sejam capazes de aumentar a vida til das baterias [10].

As baterias podem ser conectadas diretamente ao barramento CC ou atravs de um

conversor CC-CC bidirecional como observado na Figura 2.1. Esses conversores represen-

tam somente 5 % do custo total do sistema e extremamente importante que estes sejam

melhorados. Essa armao baseada no fato de que um aumento em 10 % no custo dos

controladores de carga pode levar a uma reduo de 50 % no custo do armazenamento, do-

brando a vida til das baterias. Assim o gerenciamento das baterias um dos pontos mais

ecientes para diminuir os custos dos sistemas de gerao PV como um todo [10].

7

5 %

1 6 %

4 6 %

3 3 %

5 %

1 7 %

1 3 %

6 5 %

Cont r ol ador es ;

Out r os ;

Bat er i as;

M d u l o s .

Cu s t o s

i ni ci ai s

Cu s t o s d e

ma n u t e n o

L e g e n d a :

Figura 2.2: Custos do sistema PV - fonte: IEA2002.

No que diz respeito a possveis conguraes dos sistemas PV, a topologia centrali-

zada, at agora, tem sido a mais amplamente utilizada. O emprego de um nico conversor

para efetuar o seguidor de mxima potncia (do ingls, Maximum Power Point Tracking)

(MPPT) leva a uma subutilizao da capacidade de gerao dos painis PV em situaes nas

quais parte dos painis, danicados e/ou envelhecidos, contribuem para um decrscimo da

ecincia e aumento dos custos da energia gerada pelo sistema [11].

A comercializao de sistemas PV no conectados rede tradicionalmente baseada

em estruturas centralizadas. Nestes casos, quando um ou mais painis PV so danicados,

o sistema no pode entregar a mxima energia gerada. Adicionalmente, estes sistemas tm

sistemas de armazenamento de energia de pior qualidade, devido ao fato do banco de baterias

ser conectado diretamente ao barramento CC.

A estrutura do sistema PV descentralizado, como apresentado neste trabalho, possi-

bilita a interligao de vrios painis PV a partir de vrios conversores que buscam o melhor

ponto de operao do sistema. Outra vantagem da estrutura descentralizada a possibilidade

de realizar manuteno em partes do sistema de gerao, aumentando a conabilidade da

instalao. Os sistemas descentralizados podem ter um ganho de aproximadamente 16 % na

entrega de energia ao barramento quando comparado aos sistemas centralizados [11].

No sistema descentralizado, o banco de baterias alocado fora do uxo principal de

energia, sendo interligado por um conversor com controle bidirecional do uxo de energia.

Esta topologia evita cargas e descargas desnecessrias do banco de baterias, possibilitando

um prolongamento dos ciclos de vida do sistema de armazenamento [12], [13].

2.2 Baterias chumbo-cido

Pelo exposto nas sees anteriores, interliga-se um banco de baterias a um sistema

de gerao PV com o propsito de garantir um fornecimento ininterrupto de energia eltrica.

A Figura 2.3 mostra uma fotograa de um banco de baterias formado por seis clulas ou

8

elementos. Nas baterias chumbo-cido, cada clula tem uma tenso nominal de aproxima-

damente 2 V . A bateria exibida fabricada pela EnerSystem [14] e seus parmetros so

mostrados na Tabela 2.1.

Figura 2.3: Banco de baterias chumbo-cido com seis clulas em srie.

A bateria um dispositivo eletroqumico que converte diretamente a energia arma-

zenada na forma qumica em eletricidade ou vice-versa. A equao que modela a reao

eletroqumica que ocorre nos elementos de uma bateria chumbo-cido apresentada a se-

guir:

Pb + 2H

2

SO

4

+PbO

2

2PbSO

4

+ 2H

2

O (2.1)

Alguns parmetros das baterias so essenciais para o projeto dos controladores de

carga. Os diversos tipos de baterias chumbo-cido podem ser agrupados em: (i) baterias

para partida, iluminao e ignio (do ingls, Starting, Lighting and Ignition) (SLI), (ii)

baterias para trao e (iii) baterias estacionrias [15].

Tabela 2.1: Parametros da bateria chumbo-cido - EnerSystem.

Parmetro Valor

Capacidade nominal 500 Ah/24h

Tenso de sobrecarga 2,65 V

Auto-descarga 2 %/m es (25

o

C)

12 %/m es (55

o

C)

Corrente de descarga

mxima

150 A

Densidade do eletrlito 1300 gr/dm

3

As baterias SLI so um tipo de bateria chumbo-cido projetada principalmente para

ciclos rasos, as quais so freqentemente utilizadas para partida de veculos. Um grande

9

nmero de eletrodos por clula permite bateria fornecer altas correntes de descarga durante

um curto perodo. Embora no sejam projetadas para uma longa vida sob ciclos profundos,

as baterias SLI, s vezes, so usadas em sistemas de PV, principalmente nos pases em

desenvolvimento, onde so os nicos tipos de baterias fabricadas.

Baterias para trao so um tipo de bateria chumbo-cido projetada para ciclos de

carga e descarga profundos. Elas so tipicamente usadas em veculos eltricos e equipamen-

tos como carros de golf e empilhadeiras. Baterias para trao so muito populares para uso

em sistemas PV devido capacidade dos ciclos e sua longa vida til.

Por m, as baterias estacionrias so geralmente utilizadas em UPS para prover ener-

gia em caso de faltas em computadores, equipamentos telefnicos e outras cargas ou dispo-

sitivos crticos. Geralmente elas so projetadas para descarga profundas e ocasionais e ciclos

limitados.

2.3 Processo de carga da bateria

As especicaes de carga e os pontos de operao do controle, que dependem da

bateria e do ambiente, so pontos decientes no que trata de operao de sistemas PV. Um

bomentendimento de como baterias operamemsistemas PV essencial para o sucesso deste.

A principal funo do controlador de carga em sistemas PV proteger a bateria con-

tra sobrecargas e sobredescargas. Qualquer sistema que tenha demandas imprevisveis, inter-

veno do usurio, otimizao ou subdimensionamento das baterias para minimizar custos

iniciais ou outras caractersticas que permitam uma excessiva sobrecarga ou sobredescarga

da bateria necessitam de um controlador de carga ou desconexo por baixa tenso, ou o

resultado ser uma diminuio da vida da bateria e decrescimento da carga disponvel [16].

O emprego do conversor bidirecional para a carga do banco de bateria torna possvel

a utilizao de um nvel de tenso nos terminais da bateria diferente do nvel de tenso do

barramento CC. Assim evita a ligao de muitas clulas em srie e conseqentemente di-

minui o desbalanceamento entre as mesmas. Para a escolha do nvel de tenso do banco

preciso tambm levar em considerao a ecincia do conversor bidirecional, pois a ecin-

cia dependente dos nveis de tenso aos quais o conversor est submetido.

O processo de carga da bateria requer do controlador uma estratgia elaborada de

controle, que carregue a bateria o mais rpido possvel, pois os sistemas PV possuem limita-

es quanto a disponibilidade da energia para realizar tal processo.

O processo indicado pelos fabricantes consiste da utilizao de um algoritmo de qua-

tro estgios [6] que integra as vantagens do mtodo de carga em corrente constante e em

tenso constante, sendo este mtodo tambm conhecido como IU. Sua utilizao maximiza

o processo de carga e aumenta a vida til das baterias.

10

2.3.1 Estimao do estado de carga e vida til da bateria

A Capacidade (C) de uma bateria indica a quantidade total de carga disponvel e

normalmente expressa em Ampre-hora (Ah). A corrente de carga ou descarga da bateria

comercialmente especicada em termos da taxa C (ou C rate, do ingls). A capacidade da

bateria indicada na folha de dados, normalmente, corresponde medio da capacidade para

uma taxa de descarga de C/10, pois a capacidade varia de forma inversa taxa de descarga,

ou seja, elevadas correntes de descarga resultam em menor capacidade.

A determinao do estado de carga (do ingls, State of Charge) (SoC) de uma bate-

ria em funcionamento um processo complexo. Dentre os vrios mtodos propostos para

estimar o SoC tem-se o balano de Ah [5] cuja relao dada por:

SoC[n + 1] = SoC[n] +

(I

BB

[n] I

gas

)T

SoC

C

10

(2.2)

onde: SoC[n + 1] o estado de carga no instante n + 1;

SoC[n] o estado de carga no instante n;

I

BB

[n] a corrente da bateria no instante n;

I

gas

o fator de perdas.

T

SoC

o intervalo entre amostras;

C

10

a capacidade nominal para uma taxa de descarga de 10h;

A relao (2.2) permite estimar o SoC levando em considerao as perdas das mes-

mas. Contudo ele apresenta uma estimao incorreta quando submetido a longos perodos

de carga e descarga incompletos.

H algum tempo, busca-se o desenvolvimento de mtodos de avaliao da vida til

da bateria quando estas esto em operao no sistema PV, que pode ser vantajosa por redu-

zir custos de manuteno. Uma das tcnicas estudas baseada na estimao da resistncia

interna da bateria. As tcnicas utilizadas para medio de impedncia de baterias no so

padronizadas, e em muitos casos, so tcnicas proprietrias. Porm, basicamente, as me-

dies consistem em quanticar o valor da resistncia interna. Para realizar tal medio

injetada uma corrente alternada na bateria e mede-se a componente alternada da tenso. Com

essas medies o mdulo da impedncia interna da bateria calculada e pode-se estimar o

SoC [17].

As caractersticas de impedncia para uma ampla faixa de freqncia so estudadas

em [18]. Geralmente observado um comportamento similar e todas as baterias exibem

predominantemente um comportamento resistivo entre 10 Hz e 1 KHz. Pode-se ento

mostrar que a impedncia interna diretamente afetada pelo SoC da bateria. E na regio

resistiva no exibe qualquer variao signicante dependente da temperatura, para uma faixa

de 25

o

C a 75

o

C.

11

2.3.2 Algoritmo de carga/descarga

Numa bateria chumbo-cido, quando no se conhece previamente o SoC da bateria

ou se este esta abaixo de 20% recomendvel comear o processo de carga com uma carga

leve conforme indicado na Figura 2.4. A carga leve um estgio de carga da bateria com

corrente constante. Neste modo, uma baixa corrente, tipicamente C/100 ou menor, aplicada

a bateria at que a tenso da bateria atinja o valor da tenso de corte, V

CUTOFF

. Este nvel de

tenso corresponde, aproximadamente, a capacidade zero. Esta corrente imposta na bateria

para assegurar uma operao contnua sem danos s clulas da bateria.

t

( V) ( A)

Tens o da Bat er i a

Ca r g a

L e v e

Ca r g a

I nt ens a

So b r e -

c a r g a

Ca r g a d e

Fl ut ua o

I

B U L K

I

T RI CK L E

C U T O F F

V

O C

V

V

F L OA T

I

O C T

Cor r ent e da Bat er i a

Figura 2.4: Estgios de carga para a bateria chumbo-cido.

Ao concluir o estgio de carga leve passa-se a operar no estgio de carga intensa, que

tambm um estgio de carga com corrente constante, cuja funo prover uma carga rpida

para a bateria. Fabricantes denem esta corrente como a mxima corrente de carga permitida

para as clulas. Podendo ser aplicada na bateria entre as tenses de corte (V

CUTOFF

) e

sobrecarga (V

OC

). Tipicamente, a corrente neste estgio ser de C/5 a 2C, dependendo do

fabricante e do tipo de bateria.

Reaes qumicas indesejadas ocorrem quando h sobrecarga da bateria, e o inicio

dessa depende da taxa de carga, quanto mais alta a taxa mais breve ser o inicio das reaes.

A sobrecarga coincide com 100% da capacidade quando a recarga feita numa taxa menor

que C/100. Portanto, para altas taxas de carga, necessrio evitar tais reaes, sendo ne-

cessrio realizar o controle da sobrecarga aplicando uma tenso constante. Tipicamente, a

tenso V

OC

um valor entre 2,45 V/clula a 2,65 V/clula, dependendo da taxa de carga. A

seleo inadequada da tenso V

OC

resulta em uma desidratao da bateria e em uma reduo

da vida til.

Aps completo o processo de carga, SoC a 100%, inicia-se um estgio de carga de

utuao que realizado com tenso constante e serve para manter a capacidade da bateria

12

compensando a alto descarga, a qual devido a processos qumicos internos.

A estrutura em mquina de estados proposta para controlar o processo de carga

mostrada na Figura 2.5, cuja autonomia se restringe a determinar a mudana entre estgios

de carga. O supervisrio (Sup), que controla todo o sistema PV, fornece os parmetros ne-

cessrios ao correto funcionamento do controlador de carga/descarga assim como dos outros

dispositivos presentes no sistema. Logo o supervisrio determina quando possvel carregar,

e a corrente de carga (I

BULK

), ou descarregar a bateria.

Ca r g a

L e v e

Ca r g a

I nt ens a

So b r e c a r g a

Ca r g a d e

Fl ut ua o

C U T OF F

V > V

S E

B B O C

V > V

S E

B B

O C

I < I

S E

B B

De s c a r g a

I

B UL K

I =

B B

I I =

B B T RI CKL E

O C

V = V

B B

Su p

Su p Su p

Su p

Figura 2.5: Algoritmo de carga/descarga da bateria.

2.4 Topologia do conversor bidirecional

Baseado na topologia descentralizada do sistema de gerao fotovoltaico mostrado

na Figura 2.1 pode-se concluir que o conversor CC-CC responsvel pela carga e descarga

do banco de baterias deve ter uma caracterstica bidirecional em corrente. Esta armao

devida ao fato de que a tenso do barramento CC do sistema PV unidirecional e se a

corrente pelo conversor no inverter seu sentido o uxo de potncia entre a fonte e o banco

de baterias ser tambm unidirecional.

Encontram-se na literatura tcnica especializada diversos trabalhos sobre topologias

bsicas de conversores CC-CC. Esses conversores CC-CC podem ser classicados como

conversores isolados, que usam transformadores para isolar a fonte e a carga, e conversores

no-isolados, sem transformadores. Apesar do isolamento galvnico entre a fonte e a carga,

os transformadores dos conversores isolados no so simples de serem construdos pois so

projetados para operarem em freqncias elevadas. Alm disso esses transformadores tam-

bm limitam expressivamente a faixa de potncia de operao destes conversores.

J as principais topologias de conversores no isolados so: (i) buck ou abaixador,

(ii) boost ou elevador, (iii) buck-boost, (iv)

Cuk, (v) SEPIC e (vi) Zeta [19] [20].

13

Os conversores Zeta e buck-boost so considerados inadequados para controlar a

carga e a descarga das baterias pois suas correntes de sada possuem valores elevados de

ondulao. Essa caracterstica altamente prejudicial para a vida til das baterias. J os

conversores

Cuk, SEPIC e Zeta tm um grande nmero de elementos passivos e um com-

portamento dinmico de quarta ordem que aumentam a complexidade da modelagem e do

controle dos mesmos. O SEPIC apresenta apenas uma das correntes ltradas, enquanto que

o

Cuk tem ambas. Contudo o

Cuk apresenta inconveniente de uma das tenses ser invertida

assim como o buck-boost.

As Figuras 2.6 (a) e (b) mostram as topologias de um conversor buck e um conversor

boost, respectivamente. Nessa gura a tenso V

2

relativa aos terminais do conversor que

so conectados ao banco de baterias enquanto que a tenso V

1

relativa aos terminais do con-

versor que so conectados ao barramento CC. Para que o conversor buck e o conversor boost

funcionem corretamente deve-se garantir que V

1

> V

2

, ou seja, o banco de baterias deve ter

uma tenso terminal inferior tenso do barramento CC. Assim, enquanto o conversor buck

pode ser usado para carregar a bateria, o conversor boost usado para descarreg-la.

L

S

1

D

2

V

1

I

L

V

2

(a)

L

S

2

D

1

V

1

I

L

V

2

(b)

Figura 2.6: Topologias de conversores CC-CC PWM no isolados: (a) buck e (b) boost.

A Figura 2.7 mostra a topologia de um conversor bidirecional CC-CC PWM, tambm

denominado conversor bidirecional half-bridge. Este conversor pode ser visto como resul-

tante da unio de dois conversores bsicos, sendo eles um conversor buck, Figura 2.6 (a), e

um conversor boost, Figura 2.6 (b).

O mais interessante aspecto do conversor bidirecional sua fcil realizao com m-

dulos pr-fabricados em meia-ponte (half-bridge) e drivers correspondentes. Esta caracte-

rstica especialmente proveitosa para aplicaes de grande potncia j que vrios mdulos

podem ser conectados em paralelo [21]. O fato de se conectar vrios mdulos em paralelo,

alm de reduzir a indutncia de sada equivalente do circuito, permite a utilizao de estra-

tgias de converso interleaved, que possibilitam uma reduo das ondulaes na forma de

14

S

L

2

S

1

D

1

D

2

hal f - br i dge

V

1

I

L

V

2

Figura 2.7: Conversor bidirecional CC-CC PWM.

onda da corrente que usada para carregar a bateria.

A Figura 2.8 ilustra a forma de onda da corrente no indutor para o conversor bidi-

recional onde se observa que as chaves semicondutoras controladas (S

1

e S

2

) operam com

razes cclicas complementares (d e 1 d), onde d denido em (2.3). Ao variar a razo

cclica pode-se modicar no somente a componente mdia da corrente como tambm fazer

com que esta passe a trabalhar no quadrante desejado. Portanto este um conversor classe C.

Para utiliz-lo no processo de carga/descarga necessrio que a tenso da bateria seja menor

que a tenso do barramento CC, logo V

1

referente ao barramento CC e V

2

ao banco de

baterias, ver Figura 2.7. Portanto este conversor possibilita um banco de baterias com tenso

menor que a tenso do barramento o que proporciona uma melhor equalizao das clulas j

que reduz a quantidade de clulas em srie.

d

t

ON1

T

S

(2.3)

onde, t

ON1

o tempo que a chave S

1

permanece ativa.

t

i

L

d. T ( 1- d) . T

S

1

D

2

S

2

D

1

B U C K

B O O S T

0

S S

Figura 2.8: Forma de onda da corrente no indutor para o conversor bidirecional.

Uma das caractersticas bsicas do conversor bidirecional a operao em dois qua-

drantes no plano(vxi). Ou seja, a partir de tenses terminais positivas, o conversor bidireci-

onal consegue forar a corrente por seu indutor a uir em ambos os sentidos. Por conveno

assume-se que durante a carga da bateria a corrente mdia no indutor, i

L

, positiva e

15

que durante a descarga a corrente tem polaridade inversa, isto , negativa. O estgio buck

do conversor bidirecional composto pelos dispositivos S

1

e D

2

, sendo que a energia ui

do barramento CC para o banco de baterias, enquanto que o estgio boost formado pe-

los dispositivos S

2

e D

1

e neste caso a energia ui do banco de baterias para o barramento

CC. Conforme ser mostrado adiante, o conversor bidirecional permite inverter o uxo de

energia de maneira rpida e eciente apenas controlando as razes cclicas das chaves se-

micondutoras controladas S

2

e S

1

, sem a necessidade de nenhum artifcio externo como

intertravamento dos dois estgios ou utilizao de dispositivo de manobra mecnica (rels

ou contatores) [22].

Para cada um dos estgios, buck ou boost, operando de forma independente possvel

observar a ocorrncia do modo de conduo descontnua (do ingls, Discontinuous Conduc-

tion Mode) (DCM), ou seja, poder ocorrer um perodo em que a corrente uindo pela chave

controlada e pelo diodo nula. Quando o DCM ocorre, a corrente para ou da bateria passa

a ser descontnua. J o conversor bidirecional no apresenta esse tipo de comportamento.

Controlado com as razes cclicas das chaves semicondutoras S

1

e S

2

de maneira comple-

mentar, conforme mostrado na Figura 2.8, o conversor bidirecional sempre ir operar no

modo de conduo contnua (do ingls, Continuous Conduction Mode) (CCM), com uma

chave controlada ou diodo conduzindo corrente.

2.5 Ondulaes CA

Na prtica existem discrepncias entre o tempo de vida das baterias fornecido pelos

fabricantes, normalmente obtidos atravs de ensaios em condies de laboratrios, e o tempo

observado nas aplicaes de campo, no qual a tenso e temperatura oscilam [23]. Na mai-

oria das aplicaes prticas, a carga da bateria com tenso e corrente no ltrados e/ou mal

reguladas so responsveis por falhas prematuras e pela reduo da vida til das mesmas.

fato que algumas ondulaes na corrente e tenso nos terminais das baterias usa-

das em aplicaes PV so inevitveis pois a energia eltrica convertida pelas clulas PV

fortemente dependente das condies de insolao. No caso em que o sistema de gerao

PV conectado rede eltrica apresenta-se ainda as componentes de freqncia mltiplas

de 120 Hz. Assumindo que a corrente no indutor do conversor bidirecional da Figura 2.7

seja idntica forma de onda mostrada na Figura 2.8 pode-se estimar o valor da ondulao

de corrente no indutor, I

L

, pela relao:

I

L

=

1

L

(V

1

V

2

)

V

2

V

1

1

f

, (2.4)

onde: f a freqncia de chaveamento do conversor;

L o valor da indutncia do conversor;

V

1

e V

2

so as tenses mdias de entrada e de sada do conversor bidirecional.

16

A anlise de (2.4) permite concluir que a ondulao I

L

independe do valor da

corrente de carga cujo valor mdio, i

L

, igual corrente mdia no indutor. Para calcular

o valor da indutncia, L, preciso preestabelecer um valor para I

L

e xar um valor para a

freqncia de chaveamento do conversor. O problema recai ento no fato de que a escolha

de um valor de I

L

muito pequeno resultar num valor excessivamente elevado de L que

por sua vez ir implicar em um indutor pesado, volumoso e caro.

Devido aos chaveamentos do conversor bidirecional observa-se ondulaes de alta

freqncia na tenso que alimenta o banco de baterias. A anlise da tenso de sada do con-

versor mostra a existncia de harmnicos em freqncias mltiplas da freqncia de chavea-

mento. Dessa maneira pode-se ento conectar um capacitor, C, em paralelo aos terminais da

bateria para minimizar a circulao de componentes de alta freqncia na tenso. O valor do

capacitor de sada normalmente escolhido para forar uma ressonncia com o indutor srie

cuja freqncia 100 a 1000 vezes menor que a freqncia de chaveamento do conversor.

Em muitos conversores bem projetados, as ondulaes devido ao chaveamento so

de pequena magnitude se comparados com a componente CC. Para a corrente no indutor,

um valor tpico para a ondulao na carga devido ao chaveamento de 10 % a 20 % da

componente CC. Para a tenso no capacitor de sada, a ondulao requerida tipicamente

menor que 1 % da tenso CC de sada [24].

Pode-se tambm projetar um ltro de terceira ordem (ltro T), que consiste de um

indutor adicional conectado em srie entre a bateria e os terminais de sada do conversor.

Neste caso a corrente de alimentao da bateria teria uma taxa de ltragem de 60 dB/dc.

Apesar de aumentar o nmero e componentes passivos essa soluo minimiza as ondulaes

de corrente e de tenso nos terminais das baterias, maximizando sua vida til [12].

H divergncias quanto aos nveis mximos de ondulaes permitidos em sistemas

de carga de baterias mas os fabricantes, usurios e instituies, como NEMA e IEEE, re-

conhecem que as ondulaes de fato afetam a vida til das baterias. O Johnson Controls

Battery Group, por exemplo, especica nveis mximos de ondulaes permissveis, para a

carga das baterias, na faixa de 0,5 % a 1,5 % RMS [23].

2.6 Modelagem de conversores estticos

Os conversores estticos, em um sistema, esto sujeitos a perturbaes. Estas podem

ocorrer tanto na sua fonte de alimentao quanto na carga. Dessa forma, para que a tenso

ou corrente do conversor seja mantida no valor desejado, mesmo ocorrendo perturbaes

dentro do sistema, necessria a implementao de uma malha de controle. Para projetar a

malha de controle em conversores estticos preciso determinar a funo de transferncia

do estgio de potncia do conversor.

17

O propsito de controlar conversores CC-CC instiga a busca de um modelo que re-

presente o seu comportamento dinmico. A diculdade surge devido a estes conversores

serem constitudos de dispositivos semicondutores, o que os leva a apresentar um comporta-

mento no-linear e variante no tempo. Essas diculdades podem ser superadas pelo uso de

tcnicas que utilizam a forma de onda mdia e o modelo de pequenos sinais [24]. A anlise

do comportamento dinmico destes conversores pode ser feita atravs de tcnicas de linea-

rizao desde que considerando pequenas variaes em torno do seu ponto de operao no

estado permanente, determinando assim o modelo dinmico de pequenos sinais.

No Apndice B so mostrados de maneira resumida os princpios das tcnicas de mo-

delagem de conversores baseadas na Mdia de Espao de Estados apresentado em detalhes

em [25] e [24] ou modelos equivalentes obtidos a partir do modelo da chave PWM proposto

em [26] e [27].

O modelo obtido para o conversor boost, em (B.9), mostra um sistema de fase no-

mnima devido presena de um zero na funo de transferncia G

d

(s) no semiplano direito

do planos para sistemas contnuos ou externo ao crculo unitrio no planoz para sistemas

discretos. Quando um zero est presente no semiplano direito difcil obter uma margem

de fase adequada em uma realimentao de lao simples convencional em sistemas que tm

elevada largura de banda. Deste modo h a necessidade da investigao de outras tcnicas

de controle.

2.7 Concluses parciais

A bateria chumbo-cido um dos dispositivos de armazenamento de energia mais

utilizados em aplicaes PV. Elas representam certa de 13 % dos custos iniciais e atingem

46 % dos custos de manuteno. Logo h a necessidade de se reduzir tais custos, o que se

consegue com investimentos nos controladores que representam somente 5 % dos custos.

Um aumento de 10 % em investimento nos controladores capaz de dobrar a vida til das

baterias. Dentre os fatores mais importantes para maximizar a vida til da bateria esto o

processo de carga e a diminuio das ondulaes na corrente e tenso.

Deste modo proposta a utilizao do conversor bidirecional CC-CC PWM como

visto na Figura 2.7 que possibilita a conduo de corrente em ambas as direes. Alm disso

de fcil realizao pois constitui-se de mdulos half-bridge. Este conversor possibilita

inverter o uxo de energia apenas controlando os sinais de disparo e sem o uso de qualquer

dispositivo mecnico.

Trabalhar com razo cclica complementar evita o DCM e permite obter um modelo

matemtico nico para o conversor bidirecional.

18

Captulo 3

Controle de Conversores Estticos

Ao se trabalhar com controle analgico ou digital muito importante saber avaliar a

estabilidade de um sistema. Uma das ferramentas mais utilizadas para se avaliar a estabili-

dade o critrio de Nyquist. Este critrio determina a estabilidade de um sistema de malha

fechada com base na resposta em freqncia de malha aberta e nos plos de malha aberta. A

funo de transferncia de malha fechada de um sistema como representado na Figura 3.1

visualizada em (3.1).

G( s)

H( s)

X( s) Y( s)

Figura 3.1: Diagrama de blocos de malha fechada.

Y (s)

X(s)

=

G(s)

1 +G(s)H(s)

, (3.1)

onde: Y (s) a varivel controlada;

X(s) o sinal de referncia;

H(s) a funo de transferncia do condicionamento de sinal;

G(s) a funo de transferncia da planta, do controlador e do modulador.

Para se obter estabilidade, todas as razes da equao caracterstica, que o denomi-

nador em (3.1), devem estar no semiplano esquerdo do planos. Vale observar que, embora

os plos e os zeros da funo de transferncia de malha aberta, G(s)H(s), possam estar no

semiplano direito do planos, o sistema ser estvel se todos os plos da funo de transfe-

rncia de malha fechada (isto , as razes da equao caracterstica) estiverem no semiplano

esquerdo do plano-s.

19

O critrio de estabilidade de Nyquist relaciona a resposta em freqncia de malha

aberta, G(j)H(j), ao nmero de zeros e plos da equao caractersticas que se situam no

semiplano direito do planos. Este critrio til porque a estabilidade absoluta do sistema

de malha fechada pode ser determinada gracamente a partir das curvas de resposta em

freqncia de malha aberta e no h necessidade de determinar de maneira efetiva os plos

de malha fechada [28].

As margens de fase e de ganho de um sistema de controle so uma medida da pro-

ximidade do diagrama polar em relao ao ponto 1 + j0. Portanto, essas margens podem

ser utilizadas como critrios de projetos. importante notar que apenas a margem de ganho

ou apenas a margem de fase no fornece indicao suciente sobre a estabilidade relativa.

Ambas devem ser fornecidas pra determinao da estabilidade relativa.

Para um sistema de fase mnima, as margens de fase e de ganho devem ser positi-

vas para que o sistema seja estvel. Margens negativas indicam instabilidade. Margens de

fase e de ganho apropriadas protegem contra variaes nos componentes do sistema e so

especicadas por valores positivos denidos. Os dois valores limitam o comportamento do

sistema de malha fechada nas proximidades da freqncia de ressonncia. Para obter um

desempenho satisfatrio, a margem de fase deve estar entre 30

o

e 60

o

e a margem de ganho

deve ser maior que 6dB [28]. Com estes valores, um sistema de fase mnima tem estabilidade

garantida, mesmo que o ganho de malha aberta e as constantes de tempo dos componentes

variem dentro de certos limites.

3.1 Controle modo tenso

O sistema de um conversor esttico realimentado mostrado na Figura 3.2. A tenso

v

2

(s) medida utilizando um condicionamento de sinal cuja funo de transferncia re-

presentada por H

2

(s). Em controle analgico, normalmente, este sensor composto por um

circuito divisor de tenso resistivo e seu comportamento modelado como ganho de tenso,

que condiciona a tenso v

2

(s) a nveis compatveis com o circuito de controle.

d( s)

i ( s)

C ( s)

L

v

P WM

Mo d e l o m d i o

do est gi o

de pot nc i a

v ( s) v ( s)

H ( s)

2 1

2

v* ( s)

2

v ( s)

C

e ( s)

v

Figura 3.2: Diagrama do controle modo tenso.

Osinal aps o condicionamento, H

2

(s)v

2

(s), comparado coma tenso de referncia

v

2

(s), a m de tornar H

2

(s)v

2

(s) igual a v

2

(s), fazendo com que v

2

(s) siga v

2

(s)/H

2

(s)

independente das perturbaes impostas ao conversor. A diferena entre H

2

(s)v

2

(s) e v

2

(s)

20

denominado sinal de erro, e

v

(s). Para fazer com que o sinal de erro seja bem prximo de

zero preciso melhorar as caractersticas dinmicas e a estabilidade do conversor, incluindo

assim um compensador C

v

(s) na malha de realimentao. No contexto de eletrnica de

potncia, h uma tcnica bastante difundida, proposta por Venable [29], denominada The k

factor. Esta tcnica utiliza um compensador de avano de fase na correo das margens de

fase e de ganho.

Diante da perturbao, o sistema deve retornar rapidamente a seu valor de regime. O

tempo de resposta do sistema pode ser reduzido com o aumento do valor da freqncia de

cruzamento de ganho. Teoricamente, a freqncia de cruzamento de ganho poderia assumir

valores at metade da freqncia de comutao. Entretanto, para rejeitar as perturbaes

provenientes da comutao do conversor e garantir sua estabilidade para grandes sinais, a

freqncia de cruzamento de ganho deve ser limitada a 1/10 da freqncia de comutao,

garantindo sua atenuao em, pelo menos, 20 dB.

O modelo do conversor boost, G

d

(s), apresenta um zero,

z

, na regio de instabili-

dade como observado em (B.9) e na Tabela B.2. Portanto, diz-se que este um sistema de

fase no mnima. Como visto anteriormente a estabilidade s garantida atravs da margem

de fase e de ganho quando o sistema de fase mnima. Logo a utilizao de compensadores

de avano de fase pode no ser suciente para garantir a estabilidade deste sistema. Por isso

buscam-se outras tcnicas como o mtodo de controle analgico por corrente.

3.2 Controle modo corrente

O controle modo corrente (do ingls, Current Programmed Mode) (CPM) um sis-

tema com duas realimentaes como mostrado na Figura 3.3, onde visualiza-se o CPM de

pico. Um lao de controle interno, de corrente, proposto para simplicar o projeto do lao

externo, de tenso. O objetivo desta nova realimentao controlar a corrente mdia no in-

dutor em regime permanente, mas na prtica o controle feito com base na corrente de pico.

Conversores controlados pelo lao de corrente so ditos operando em CPM [30] e [31].

Este controle tem diversas aplicaes em conversores CC-CC e em correo de fator

de potncia (do ingls, Power Factor Correction) (PFC) [32] [33] e uma de suas vantagens

a aplicao em paralelismo de conversores CC-CC. O paralelismo proporciona um aumento

da potncia nominal, uma melhoria da conabilidade e permite futuras expanses do sistema

[34].

Para o CPM h variantes que esto relacionadas forma de comparao entre a cor-

rente no indutor e corrente de referncia. Deste modo, pode-se classicar o CPM em vale,

pico ou mdia. O fato de controlar a corrente no indutor possibilita uma dinmica simples

e robusta. Dentre as variaes citadas, o mtodo de CPM mdia o mais indicado por ter

maior imunidade a rudo, operar com freqncia constante e no precisar da rampa de com-

pensao.

21

3.2.1 Controle modo corrente de pico

O CPM de pico tem como princpio de funcionamento a comparao da rampa de

subida da corrente no indutor, i

L

, com um nvel de corrente de referncia, i

C

. A sada do

comparador vai a nvel lgico zero quando a corrente instantnea atravs do indutor atinge

o nvel de referncia. A diferena entre as inclinaes da corrente no indutor e da corrente

de referncia normalmente muito pequena, especialmente quando a tenso v

1

(s) rela-

tivamente baixa. Conseqentemente este mtodo extremamente suscetvel a rudos. A

Figura 3.3 mostra o circuito do CPM de pico para o conversor esttico e as formas de onda

caractersticas.

v ( s)

d( s)

v ( s)

i ( s)

H ( s)

C ( s)

L

2 1

2

v

i * ( s)

L

v* ( s)

2

i ( s)

C

Mo d e l o m d i o

do est gi o

de pot nc i a

Fo r ma s d e o n d a

i

C

i

L

d

La t c h

Q

S

R

Figura 3.3: Diagrama do CPM de pico.

3.2.2 Controle modo corrente de pico com compensao em rampa

O CPM de pico por natureza instvel para razes cclicas superiores a 0,5 apresen-

tando oscilaes na resposta do sistema [30], [33]. A Figura 3.4 mostra a compensao em

rampa, v

S

, que normalmente aplicada entrada do comparador, para eliminar a instabili-

dade. Tambm observam-se as formas de onda caractersticas.

d( s)

i ( s)

C ( s)

L

v

i ( s)

C

Mo d e l o m d i o

do est gi o

de pot nc i a

Fo r ma s d e o n d a

i

C

i

L S

d

v ( s)

S

i ( s)

L S

v

S

La t c h

Q

S

R

v ( s) v ( s)

H ( s)

2 1

2

i * ( s)

L

v* ( s)

2

Figura 3.4: Diagrama do CPM com compensao em rampa.

22

3.2.3 Controle modo corrente mdia

O CPM de pico opera comparando diretamente a forma de onda da corrente atual

com a corrente de referncia que obtida pela realimentao externa. A tcnica de CPM

mdia [33] supera os problemas dos outros mtodos por introduzir um alto ganho, C

i

(s), no

erro da realimentao interna de corrente como indicado na Figura 3.5. A partir deste sinal

gerado o sinal PWM de modo semelhante ao controle modo tenso.

d( s)

i ( s)

C ( s) C ( s)

L

v i

i ( s)

C

P WM

Mo d e l o m d i o

do est gi o

de pot nc i a

v ( s) v ( s)

H ( s)

2 1

2

i * ( s)

L

v* ( s)

2

v ( s)

C

e ( s)

v

e ( s)

i

Figura 3.5: Diagrama do CPM mdia.

O controle de corrente analgico deciente em alguns aspectos devido a fatores

como a sensibilidade a variao de parmetros e a alta ondulao da corrente no indutor

a ser ltrada. Por esses e outros fatores h atualmente uma tendncia de substituio do

controle analgico pelo controle digital.

3.3 Implementao do controlador digital

O controle digital aplicado a conversores estticos recebe atualmente uma grande

ateno do meio acadmico bem como da indstria, atribudo ao fato deste possuir inmeras

vantagens. Entre elas citam-se a (i) baixa sensibilidade a variaes dos parmetros; (ii) redu-

o do nmero de componentes passivos; (iii) possibilidade de implementao de controles

avanados, proteo e algoritmos de calibrao e (iv) exibilidade, o que permite modicar

o projeto das estratgias de controle, ou reprogram-lo totalmente sem precisar fazer modi-

caes signicantes no hardware. No projeto de controladores digitais importante tambm

o desenvolvimento de sistemas tolerantes a rudos e que apresentem um desempenho ro-

busto frente ao envelhecimento dos componentes do controlador e variao da temperatura

ambiente [35] e [36].

Almdisso, a fabricao dos microcontroladores e DSPs realizada de forma a tornar

acessvel a alta performance e o baixo custo dos processadores com perifricos adequados

para o controle de conversores estticos, o qual inclui ADC com mltiplos canais, encoders

e gerador PWM [37].

23

3.3.1 Processamento digital de sinais de tempo contnuo

O circuito de interface de converso do sinal de tempo contnuo para a forma digital

denominado ADC. Igualmente, a operao reversa de converso de um sinal digital em um

sinal de tempo contnuo implementado pelo circuito de interface denominado Conversor

D/A (DAC), que normalmente em hardwares digitais dedicados a conversores estticos so

representados pela modulao por largura de pulso digital (do ingls, Digital Pulse Width

Modulation) (DPWM). O diagrama de blocos da Figura 3.6 ilustra os requerimentos funcio-

nais para o processamento digital de sinais de tempo discreto de um sinal de tempo contnuo.

Fi l t r o

x ( t )

a

S/ H A/ D D P W M

Pr oc e s s a dor

di gi t al

x[ n] y[ n] x ( t )

d

a n t i - a l i a s i n g

Figura 3.6: Diagrama de blocos do controle digital.

Alm do ADC e do DAC necessria a incluso de outros dispositivos como o amos-

trador/retentor (do ingls, Sample/Hold) (S/H). Este circuito fundamental quando a con-

verso de analgico para digital normalmente feita em um tempo nito, pois garante que

o sinal analgico de entrada do ADC no contenha resduos na amplitude at que a con-

verso se torne completa, evitando assim erros na representao do sinal [38]. O diagrama

esquemtico de um circuito S/H mostrado na Figura 3.7.

Font e

do si nal

R R

C

S

C

V

S O N

P H

O U T

A DCI N

Figura 3.7: Circuito esquemtico do S/H - TMS320F2812.

Dado o inicio da amostragem, decorre-se um tempo para que o sinal seja dispo-

nibilizado na sada do S/H. necessrio preestabelecer o tempo no qual o dispositivo S

dever ser mantido ligado para que a amostragem seja realizada de maneira correta como

visualizado na Figura 3.8, este intervalo de tempo denominado janela de aquisio. As

limitaes fsicas, ou seja, a impedncia da fonte do sinal e a impedncia de entrada, limitam

a mxima freqncia de amostragem, f

S

, de operao do ADC. O DSP TMS320F2812

da Texas Instruments, por exemplo, tem os seguintes parmetros para o S/H: C

P

= 10 pF,

C

H

= 1,25 pF e R