Professional Documents

Culture Documents

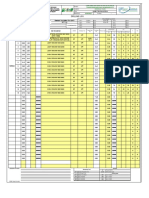

PXC 3871467

Uploaded by

aditya414Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PXC 3871467

Uploaded by

aditya414Copyright:

Available Formats

International Journal of Computer Applications (0975 8887) Volume 7 No.

5, September 2010

Standby Leakage Reduction in Nanoscale CMOS VLSI Circuits

Dhananjay E. Upasani

H.O.D. E&Tc &IT Sinhgad Institute of Technology & Sci. Narhe,Pune-411041

Sandip B. Shrote

Lect.E & Tc Deptt. SGREFS, COEM,Ahmednagar Ahmednager

Pallavi S.Deshpande

Asst.Prof.E&TC Dept. Sinhgad Institute of Technology & Sci. Narhe,Pune-411041

ABSTRACT

Most of the portable systems, such as cellular communication devices, and laptop computers operate from a limited power supply. Devices like cell phones have long idle times and operate in standby mode when not in use. Consequently, the extension of battery-based operation time is a significant design goal which can be made possible by controlling the leakage current flowing through the CMOS gate. This article reviews the off-state leakage mechanisms like weak inversion leakage, gate induced drain leakage and channel punchthrough current. Various circuit level techniques to reduce standby leakage and their design trade-off are discussed. Based on the surveyed techniques, a designer would be able to select the appropriate leakage optimization technique for a standby mode. Categories and Subject Descriptors B.7.1 [Integrated Circuits]: Types and Design Styles VLSI (very large scale integration). General Terms Documentation and Theory Keywords Standby leakage, LECTOR, GALEOR

threshold leakage, which is pattern dependent as it only occurs in off transistors. Hence, this necessitates the need for robust techniques to reduce this leakage power dissipation. To this effect, several techniques have been proposed that efficiently minimize leakage power dissipation. This paper is organized as follows: leakage sources in an MOS transistor are discussed in details in section II; this is followed by a comprehensive survey of Standby mode leakage reduction techniques in section III. Finally, section IV gives some final conclusions.

2. LEAKAGE MECHANISMS IN STANDBY

Subthreshold Leakage current (ISUB) is the most dominant leakage current component in standby mode amongst the different leakage current mechanisms contributing to the total leakage in CMOS circuits which are depicted in Figure 1[1].

1. INTRODUCTION

Low-power consumption in high performance VLSI circuits is highly desirable aspect as it directly relates to battery life, reliability, packaging, and heat removal costs .With the continuous trend of technology scaling, leakage power is becoming major contributor to the total power consumption in CMOS circuits. Scaling of Vdd reduces dynamic power consumption but degrades the performance of the circuit as well. This can be partially compensated by lowering Vth but at the cost of increased leakage power. Minimizing leakage power consumption is currently an extremely challenging area of research, especially with on-chip devices doubling every two years. Leakage power dissipation arises from the leakage currents flowing through the transistor when there are no input transitions and the transistor has reached steady state. Unlike dynamic power, leakage power depends on the total number of transistors in the circuit, their types, and their operation status regardless of their switching activity. This makes it more difficult to attempt to reduce leakage power than to reduce dynamic power. Leakage current constitutes only of sub-

Figure 1. Different Leakage Current Mechanisms in CMOS transistor

2.1 Subthreshold Leakage:

The subthreshold current is the current between the source and the drain of the transistor in weak inversion mode, which is also known as Weak Inversion conduction Current. Subthreshold current flows by carrier diffusion rather than drift along the channel surface due to nonzero minority carrier concentration. The following parameters affect the threshold voltage and hence the subthreshold leakage current:

2.1.1 Drain-Induced Barrier Lowering (DIBL):

The barrier lowering effect is observed by a shift of threshold voltage as a function of drain voltage of short channel device. In short channel MOSFET, it is well known that the depletion 1

International Journal of Computer Applications (0975 8887) Volume 7 No.5, September 2010 width at source and drain junction become comparable to the channel length. The effect of decreasing channel length caused the depletion region width surround the source and drain diffusion to approach each other. Depending on the drain bias, the electric field at the drain can penetrate to the source region of the device caused the decreasing of potential barrier at source. As a result, the device can conduct significant drain current due to an increase of carrier injected from the source [2]. This mechanism is responsible for the strong dependence of subthreshold current on the drain bias. Moreover the subthreshold current will change the threshold voltage as the drain bias is varied. through level. An additional implants at bottom or edges of the source and drain junction boundaries can control the punch through.

3. SURVEY OF STANDBY MODE LEKAGE REDUCTION TECHNIQUES 3.1 Self- Reverse Bias/Natural Transistor Stacks

Self- reverse biasing is a technique which helps to reduce subthreshold leakage current by turning off a stack of transistors [4]. This stacking effect is achieved by exploiting the dependency of subthreshold current on source voltage VS as depicted in figure 3. Increase in VS results in: Negative VGS if the applied input is grounded, Decreases signal strength (VCC-VS), Reduces DIBL due to reduction in VDS causing leakage reduction Negative VBS (body effect); thereby reducing sub threshold leakage current exponentially. More are the number of off transistors in a natural stack; less is the leakage due to raised source voltage as shown in figure 4. Sub threshold leakage through logic gate is dependent on applied

2.1.2 Effect of body bias

The expression (1) of threshold voltage for substrate bias reflects the influence of the nonzero source to substrate voltage upon the device characteristic as: VT (VSB) = VTO + [(|2F|+VSB) - (|2 F|) ] (1) Where, VT (VSB) is the zero substrate-bias threshold voltage which mainly depends on the manufacturing process; is the substrate bias coefficient (typically equals to 0.4V-0.5V) and it depends on the gate oxide capacitance, silicon permittivity, doping level, and other parameters; F is the Fermi potential; VSB is the substrate bias potential. Increase in substrate reverse bias increases the threshold voltage. As per the decrease in supply voltage and body bias, leakage power decreases with decrease in threshold voltage for 45 nm technology. Hence optimal body bias is to be determined to minimize leakage.

2.1.3 Effect of temperature

Temperature dependence of threshold voltage affects the subthreshold leakage current. Increase in leakage current with temperature for a given technology [3]. Threshold voltage has temperature sensitivity of 8mV/ C. Figure 2. Leakage current descendants with the number of transistors OFF in stack input vector. But under high gate leakage conditions, natural stacking fails to reduce leakage; rather it might increase the overall leakage [5]. However, circuits in which natural stacking does not exist; forced stacking is used [6]. Forced stacking utilizes the stacking effect by introducing an additional transistor for every input of the gate in both NMOS and PMOS networks. By replacing a single transistor of width W by two transistors each whose width is W/2 ensures that two transistors are OFF instead of one for every OFF-input of the gate which makes a significant savings on the leakage current. Reducing leakage through the use of transistor stacks depends on the choice of input pattern during standby periods since it determines the number of OFF transistors in the stack. The work in [7] exploits an idea of an effective stacking of transistors in the path from supply voltage to ground. Two leakage control transistors (LCTs) are introduced in each CMOS gate such that one of the LCTs is near its cutoff region of operation. Drawbacks like propagation delay and area overhead 2

2.2 Gate Induced Drain Leakage (IGIDL):

The carriers responsible for GIDL, an off-state drain leakage, originate in the region of the drain that is overlapped by the gate, under accumulation condition when the gate is grounded and the drain is at VDD. Since the substrate is at a lower potential for minority carriers, the minority carriers that have been accumulated or formed at the drain depletion region underneath the gate are swept laterally to the substrate, completing a path for the GIDL. GIDL is minimized by incorporating very high and abrupt drain doping, as it provides lower series resistance required for high transistor drive currents.

2.3 Punch Through:

Merging of the depletion regions at the drain-substrate and source-substrate junctions due to short channel and increased reverse bias across junctions is called as punch through. Subthreshold current increases due to the increase in majority carriers generated in the source and collected at the drain end due to the increase in the drain voltage beyond required punch

International Journal of Computer Applications (0975 8887) Volume 7 No.5, September 2010 are overcome by transistor sizing and using SCCG gates for LECTOR (LEakage Control TransistOR) respectively. In [8], a technique called as GALEOR (GAted LEakage TransistOR) is introduced which achieves 52% savings in leakage power compared to 30% power reduction obtained using LECTOR which is depicted in figure 4. Area overhead is minimized by eliminating the use of control logic to switch between the active and standby states. Vth power switches (sleep transistors) to low-Vth logic cell blocks. As supply voltage is scaling down continuously, high V th transistors cannot operate with supply voltages equal to or below than 0.7V. To cope with this issue, the Boosted Gate MOS scheme [14] was introduced. The gate overdrive of this high- Vth, thick gate oxide transistor is drastically improved by applying a higher than gate-to-source voltage. This scheme has the added advantage of lowering the gate tunneling currents. The MVCMOS [15] is similar to Super Cutoff CMOS power switch [16]. It is a low- Vth transistor whose leakage current is exponentially reduced by reverse-biasing its gate, rendering the gate-to-source voltage negative in the case of an nMOS transistor and positive in the case of a pMOS one. The main advantages of this power switch are its small size and the fact that it performs pretty well in a low- Vth environment. To achieve maximum leakage reduction, automatic gate biasing of Super Cut-off CMOS (SCCMOS) switch [17] is done using a polarization circuit that automatically finds the optimal gate bias voltage whatever the environment condition.

3.2 Sleep Transistor, MTCMOS and Power Switches

Another way for leakage current control is inserts sleep transistor in series with the pull-down/pull-up path of a gate.There are two insertion schemes-PMOS and NMOS insertion. Due to the advantages like smaller resistance at the same width and smaller size, NMOS scheme is preferable than PMOS scheme [9].

3.3 Body Biasing

Power consumption can be reduced by using low supply voltage and low threshold voltage without loosing speed performance; but it leads to increased subthreshold leakage and hence standby power consumption. One of the methods proposed to solve this problem is VTCMOS which utilizes body effect. The threshold voltage of the low threshold devices is controlled by applying variable substrate bias voltage Vbs. This is varied by making the substrate voltage lower than ground for NMOS transistors and higher than supply voltage for PMOS transistors. The advantage of VTCMOS scheme is no extra circuit is required for the data retention. But VTCMOS needs triple well technology to achieve different substrate bias voltage levels which adds complexity of structure as shown in figure 11. It also needs separate substrate bias voltage generator.

Figure 4. Power Gating Circuit and Mechanisms In such a circuit, the supply voltage is turned off during the standby mode by using a PMOS transistor or an NMOS transistor. In active mode, the sleep transistor is on and the circuit functions as usual. The basic mechanism by which the switch transistor reduces the leakage current of the power gated logic transistors is the increased body effect: the increased source voltage of the logic transistors, relative to their bodies, raises their thresholds [10]. The resulting current flow from the power or to the ground is substantially reduced. Since this high V th sleep transistor acts as a current gate to the designed circuit, this technique is also referred to as Power Gating. Power gating circuit and leakage reduction mechanisms are depicted in Figure 4 [11]. The topology, which is known as MTCMOS described in [12] and [13], reduces leakage effectively by inserting a highthreshold voltage sleep transistor in series with the power supply and the existing design and ground. MTCMOS can only reduce leakage power in standby mode and the large inserted sleep transistors can increase the area and delay. Sizing of the sleep transistors is an important design consideration. Usage of large transistor solves the delay problem incurred due to voltage drop; but it increases the area overhead and the dynamic power consumption. To reduce this area and power overhead, one transistor can be used for each group of gates rather than each logic gate. The Power switch transistors which are inserted inbetween the logical circuit and the supply/ground lines are very effective in cutting the leakage currents in a standby mode by desupplying unused blocks. MTCMOS technique, as discussed earlier, can significantly reduce the subthreshold leakage currents during the circuit sleep (standby) mode by adding high-

Figure 5. VTCMOS Scheme Body biasing techniques use the body terminal bias values as another control mechanism to dynamically tune threshold voltages. Reverse body biasing is often used to reduce the device leakage power. For every process technology there is an optimum reverse body bias. Article [18] proposes a new optimal body biasing system to balance the subthreshold leakage with the BTBT leakage. In this, the threshold voltage is increased by adjusting body-bias voltage in RBB direction and when the optimal body bias is reached, the body voltage adjustment is stopped to avoid excessive reverse body bias.

International Journal of Computer Applications (0975 8887) Volume 7 No.5, September 2010

4. CONCLUSION

As technology scales down to the deep sub-micron (DSM) domain, chip power dissipation and power density are increasing rapidly. With deep-submicron and nanometer technologies, the leakage current becomes more critical in portable systems where battery life is of prime concern. In view to this, we stress the importance of leakage current in CMOS circuits. In this paper, several leakage mitigation techniques are explored that can control standby leakage. Based on the surveyed techniques, a designer would be able to select the appropriate leakage optimization technique for a particular level of an application.

Conference on Electronics, Circuits and Systems, 2008, Volume, Issue, Aug. 31 2008-Sept. 3 2008 Page(s):574 577 [6] [10] Kao J., Chandrakasan A. and Antoniadis D., Transistor sizing issues and tool for multi-threshold CMOS technology, in Proc. ACM/IEEE Design Automation Conf., pp. 495500, 1997. [7] [11] Kao, J. T., and Chandrakasan, A. P. Dual-Threshold Voltage Techniques for Low-power Digital Circuits, IEEE Journal of Solid-State Circuits 35, pp.1009-1018, 7 (July 2000). [8] [12] Ken Choi and Jerry Frenkil, An Analysis Methodology for Dynamic Power Gating, Sequence Design Inc, pp. 1- 13, 26 (July 2007). [9] [13] J. Kao, A. Chandrakasan, and D. Antoniadis,Transistor sizing issues and tool for multi-threshold CMOS technology, in Proc. 34th DAC, 1997, pp. 409414. [10] [14] C. Gopalakrishnan and S. Katkoori, Resource allocation and binding approach for low leakage power, in Proc. IEEE Int. Conf. VLSI Design,Jan. 2003, pp. 297302. [11] [15] T. Inukai, M. Takamiya, K. Nose, H. Kawaguchi, T. Hiramoto, and T. Sakurai, Boosted gate MOS (BGMOS): device/circuit cooperation scheme to achieve leakage-free gigascale integration, in Proc. IEEE Custom Integrated Circuits Conf., pp. 409412, May 2000. [12] [16] M. R. Stan, Low threshold CMOS circuits with low standby current, in Proc. Int. Symp. Low Power Electronics and Design (ISLPED), pp. 9799, Aug. 1998. [13] [17] H. Kawaguchi, K. Nose, and T. Sakurai, A CMOS scheme for 0.5 V supply voltage with pico-ampere standby current, in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 192193, Feb. 1998. [14] [18] Alexandre Valentian and Edith Beigne, Automatic Gate Biasing of an SCCMOS Power Switch Achieving Maximum Leakage Reduction and Lowering Leakage Current Variability, IEEE J. OF Solid-State Circuits, vol. 43, no. 7, July 2008. [19] Kyung Ki Kim; Yong-Bin Ki, Optimal Body Biasing for Minimum Leakage Power in Standby Mode, IEEE International Symposium on Circuits and Systems, 27-30 May 2007, Page(s):1161 1164.

5. REFERENCES

[1] K. Roy, S. Mukhopadhyay and H.Mahmoodi-Meimand, Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits, In the Proceedings of the IEEE, vol. 91, no. 2, pp. 305327, [2] M.Jamal Dean, DIBL in Short Channel NMOS Devices, IEEE Transaction on Electron Devices, Vol39, No4, 908- 915, 1992 [3]Farzan Fallah and Massoud Pedram, Standby and Active Leakage Current Control and Minimization in CMOS VLSI Circuits, IEICE transactions on electronics, vol. 88, no.4, pp. 509-519, 2005 [4]Y. Ye et al. IEEE Symposium on VLSI Circuits, 1998. [1] [5] S. Mukhopadhyay, IEEE Transactions on VLSI Systems, 2003. [2] [6] S. Narendra, S. Borkar, V. De, D. Antoniadis, and A. P. Chandrakasan, Scaling of stack effect and its application for leakage reduction, Proc. IEEE ISLPLED, pp. 195 200, Aug. 2001. [3] [7] S. Narendra, S. Borkar, V. De, D. Antoniadis, and A. P. Chandrakasan, Scaling of stack effect and its application for leakage reduction, Proc. IEEE ISLPLED, pp. 195 200, Aug. 2001. [4] [8] N. Hanchate and N.Ranganathan, LECTOR: A Technique for Leakage Reduction in CMOS Circuits, IEEE Transactions on VLSI Systems,vol. 12, pp. 196-205, Feb, 2004. [5] [9] Srikanth Katrue and Dhireesha Kudithipudi, GALEOR: Leakage Reduction for CMOS Circuits, 15th IEEE International

You might also like

- Legend of Vinayaka ChavithiDocument6 pagesLegend of Vinayaka Chavithiaditya414No ratings yet

- New Text DocumentDocument1 pageNew Text Documentaditya414No ratings yet

- Java Collection Interview QuestionsDocument4 pagesJava Collection Interview Questionsaditya414No ratings yet

- JCL SampleDocument2 pagesJCL Sampleaditya414No ratings yet

- Vlsi Mtech Jntu Kakinada SyllabusDocument11 pagesVlsi Mtech Jntu Kakinada Syllabusaditya414No ratings yet

- VEDA Institute of Information Technology Pvt. LtdDocument2 pagesVEDA Institute of Information Technology Pvt. Ltdaditya414No ratings yet

- 136Document5 pages136aditya414No ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Harris Ts100 User ManualDocument24 pagesHarris Ts100 User ManualMiguel Alfonso Ruiz MendezNo ratings yet

- Lab 7 Configuring and Verifying Static NATDocument5 pagesLab 7 Configuring and Verifying Static NATrehsif nam100% (1)

- AssignmentDocument14 pagesAssignmentapi-561990701No ratings yet

- Manual CX600 X8Document261 pagesManual CX600 X8volicon voliconNo ratings yet

- Micro Focus®Document6 pagesMicro Focus®pncsatishNo ratings yet

- LCD 20x4B DatasheetDocument1 pageLCD 20x4B DatasheetyopisukitaNo ratings yet

- Measurement of NPK, Temperature, Moisture, Humidity Using WSNDocument6 pagesMeasurement of NPK, Temperature, Moisture, Humidity Using WSNFajar AnugrahNo ratings yet

- Autosar TR SwcmodelingguideDocument57 pagesAutosar TR SwcmodelingguideRadu ButnaruNo ratings yet

- Epp Delivery Format and Personal Provision BRCDocument3 pagesEpp Delivery Format and Personal Provision BRCScribdTranslationsNo ratings yet

- ArrayDocument32 pagesArraydhun1513.be22No ratings yet

- Newbay 13mic Gude PDFDocument36 pagesNewbay 13mic Gude PDFjgcalocaNo ratings yet

- Résumé For Arjun JayaramanDocument1 pageRésumé For Arjun JayaramanArjun JayaramanNo ratings yet

- A 24-Ghz Full-360 ° Cmos Reflection-Type Phase Shifter Mmic With Low Loss-VariationDocument4 pagesA 24-Ghz Full-360 ° Cmos Reflection-Type Phase Shifter Mmic With Low Loss-VariationSàRâh ËłâbïàdNo ratings yet

- Plannerplus: Automated Capacity Management For Optimized Network DesignsDocument4 pagesPlannerplus: Automated Capacity Management For Optimized Network DesignsPrasanna GanesanNo ratings yet

- Pa3X Factory ResetDocument12 pagesPa3X Factory ResetAnonymous qz5pEMh44No ratings yet

- Happy Plugs Air 1 ManualDocument1 pageHappy Plugs Air 1 ManualHalley JiménezNo ratings yet

- 3MZ-FE EngineDocument51 pages3MZ-FE Engineelijahcoles1990No ratings yet

- Modelling and Simulation PV Station VRTDocument4 pagesModelling and Simulation PV Station VRTDaniel ManjarresNo ratings yet

- Vehicle Running Account (Vra) December 2022 RCCKDocument12 pagesVehicle Running Account (Vra) December 2022 RCCKm.fadhlyaugustami fadhlyNo ratings yet

- Erp KPL Jul16Document192 pagesErp KPL Jul16sriiyer85No ratings yet

- Telefone IP 8002 - 80012Document3 pagesTelefone IP 8002 - 80012Ronaldo JoseNo ratings yet

- Gill - Stealth Racer - W017 - Instruction Manual - enDocument27 pagesGill - Stealth Racer - W017 - Instruction Manual - enalmoghaddamNo ratings yet

- CJ - CP 300 IM 10052125-AC EnglishDocument26 pagesCJ - CP 300 IM 10052125-AC EnglishFarissa ACHIROU ALASSANENo ratings yet

- Objective: TH STDocument3 pagesObjective: TH STAmzal AhamedNo ratings yet

- cpp5gs PDFDocument2 pagescpp5gs PDFmohammadNo ratings yet

- Ultimate Windows Tweaker 4 For Windows 10Document4 pagesUltimate Windows Tweaker 4 For Windows 10lehaphuong03No ratings yet

- Stepper MotorDocument26 pagesStepper MotorSupriya Rakshit100% (1)

- Limits of Variations of Inlet Steam ConditionsDocument1 pageLimits of Variations of Inlet Steam ConditionsShashi NaganurNo ratings yet

- Chapter 3!: Agile Development!Document21 pagesChapter 3!: Agile Development!Irkhas Organ SesatNo ratings yet

- 12drilling Log Spt04 160622Document2 pages12drilling Log Spt04 160622Angelica E. Rabago LopezNo ratings yet