Professional Documents

Culture Documents

Máquina de Estados

Uploaded by

NATHALIA175Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Máquina de Estados

Uploaded by

NATHALIA175Copyright:

Available Formats

Mquina de estados

Se ha sugerido que este artculo o seccin sea fusionado con Autmata finito (discusin).

Una vez que hayas realizado la fusin de artculos, pide la fusin de historiales aqu.

Se denomina mquina de estados a un modelo de comportamiento de un sistema con entradas y salidas, en donde las salidas dependen no slo de las seales de entradas actuales sino tambin de las anteriores. Las mquinas de estados se definen como un conjunto de estados que sirve de intermediario en esta relacin de entradas y salidas, haciendo que el historial de seales de entrada determine, para cada instante, un estado para la mquina, de forma tal que la salida depende nicamente del estado y las entradas actuales.

Una mquina de estados se denomina mquina de estados finitos (FSM por finite state machine) si el conjunto de estados de la mquina es finito, este es el nico tipo de mquinas de estados que podemos modelar en un computador en la actualidad; debido a esto se suelen utilizar los trminos mquina de estados y mquina de estados finitos de forma intercambiable. Sin embargo un ejemplo de una mquina de estados infinitos sera un computador cuntico esto es debido a que los Qubit que utilizara este tipo de computadores toma valores continuos, en contraposicin los bits toman valores discretos (0 1). Otro buen ejemplo de una mquina de estados infinitos es una Mquina universal de Turing la cual se puede definir tericamente con una "cinta" o memoria infinita.

La representacin de una mquina de estados se realiza mediante un Diagrama de estados, sin embargo tambin es posible utilizar un Diagrama de flujo.

Es posible clasificar las mquinas de estados en aceptoras o transductoras:

Aceptoras (tambin llamadas reconocedoras o discriminadoras): Son aquellas en donde la salida es binaria (s/no), depende nicamente del estado y existe un estado inicial. Puede decirse, entonces, que cuando la mquina produce una salida "positiva" (es decir, un "si"), es porque ha "reconocido" o "aceptado" la secuencia de entrada. En las mquinas de estados aceptoras, los estados con salida "positiva" se denominan estados finales.

Transductoras: Son las ms generales, que convierten una secuencia de seales de entrada en una secuencia de salida, pudiendo sta ser binaria o ms compleja, depender de la entrada actual (no slo del estado) y pudiendo tambin prescindirse de un estado inicial.

La bibliografa a veces llama autmata finito a las aceptoras, mientras que en otros casos se emplea autmata como sinnimo de mquina de estados sin importar su tipo.

Las aceptoras son los de mayor inters en la Teora de la Computacin, ms precisamente en la Teora de autmatas, siendo stas ramas de la matemtica. Las transductoras, en cambio, lo son en la electrnica digital y la computacin prctica. Es por eso que, por lo general, en los textos sobre matemtica y ciencias de la computacin se suele hablar de autmatas (y se refieren a las aceptoras) mientras que los de electrnica y computacin prctica hablan de mquinas de estados (y se refieren a los transductoras).

En UML (Lenguanje Unificado de Modelado), dice que una mquina de estado es aquel comportamiento que permite hacer un seguimiento de la vida de un objeto en el transcurso de un tiempo finito.

Categora:

Programacin

You might also like

- Parte Interna de La ComputadoraDocument3 pagesParte Interna de La Computadorañaña04100% (1)

- Introducción A Finanzas Evaluacion FinalDocument5 pagesIntroducción A Finanzas Evaluacion Finaldarien stivenNo ratings yet

- Manual Asistente EjecutivaDocument53 pagesManual Asistente EjecutivaTeresa De Jesús Juárez GutiérrezNo ratings yet

- Syllabus Del Curso Seguridad en Aplicaciones WebDocument9 pagesSyllabus Del Curso Seguridad en Aplicaciones WebJimmy SalcedoNo ratings yet

- Negra AaaaaaaaaaaaaaaDocument17 pagesNegra AaaaaaaaaaaaaaaNATHALIA175No ratings yet

- Base de DatosDocument8 pagesBase de DatosNATHALIA175No ratings yet

- ADMINISTRACIÓN POR CALIDAD TOTAL (Investigacion Final)Document10 pagesADMINISTRACIÓN POR CALIDAD TOTAL (Investigacion Final)NATHALIA175No ratings yet

- Teoria de La Complajidad ComputacionalDocument1 pageTeoria de La Complajidad ComputacionalNATHALIA175No ratings yet

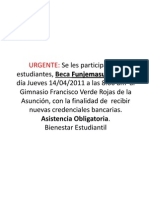

- URGENTEDocument1 pageURGENTENATHALIA175No ratings yet

- Manual Usuario Listo 1Document8 pagesManual Usuario Listo 1randyygamer9No ratings yet

- Sensor de Oxigeno Principios de FuncionamientoDocument6 pagesSensor de Oxigeno Principios de FuncionamientoING. Miguel Angel Sanchez MonzonNo ratings yet

- Portafolio. Una Opción Metodológica Más Auténtica para EvaluaciónDocument10 pagesPortafolio. Una Opción Metodológica Más Auténtica para Evaluacióncoasibague900No ratings yet

- Pantalla Negra Win7 TaringaDocument1 pagePantalla Negra Win7 TaringaoscarwebNo ratings yet

- Universidad Nacional Del Centro Del Perú: Facultad de Ingeniería de MinasDocument77 pagesUniversidad Nacional Del Centro Del Perú: Facultad de Ingeniería de MinasPATOLUCASNo ratings yet

- Subaru Impreza (2003)Document3 pagesSubaru Impreza (2003)EDUARDo GILNo ratings yet

- SNMP Traps PDFDocument10 pagesSNMP Traps PDFGerardo A SanchezNo ratings yet

- Tarea 1-3Document10 pagesTarea 1-3owen chavarriaNo ratings yet

- Regeneracion OvariosDocument4 pagesRegeneracion OvariosAndres Cartes PfisterNo ratings yet

- Guía para La Aplicación Del Método de Costeo Dec2014Document66 pagesGuía para La Aplicación Del Método de Costeo Dec2014Art E LorettoNo ratings yet

- Guía RápidaDocument84 pagesGuía RápidaJazzNo ratings yet

- PSM ApuntesDocument4 pagesPSM ApuntesJ8IgnacioNo ratings yet

- Movicarga 430 WEBDocument152 pagesMovicarga 430 WEBpsd057No ratings yet

- CV Angie JimenezDocument3 pagesCV Angie JimenezKike AtaramaNo ratings yet

- Expo Unidad 4Document30 pagesExpo Unidad 4Jacke AngelesNo ratings yet

- Dinamica Inversa Brazo RoboticoDocument4 pagesDinamica Inversa Brazo RoboticoWilliam WillNo ratings yet

- Unidad 5 Actividad 1Document2 pagesUnidad 5 Actividad 1EsmerolinNo ratings yet

- Taller Practico N°2 Sistema Operativo Linux - Academia Red HatDocument9 pagesTaller Practico N°2 Sistema Operativo Linux - Academia Red HatgverdugobNo ratings yet

- Formacion Ciudadana Marco TeoricoDocument15 pagesFormacion Ciudadana Marco TeoricomaximhuxNo ratings yet

- Bitácora 11 - 10 JL AL 24 JLDocument2 pagesBitácora 11 - 10 JL AL 24 JLsol garciaNo ratings yet

- SYMI - ssomA.et.07.F.07 Petar para Izaje de PersonalDocument2 pagesSYMI - ssomA.et.07.F.07 Petar para Izaje de PersonalLuisfer Sanchez PinedaNo ratings yet

- Programación GenéricaDocument4 pagesProgramación GenéricaWelintong CabascangoNo ratings yet

- Manual S40ANDDocument8 pagesManual S40ANDBladimirUgarteNo ratings yet

- Grado 7Document8 pagesGrado 7sebastian espitiaNo ratings yet

- Instructivo Portal - FacturaxionDocument11 pagesInstructivo Portal - FacturaxionAlfredoNo ratings yet

- Word de SensoresDocument9 pagesWord de SensoresLiz SánchezNo ratings yet