Professional Documents

Culture Documents

Dissertação DSP

Uploaded by

jullianofariaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dissertação DSP

Uploaded by

jullianofariaCopyright:

Available Formats

RAFAEL TAKASAKI CARVALHO

ESTUDO E IMPLEMENTAO DE CONTROLE

DIGITAL PARA O CONVERSOR PONTE

COMPLETA E COMUTAO SUAVE COM

MODULAO POR DESLOCAMENTO DE FASE

(FB-ZVS-PS)

FLORIANPOLIS

2003

UNIVERSIDADE FEDERAL DE SANTA CATARINA

PROGRAMA DE PS-GRADUAO

EM ENGENHARIA ELTRICA

ESTUDO E IMPLEMENTAO DE CONTROLE

DIGITAL PARA O CONVERSOR PONTE

COMPLETA E COMUTAO SUAVE COM

MODULAO POR DESLOCAMENTO DE FASE

(FB-ZVS-PS)

Dissertao submetida

Universidade Federal de Santa Catarina

como parte dos requisitos para a

obteno do grau de Mestre em Engenharia Eltrica.

RAFAEL TAKASAKI CARVALHO

Florianpolis, Novembro de 2003.

ii

ESTUDO E IMPLEMENTAO DE CONTROLE DIGITAL

PARA O CONVERSOR PONTE COMPLETA E

COMUTAO SUAVE COM MODULAO POR

DESLOCAMENTO DE FASE (FB-ZVS-PS)

Rafael Takasaki Carvalho

Esta Dissertao foi julgada adequada para obteno do Ttulo de Mestre em

Engenharia Eltrica, rea de Concentrao em Eletrnica de Potncia, e aprovada

em sua forma final pelo Programa de Ps-Graduao em Engenharia Eltrica da

Universidade Federal de Santa Catarina.

Hari Bruno Mohr, Dr.

Orientador

Denizar Cruz Martins, Dr.

Coordenador do Programa de Ps-Graduao em Engenharia Eltrica

Banca Examinadora:

Hari Bruno Mohr, Dr.

Presidente

Arnaldo Jos Perin, Dr.

Daniel Juan Pagano, Dr.

Enio Valmor Kassick, Dr.

iii

minha esposa, Carise, com quem j dividi e ainda espero dividir

muitos dos melhores momentos de minha vida.

iv

Ao meu filhos, Gabriel e Clara, que so minha

grande fonte de felicidade e realizao.

v

Aos meus pais, Jos Carlos e Ndia, e irmos, Danilo e Cssio,

pela famlia maravilhosa que so.

vi

Agradecimentos

Agradeo, primeiramente, a Deus e ao meu anjo da guarda que sempre

iluminaram meus pensamentos e foram grandes companheiros em todos momentos de

minha vida.

A toda minha famlia e amigos que foram sempre aqueles que estavam mais

prximos para me orientar, alegrar, incentivar e ouvir.

Aos professores Hari B. Mohr e Alexandre F. de Souza pela orientao e empenho

para o aprimoramento deste trabalho e de ou tras atividades que assumi dentro do

instituto.

Ao professor Arnaldo J. Perin que foi, juntamente com o professor Alexandre, um

dos grandes incentivadores para concluso deste trabalho.

Aos professores membros da banca, Arnaldo J. Perin, Daniel J. Pagano e Enio V.

Kassick, pela ateno e contribuio.

Aos meus amigos Carlos, Dirk, Douglas, Eduardo, Kefas, Lus Tomaselli, Ricardo e

Srgio com os quais dividi muito conhecimento e diverso.

A todos os integrantes do INEP que formam uma base importante de apoio no

desenvolvimento de todos os projetos.

A CAPES que disponibilizou os recursos fundamentais para que eu pudesse me

dedicar integralmente durante grande parte do trabalho.

A Universidade Federal de Santa Catarina e ao Departamento de Engenharia

Eltrica pela grande importncia na minha formao profissional e pessoal.

vii

Resumo da Dissertao apresentada UFSC como parte dos requisistos

necessrios para a obteno do grau de Mestre em Engenharia Eltrica.

ESTUDO E IMPLEMENTAO DE CONTROLE DIGITAL

PARA O CONVERSOR PONTE COMPLETA E

COMUTAO SUAVE COM MODULAO POR

DESLOCAMENTO DE FASE (FB-ZVS-PS)

Rafael Takasaki Carvalho

Novembro/ 2003

Orientador: Hari Bruno Mohr, Dr.

rea de concentrao: Eletrnica de Potncia.

Palavras-chave: Fonte de alimentao, controle digital, DSP, telecomunicaes, FB-

ZVS-PS.

Nmero de pginas: 116.

O presente trabalho aborda o desenvolvimento e implementao de um

sistema de controle digital para o estgio de sada de uma fonte de alimentao

para telecomunicaes, conversor FB-ZVS-PS, utilizando o processador digital de

sinais TMS320LF2407 da Texas Intruments. Este trabalho foi motivado, no s

pelas vantagens proporcionadas pelo controle digital, tais como flexibilidade e

reduo de volume, como tambm pela necessidade de desenvolvimento nas

tcnicas de controle para o segmento de retificadores monofsicos. Para a

realizao deste trabalho foi necessrio, alm do estudo do estgio de potncia e

do processador, a elaborao de uma soluo digital original de controle phase-

shift aplicada ao conversor FB-ZVS-PS. Um prottipo utilizando uma placa de

circuito impresso de uma fonte comercial de 600 W foi desenvolvido para

validao desta tcnica. Os resultados obtidos foram extremamente satisfatrios

com destaque para o comportamento dinmico verificado atravs de reduzidas

variaes na tenso de sada sob mudanas de carga.

viii

Abstract of Dissertation presented to UFSC as a partial fulfillment of the

requirements for the degree fo Master in Electrical Engineering.

STUDY AND IMPLEMENTATION OF DIGITAL

CONTROL FOR A SOFT-SWITCHING PHASE-SHIFT

FULL-BRIDGE CONVERTER (FB-ZVS-PS)

Rafael Takasaki Carvalho

November/ 2003

Advisor: Hari Bruno Mohr, Dr.

Area of concentration: Power Electronics.

Keywords: Power supply, digital control, DSP, telecommunications, FB-ZVS-PS.

Nmero de pginas: 116.

The present work accost the development and implementation of a digital

control system to the output stage of telecommunications power supply, FB-ZVS-

PS converter, using the digital signal processor TMS320LF2407 from Texas

Instruments. This project was motivated, not only by the digital control

advantages such as flexibility and volume reduction, but also by the necessity of

control technique development in single fase rectifiers. To accomplish this work,

besides the study of power stage and processor, it was necessary to propose an

original digital solution of phase-shift control applied to FB-ZVS-PS converter. A

prototype using a 600 W commercial supplys power lay-out was developed to

validate this technique. Obtained results were extremely satisfactories standing

out the dynamic behaviour verified by reduced variations on the output voltage

under load changes.

ix

Sumrio

Simbologia................................................................................. XII

Introduo.................................................................................. 1

Captulo 1

Unidades Retificadoras: Um breve histrico...................... 4

1.1. Introduo....................................................................................... 4

1.2. Reviso bibliogrfica....................................................... .............. 5

1.3. Concluso........................................................................................ 8

Captulo 2

Estrutura de Potncia............................................................... 9

2.1. Introduo....................................................................................... 9

2.2. Funcionamento.............................................................................. 10

2.3. Concluso........................................................................................ 16

Captulo 3

Caractersticas do Processador............................................... 17

3.1. Introduo....................................................................................... 17

3.2. Caractersticas bsicas................................................................... 18

3.3. Unidades de memria................................................................... 19

3.4. Ncleo de processamento................................................. ........... 22

3.5. Conjunto de perifricos................................................................. 26

3.5.1. Gerenciadores de eventos................................................ 27

3.5.2. Converso Analgico-Digital (ADC)............... .............. 35

3.5.3. Portas I/ O e pinos de dupla funo............................... 39

3.5.4. Outros registradores configurados................................. 40

3.6. Concluso........................................................................................ 43

x

Captulo 4

Estratgia de Comando............................................................ 44

4.1. Introduo....................................................................................... 44

4.2. Estudo do funcionamento dos Integrados da famlia Phase-

Shift Resonant Controllers.................................................................. 44

4.3. Estratgia para realizar o controle Phase-Shiftutilizando o

DSP TMS320LF2407............................... ............................................... 47

4.4. Resultados experimentais............................................................. 51

4.5. Concluso........................................................................................ 54

Captulo 5

Projeto do Sistema de Controle............................................. 56

5.1. Introduo....................................................................................... 56

5.2. Anlise das caractersticas do sistema digital........................... 58

5.3. Projeto do controlador.................................................................. 62

5.3.1. Modelos da planta e do conversor.................................. 63

5.3.2. Definio dos parmetros do compensador. ................. 67

5.4. Resultados de simulao.............................................................. 72

5.5. Concluso........................................................................................ 77

Captulo 6

Resultados Experimentais...................................................... 78

6.1. Introduo....................................................................................... 78

6.2. Anlise dos resultados..................................................... ............. 78

6.3. Concluso........................................................................................ 87

Concluses Finais..................................................................... 89

Anexo 1

Projeto do Circuito de Potncia e Circuitos Auxiliares e

Diagramas de Circuitos........................................................... 92

xi

A1.1. Projeto do conversor FB-ZVS-PS.............................................. 92

A1.2. Projeto dos circuitos de controle e comando.......................... 103

Anexo 2

Caracterizao do Rudo Psofomtrico................................ 107

A2.1. Psofmetro................................................................................... 108

Referncias Bibliogrficas...................................................... 112

xii

Simbologia

Lista de smbolos empregados no texto

Smbolo Significado

VI Tenso de entrada

VO Tenso de sada

PO Potncia de sada

PIN Potncia de entrada

IO Corrente de sada

Def Razo cclica efetiva

D Perda de razo cclica

Rendimento

frede Freqncia da rede eltrica

Vac Tenso eficaz de entrada

Iac Corrente eficaz de entrada

IINRUSH Corrente de Inrush

CIN Capacitor de filtro da entrada retificada

J Densidade de corrente

B Densidade de fluxo magntico

Ku Fator de utilizao do transformador

Kp Fator de utilizao do primrio

Ae rea da perna central do transformad or

Aw rea da janela do transformad or

Resistividade do cobre

TTrafo

Elevao de temperatura no transformador

O

Permeabilidade do ar

tr Tempo de bloqueio do Mosfet aps comando no gate

tf Tempo de entrada em conduo do Mosfet aps comand o no gate

ID Corrente no diodo

VD Tenso no diodo

IS Corrente no transistor Mosfet

xiii

VS Tenso no transistor Mosfet

MF Margem de fase

Rth Resistncia trmica

S1 S4 Interruptores Mosfet do conversor FB-ZVS-PWM

Di1 Di4 Diod os intrnsecos aos Mosfets S1 S4

Ci1 Ci4 Capacitores em anti-paralelo intrnsecos aos Mosfets S1 S4

G1 G4 Gate dos Mosfets S1 S4

Lr Indutor ressonante

Lp Indutncia do enrolamento primrio

TR Transformador do conversor FB-ZVS-PWM

Ls1 e Ls2 Indutncias do enrolamentos secundrio

Dr1 Dr2 Diod os retificadores d o conversor FB-ZVS-PWM

Cg1 Cg2 Capacitores de grampeamento dos diodos Dr1 Dr2

Rg1 Rg2 Resistores de grampeamento dos diodos Dr 1 Dr2

Dg1 Dg2 Diod os de grampeamento dos diod os Dr1 Dr2

C1 C3 Capacitores do filtro de sada

R1 R3 Resistncias srie equivalente dos capacitores do filtro de sada

L1 e L2 Indutores do filtro de sada

Ro Resistncia de carga

Lo Indutor do filtro de sada tipo LC simples

Co Capacitor do filtro de sada tipo LC simples

Lb Indutor Boost

Db Diod o Boost

Ls Indutor do snubber do conversor PFC Boost

Cs Capacitor do snubber do conversor PFC Boost

Ds1 Ds2 Diod os d o snubber do conversor PFC Boost

Rb Resistor de bloqueio de componente contnua

Cb Capacitor de bloqueio de componente contnua

RINRUSH Resistor de Inrush

n Relao de transformao

Np Nmero de espiras do primrio do transformad or

Ns Nmero de espiras do secundrio do transformador

lg Largura do entreferro

xiv

Ldisp Indutncia de disperso

Dfio Dimetro do fio de cobre

Afio rea do fio de cobre

Fpar alelo Nmero de fios em paralelo

ffita Espessura da fita de cobre

Lfita Largura da fita de cobre

Afita rea da fita de cobre

fs Freqncia de comutao

Fc Freqncia de corte

N5 No

Coeficientes do numerador da funo de transferncia completa do

conversor FB-ZVS-PWM

D7 Do

Coeficientes do denominador da funo de transferncia completa do

conversor FB-ZVS-PWM

Vs Tenso aplicada ao filtro de sada do conversor FB-ZVS-PWM

I/ O Input/ Output (Entrada/ Sada)

T Perod o

Deslocamento entre os pulsos de comando em segundos

Deslocamento percentual entre os pulsos de comando

f Freqncia

fN Freqncia de Nyquist

r (t) Referncia no sistema contnuo

e (t) Sinal de erro no sistema contnuo

u (t) Sinal de sada de controle no sistema contnuo

y (t) Sinal de sada no sistema contnuo

r (kT) Referncia no sistema amostrado

e (kT) Sinal de erro no sistema amostrado

u (kT) Sinal de sada de controle no sistema amostrado

y (kT) Sinal de sada no sistema amostrado

C (s) Funo de transferncia do compensador no sistema contnuo

G (s) Funo de transferncia da planta no sistema contnuo

C (z) Funo de transferncia do compensador discretizada

G (z) Funo de transferncia da planta discretizada

H (z) Funo de transferncia do sensor discretizada

xv

R (z) Referncia no sistema discreto

Y (z) Sinal de sada no sistema discreto

KC Ganho do compensador PI

KDC Ganho esttico do filtro anti-aliasing

Freqncia angular

t tempo

Vsensor Tenso de sada do sensor de tenso/ corrente

VC Sinal de sada do filtro anti-aliasing

Rf1 Rf3 Resistores do do filtro anti-aliasing

Cf1 Capacitor do filtro anti-aliasing

Pp Potncia do sinal a ser medido pelo psofmetro

Pref Potncia de referncia para o psofmetro

Lista de unidades

Smbolo Significado

V Volts

A Ampre

Ohm

W Watt

Hz Hertz

s Segundos

F Faraday

H Henry

dB Decibel

rad Radianos

xvi

Lista de abreviaes

Smbolo Significado

CAPES

Fundao de Coordenao de Aperfeioamento de Pessoal de Nvel

Superior

INEP Instituto de Eletrnica de Potncia

UFSC Universidade Federal de Santa Catarina

FB Full-Bridge (Ponte Completa)

ZVS Zero Voltage Switching (Comutao sob Tenso Nula)

PWM Pulse Width Modulation (Modulao por Largura de Pulso)

ZCS Zero Current Switching (Comutao sob Corrente Nula)

CC Corrente Contnua

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

IGBT Insulated Gate Bipolar Transistor

PFC Power Factor Correction (Correo de Fator de Potncia)

EMI Electromagnetical Interference (Interferncia Eletromagntica)

UPS Uninterruptable Power Supply

DSP Digital Signal Processor (Processador Digital de Sinais)

RAM Random Access Memory

ROM Read-Only Memory

JTAG Joint Test Action Group

A/ D Analgico para Digital

D/ A Digital para Analgico

CI Circuito Integrado

PI Proporcional Integral

PID Proporcional Integral-Derivativo

In tr odu o

1

Introduo

A demanda por inovaes tecnolgicas em Eletrnica de Potncia crescente.

Fabricantes esto continuamente projetando dispositivos capazes de processar energia de

mod o mais eficiente.

Entre as principais aplicaes da Eletrnica de Potncia esto as fontes de

alimentao chaveadas, baseadas em conversores CC-CC, empregadas em equipamentos

de suprimento de energia para diversas finalidades. Dentre elas destaca-se as unidades

retificadoras que com a necessidade de ampliao d o sistema de telefonia, tanto o de

telefonia fixa como mvel, e de alimentao de diversos equipamentos a partir de baterias

tornaram-se foco de diversas pesquisas nos mais variados centros de tecnologia.

Atualmente a necessidade de conformar as fontes de alimentao a uma srie de

rgidas normas de segurana, compatibilidade eletromagntica e, no caso de sistemas de

telefonia, rudo psofomtrico, tem exigido dos projetistas solues inovadoras para

manter seus produtos num mercado competitivo. Alm disso a eterna busca por reduo

de custos um elemento bastante motivador. Para isto, no s o estudo de diferentes

topologias, mas principalmente de diferentes tcnicas de controle so imprescindveis.

A utilizao de tcnicas de controle digital uma tendncia mundial e os seus

estudos vm avanando para aplicao em conversores estticos, principalmente quando

algumas tcnicas de controle analgicas e alguns conversores j so considerados solues

padres para determinado propsito. Pode-se apontar como principais vantagens do

emprego de um controle digital:

Flexibilidade.

Menor suscetibilidade a fatores externos. Ex: temperatura, rudos, mudanas

no lay-out da placa de circuito impresso.

Reduo de volume do equipamento, devido ao nmero de funes que um

processador pode realizar.

Reduo de custos de desenvolvimento e manuteno de um produto.

O conversor FB-ZVS-PS utilizando controle tipo phase-shift ou deslocamento de

fase atravs de integrados dedicados como os da famlia Phase-Shift Resonant

Controllers da Unitrode/ Texas Instruments pode ser considerado uma soluo padro

In tr odu o

2

para unidades retificadoras monofsicas para aplicaes em telecomunicaes. At

mesmo o conversor de entrada, conversor PFC Boost com controle por valores mdios

instantneos, pode ser citado como soluo padro.

Neste sentido este trabalho consiste na apresentao de um mtodo de controle

digital para o conversor de sada de uma fonte de alimentao para telecomunicaes

utilizando o processador digital de sinais DSP TMS320LF2407 da Texas Instruments. O

processador deve ser responsvel, no s, pela execuo da estratgia de controle, mas

tambm por gerar os pulsos de comando d os interruptores. A tcnica de controle

empregada baseada naquela utilizada pelos integrados da famlia Phase-Shift Resonant

Controllers (Unitrode/ Texas Instruments), porm com ajustes por software capazes de

corrigir algumas de suas fragilidades.

O Captulo 1 apresenta uma breve contextualizao desta pesquisa atravs de um

histrico de desenvolvimento de tecnologia para unidades retificadoras.

O Captulo 2 faz uma anlise sobre o funcionamento e as caractersticas do

conversor FB-ZVS-PS empregado. apresentado o modelo do conversor obtido atravs

da anlise do filtro de sada e da sua caracterstica de sada em regime permanente.

No Captulo 3 diversos aspectos do processad or digital so analisados e so

evidenciadas as razes que o fazem apropriado para ser empregado nesta aplicao. Alm

disso, os principais registradores configurados, bem como os valores empregados nestes,

so detalhados, fazendo com que este captulo possa ser uma ferramenta para fcil

reproduo deste projeto ou para novos projetos envolvendo conversores estticos.

Toda a tcnica de controle tipo phase-shift gerada a partir de um processador

digital explanada no Captulo 4. O funcionamento de integrados da famlia Phase-Shift

Resonant Controllers (Unitrode/ Texas Instruments) analisado para servir de base para

elaborao da tcnica. Resultados experimentais em malha aberta so tambm

apresentados.

O Captulo 5 detalha toda a etapa de projeto do lao de controle digital, abordando

todos os aspectos especficos advindos de um sistema de controle digital. Resultados de

simulao do sistema de controle projetado aplicado tanto ao modelo da planta (funo

de transferncia obtida por mtodo de linearizao) quanto ao prprio circuito de

potncia so apresentados.

A validao de toda a tcnica de controle digital proposta realizada no Captulo 6

atravs de uma anlise sobre os resultados experimentais, em r egime permanente e

In tr odu o

3

transitrio, da fonte de alimentao operando com controle de tenso e corrente. So

tambm tomadas medidas de rudo psofomtrico.

Ca pt u lo 1

4

Captulo 1

Unidades Retificadoras: Um breve histrico

1.1. Introduo

Unidades retificadoras (UR) vm sendo largamente utilizadas pela indstria

devido, principalmente, ao aumento da necessidade de carregadores de bateria. Pode-se

citar o mercado de telecomunicaes e o de fontes ininterruptas de energia (UPS) como os

grandes clientes das empresas que desenvolvem estes equipamentos. Embora cada um

destes mercad os possuam suas peculiaridades quanto s caractersticas de desempenhos

das unidades retificadoras, quesitos como correo de fator de potncia, alto rendimento,

excelente regulao de tenso, limitao de corrente, compatibilidade eletromagntica e

monitoramento so pontos comuns na anlise de desempenho de uma UR.

Da mesma forma, como especificaes mais restritivas foram sendo exigidas ao

longo do tempo, o desenvolvimento de novas estruturas vinha sendo realizado ano aps

ano. Com exceo das estruturas trifsicas que ainda no apresentam uma soluo

padro, as URs monofsicas convergiram para uma estrutura de potncia que

basicamente composta de um estgio pr-regulador para correo de fator de potncia

(Conversor Boost com controle por valores mdios instantneos) e um estgio de

isolamento e regulao da tenso de sada (Conversor FB-ZVS-PS).

Inicialmente as URs eram equipamentos pesados e volumosos, caractersticas de

uma retificao a filtro capacitivo com isolamento em baixa freqncia e de uma

regulao da tenso de sada utilizando tiristores ou transistores. Mas com o aumento da

demanda por tecnologia embarcada houve um desenvolvimento muito grande no

processo de fabricao de semicondutores Mosfets e IGBTs de melhor desempenho, o

que possibilitou o aumento da freqncia de operao d os conversores e

consequentemente a reduo de volume e peso dos elementos reativos. Porm, da mesma

forma que houve esta reduo de volume e peso por parte dos elementos reativos, houve

tambm um aumento do volume do dissipador por conseqncia das perdas de

Ca pt u lo 1

5

comutao mais elevadas. Isto causava uma limitao da freqncia de operao do

conversor para que a temperatura de juno do interruptor no atingisse nveis

proibitivos. Para que se pudesse aumentar a freqncia de comutao era necessrio o

desenvolvimento de tcnicas de comutao no-dissipativa dos interruptores e com este

intuito, no incio da dcada de 80, foram introduzidas as tcnicas ressonantes e o

desenvolvimento de novas estruturas que permitiram realizar a comutao tanto sob

corrente nula (ZCS), como sob tenso nula (ZVS).

1.2. Reviso bibliogrfica

Porm, embora as perdas por comutao fossem drasticamente reduzidas, as

perdas por conduo tornaram-se o novo foco das pesquisas visto a circulao elevada de

energia reativa. Para isto foram prop ostas tcnicas e estruturas em que a ressonncia

estivesse presente apenas no instante da comutao. Nesta linha de pesquisa Vieira [1]

realizou uma anlise bem completa de algumas estruturas, inclusive do conversor FB-

ZVS-PS. Foram estudados conversores com modulao em freqncia e PWM. Destacou-

se a modulao PWM pela facilidade no emprego da tcnica e uma indicao de que o

conversor FB-ZVS-PS poderia ser uma alternativa interessante. O trabalho foi

principalmente dedicado anlise do estgio de sada, mas foi identificada a

possibilidade da UR operar com apenas um estgio. Este estudo apresentou uma soluo

competitiva para sistemas trifsicos, pois possui um elevado nmero de componentes

para sistemas monofsicos.

O indicativo sobre a utilizao d o conversor FB-ZVS-PS para o estgio de sada da

UR foi muito importante e deu incio a uma srie de pesquisas de desenvolvimento como

as apresentadas em [2], [3], [4] e [5]. Ainda em sistemas de mais baixa potncia abaixo de

300 W se observa a utilizao do conversor Meia Ponte, mas a tendncia o aumento da

potncia da UR migrando do sistema monofsico para o trifsico sendo que em sistemas

monofsicos, comercialmente, existe uma grande procura por fontes de 10 e 15 A, ou seja,

600 e 900 W.

O conversor FB-ZVS-PS bsico apresentado na Fig. 1.1.

Ca pt u lo 1

6

Lr

Dr1

Dr2

TR1

Lp

Ls1

Ls2

Carga

Co

Lo

Vs

B

A

2

Cg

2 Rg

Dg

2

1

Cg

1

Rg

Dg

1

Vi

C D

C D

1 1

3 3

S

3

S

1

C D

2 2

S

2

C D

4 4

S

4

Fig. 1.1 Estrutura bsica do conversor FB-ZVS-PS.

As reas em destaque tambm foram alvos de pesquisa. O grampeamento da

tenso sobre os diodos retificadores de sada extremamente necessrio devido a

ressonncia entre a indutncia ressonante (Lr) e a capacitncia intrnseca dos diod os. Mas

da forma que empregado na figura acima totalmente dissipativo. Em [6] prop osta a

utilizao de um grampeamento pelo lado do enrolamento primrio, dessa forma pode -se

aproveitar parte da energia da indutncia ressonante e consequentemente aumentar o

rendimento da estrutura. O conversor utilizado neste trabalho faz uso desta tcnica e ser

apresentado no captulo seguinte. Ainda nesta linha de pesquisa, Font e Barbi [7]

apresentam um conversor capaz de aproveitar grande parte da energia que seria perdida

na resistncia do grampead or (Rg) e destin-la ao capacitor de sada. Mas devido ao custo

deste conversor ele se mostra muito til apenas para potncias mais elevadas em sistemas

trifsicos. O filtro de sada tambm um p onto d e bastante estudo, j que no mercado de

telecomunicaes o rudo psofomtrico [8 e 9] uma especificao normatizada.

O conversor pr-regulador tambm um tema importante de desenvolvimento.

Em aplicao para unidades retificadoras monofsicas, o conversor Boost com controle

por valores mdios instantneos adotad o na grande maioria das URs que necessitam de

correo de fator de potncia. Com a necessidade de melhorar cada vez mais o

rendimento das estruturas, esto propostos na literatura muitos mtodos para reduo

das perdas por comutao como tcnicas de comutao sob tenso ou corrente nula ou

circuitos snubber para limitao da derivada de corrente na entrada em conduo ou

bloqueio do interruptor e, tambm, para reduo das perdas por conduo. Pode-se

destacar Souza [10] que analisa uma topologia que integra os interruptores de alta

freqncia no circuito retificador de entrada reduzindo de 3 para 2 o nmero de

semicondutores em conduo simultnea. Mas, por questes de custo, esta tcnica s

Ca pt u lo 1

7

pde ser aproveitada melhor em sistemas de maior potncia. A estrutura bsica

apresentada na Fig. 1.2.

Carga

Vi

Lb

Co

Fig. 1.2 Conversor Boost com reduzidas perdas em conduo.

Um mtodo largamente empregado o snubber no-dissipativo que limita a

derivada do crescimento da corrente sobre o interruptor principal, diminuindo a

influncia da corrente de recuperao reversa do diodo. Este circuito apresentado a

seguir.

Lb

Cs

Ls

Ds Ds

1 2

Vo

Sb

Db

Vi

Fig. 1.3 Snubber no-dissipativo empregado no Conversor Boost.

Atualmente o estudo de tcnicas digitais de controle, em substituio s tcnicas

analgicas, vem sendo objeto de pesquisa. Os avanos nestes estudos foram acelerados

com o advento de novos processadores digitais de sinais, que alm de operarem em alta

velocidade e possurem alto grau de interface, tambm passaram a ser de baixo custo.

Com a flexibilidade que se ganha atravs de implementao de programas, ao invs de

circuitos de controle, reduz-se o tempo e os custos de desenvolvimento de um novo

produto. Alm disso, o fato d o desempenho do processador ser menos afetado por

agentes externos (ex: temperatura) propiciava tambm a reduo nos custos de

manuteno e maior robustez. A maior parte das pesquisas realizadas at o momento se

concentraram em estudos de controle para o conversor PFC ([11] e [12]), alcanando bons

resultados. Pode-se citar como alternativa para URs de baixa potncia o estudo realizado

Ca pt u lo 1

8

por Fung & Tzou [13]. Nele, uma tcnica de controle utilizando um DSP da famlia

TMS320 empregada para operar um conversor PFC Flyback e um conversor CC-CC

bidirecional que responsvel pelo funcionamento da UR nos mod os carga e

flutuao.

Como p ode-se perceber existe uma lacuna a ser preenchida nos estudos de

controle para os conversores que compe uma UR. Poucos estudos de controle digital

foram realizados tendo como foco o estgio CC-CC. O estudo e implementao de

tcnicas de controle digital em estruturas FB-ZVS-PS tm sido pouco explorados na

literatura.

1.3. Concluso

Depois de anos de desenvolvimento e pesquisa, as URs monofsicas, como j dito,

convergiram para uma soluo padro com a possibilidade de utilizao de alguns

circuitos para melhorar o rendimento. As tcnicas de controle desenvolvidas neste

perodo ficaram muito concentradas em solues digitais para o conversor PFC. Desta

forma isto se constituiu em motivao para o desenvolvimento do presente trabalho que

enfoca uma nova proposta de controle atravs de um processador digital de sinais para o

estgio de sada.

Ca pt u lo 2

9

Captulo 2

Estrutura de Potncia

2.1. Introduo

Aplicaes de retificadores de potncia como carregadores de baterias ou

alimentadores de sistemas de telefonia exigem dos conversores estticos empregados,

alm de simplicidade e robustez, tambm eficincia, isolamento e baixos nveis de

interferncia gerados tanto na entrada quanto na sada.

De forma geral os retificadores monofsicos utilizam dois estgios de

processamento. O estgio inicial que corresponde ao filtro de EMI e ao conversor PFC

(conversor Boost) tem o inconveniente de fornecer ao estgio de sada um valor de tenso

elevado e com altos nveis de ondulao.

Esta tenso deve ser alterada para valores entre 42V e 60V com ondulao

reduzida de tal forma que no comprometa os testes de rudo psofomtrico. O isolamento

da carga em relao a rede imprescindvel visto que a carga, muitas vezes, de alto

custo e possui uma importncia estratgica. No caso dos alimentadores de bateria de No-

Breaks o isolamento pode ser feito na sada do inversor, embora apresente um volume

muito maior.

Uma soluo natural para um conversor abaixador isolado seria o conversor

Forward, porm o seu rendimento abaixo do que desejado pelo mercado (acima de

90% para a UR como um tod o). Alm disso, a dificuldade no emprego de tcnicas de

comutao suave, importantes para evitar a propagao de interferncia, e o mau

aproveitamento do transformador no permitem sua aplicao para os atuais fins

comerciais.

O conversor que atende s necessidades do projeto e que ser empregado, como j

mencionado no captulo anterior, o conversor em ponte completa com comutao sob

tenso nula, modulao por largura de pulso (tipo phase-shift) e sada em corrente,

mais conhecido como FB-ZVS-PS, embora este que foi utilizado apresente duas diferenas

Ca pt u lo 2

10

bsicas em relao ao original: o grampeamento da tenso dos diodos retificadores pelo

lado primrio do transformador [6] e o filtro LC duplo na sada.

O conversor FB-ZVS-PS utilizado apresentado na Fig. 2.1.

Lr

Dr

Dr

TR

Lp

Ls

Ls

Carga

Cb

Rb

L

Vs

B

A

2 Cg

2 Rg

Dg

2

1

Cg

1

Rg

Dg

1

S2

S1

S3

S4

1

1

1

2

3

1 L2

1

1

2

2

C

1

R

1

C

2

R

2

C

3

R

3

entrada

Estgio de

CA-CC

Fig. 2.1 Conversor FB-ZVS-PS empregado.

Este conversor apresenta excelente rendimento decorrente das baixssimas perdas

por comutao, reduzidas perdas de conduo devido sua caracterstica de sada em

corrente e do grampeamento de tenso nos diod os retificadores.

Alm disso, como a tcnica de comutao suave proporciona menores perdas, ela

permite a elevao da freqncia de comutao e consequentemente a reduo de volume

dos componentes magnticos e dos capacitores, bem como reduz os nveis de

interferncia eletromagntica.

Para que a tcnica de comutao suave do FB-ZVS-PS seja realizada, necessria a

insero, para cada interruptor, de um capacitor em paralelo e um diodo em anti -paralelo.

Como a grande maioria das estruturas monofsicas utiliza como interruptores elementos

MOSFET, a aplicao da tcnica se torna ainda mais indicada devido ao aproveitamento

dos seus componentes parasitas.

2.2. Funcionamento

Para simplificar a anlise, considera-se a estrutura bsica do conversor FB-ZVS-PS

apresentada na Fig. 1.1, sendo os diod os retificadores componentes ideais e a associao

filtro de sada-carga substituda por uma fonte de corrente.

Desta forma, as principais formas de onda deste conversor so apresentados a

seguir.

Ca pt u lo 2

11

t

0

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

10

t

11

t

12

S

1

S

2

S

3

S

4

I

S2

V

i

V

S2

I '

o

I

S1

V

S1

V

i

I '

o

I

Lr

I '

o

- I '

o

V

ab

V

i

-V

i

V

s

n.V

i

Fig. 2.2 Formas de onda bsicas do conversor FB-ZVS-PS.

Das formas de onda acima apresentadas importante discutir alguns pontos:

Pulsos de comando

O bom desempenho de qualquer conversor esttico depende muito do sinal de

comando dos seus interruptores. O conversor FB-ZVS-PS utiliza pulsos de comando

simtricos. O controle das variveis de sada realizado pelo tipo de modulao

empregada: phase-shift. A modulao por largura de pulso neste caso no se observa

pelo sinal de comando aplicado ao interruptor, mas sim aps a retificao, no secundrio.

A tenso Vs, ou seja, a tenso aplicada ao filtro de sada varia a largura de seu pulso

conforme o deslocamento no tempo dos sinais de comando. Se no houver sobreposio

Ca pt u lo 2

12

entre os sinais significa que o conversor est operando com o mximo de razo cclica que,

na prtica, no pode ser igual a 1 devido ao tempo-morto entre os sinais de comando d o

mesmo brao. A sobreposio total leva a uma tenso nula na sada. O tempo-morto deve

ser calculado no somente para proteo contra curto-circuito de brao, mas tambm para

garantir a entrada em conduo dos interruptores sob tenso nula.

Transformador

Esta tcnica de comand o tambm prop orciona um melhor aproveitamento do

transformador, fazendo-o operar nos quatro quadrantes, simetricamente. Por operar nos

quatro quadrantes a excurso mxima do fluxo reduzida, diminuindo, ento, o tamanho

do ncleo. A tenso VAB (Fig. 2.1) apresenta o sinal imposto ao transformador. Para

reduzir os efeitos de algum desbalanceamento na tenso VAB, que provoca perdas no

transformador, utilizado um circuito RC de bloqueio de componente contnua (bloco 3

Fig. 2.1).

Comutao suave

Para a comutao ser suave, trs fatores devem ser considerad os: a corrente de

carga, a indutncia ressonante e o tempo-morto entre os sinais de comando. a troca de

energia entre a indutncia ressonante e os capacitores em paralelo com os interruptores

que definem a caracterstica da comutao. O brao S1-S3 considerado o brao no-

crtico por sua comutao (bloqueio) ser realizada com corrente de carga referenciada ao

primrio. O brao crtico por sua vez j depende do valor da indutncia ressonante ser

suficientemente grande para no se descarregar to facilmente.

Como se pode ver, este conversor utiliza apenas alguns estgios ressonantes. Isto

uma vantagem em relao aos conversores ressonantes que realizam comutao suave ao

custo de maiores perdas em conduo por circulao de reativos.

Caracterstica de sada

Pela anlise da Fig. 2.2 pode-se perceber que a tenso Vs no somente nula no

intervalo de sobreposio dos pulsos de comando, mas tambm no intervalo de variao

linear da corrente no indutor Lr. Considerando que durante a segunda etapa a corrente no

indutor Lr no varia e sendo D a razo entre o tempo em que a tenso VAB igual a Vi

e o perod o de comutao, atravs da anlise apresentada em [14] definida a

caracterstica esttica do conversor FB-ZVS-PS.

Ca pt u lo 2

13

O

S

2

I O

O

R

f Lr n 4

1

V n

D

V

G

+

(Eq. 2.1)

Onde:

VO = 42 60 V; n = 0,214;

VI = 400 V; fS = 140 kHz;

RO = 4,2 6 ; Lr = 45 H;

Esta expresso pode ser obtida tambm empregando o modelo da chave PWM,

apresentado por Vorprian [15] atravs da anlise do modelo de pequenos sinais do

conversor. Desta forma encontra-se no s o ganho esttico como a funo de

transferncia completa, que nada mais do que a funo de transferncia do filtro de

sada. O ponto de operao foi definido para uma carga de 10 A e razo cclica

aproximadamente igual a 0,8. Em geral, ao projetar a malha de controle utiliza -se apenas a

caracterstica de um filtro LC simples independentemente do filtro adotado. Isto ajuda a

simplificar o projeto, porm pode levar a diferenas significativas ao calcular a malha de

controle digital. A funo de transferncia completa da estrutura apresentada na Fig. 2.1

mostrada a seguir.

0 1

2

2

3

3

4

4

5

5

6

6

7

7

0 1

2

2

3

3

4

4

5

5

O

O

D s D s D s D s D s D s D s D

N s N s N s N s N s N

G

D(s)

(s) V

+ + + + + + +

+ + + + +

(Eq. 2.2)

Sendo:

N5 = (L2.C3

2

.R3

2

.R2.C2.R1.C1 + L2.R3.C3

2

.RO.R2.C2.R1.C1);

N4 = (L2.R2.C2.R1.C1 + L2.C3.R3.R2.C2 + L2.C3.R3.R1.C1 + RO.R3.C3.R2.C2.R1.C1

+ L2.C3.RO.R2.C2 + L2.C3.RO.R1.C1).R3.C3 + (L2.C3.R3.R2.C2.R1.C1 +

L2.C3.RO.R2.C2.R1.C1);

N3 = (RO.R3.C3.R2.C2 + RO.R3.C3.R1.C1 + L2.C3.R3 + RO.R2.C2.R1.C1 + L2.R2.C2

+ L2.R1.C1 + L2.C3.RO).R3.C3 + (L2.R2.C2.R1.C1 + L2.C3.R3.R2.C2 + L2.C3.R3.R1.C1

+ RO.R3.C3.R2.C2.R1.C1 + L2.C3.RO.R2.C2 + L2.C3.RO.R1.C1);

Ca pt u lo 2

14

N2 = RO.R2.C2.R3.C3 + RO.R1.C1.R3.C3 + L2.R3.C3 + RO.R3

2

.C3

2

+ (RO.R3.C3.R2.C2

+ RO.R3.C3.R1.C1 + L2.C3.R3 + RO.R2.C2.R1.C1 + L2.R2.C2 + L2.R1.C1 + L2.C3.RO);

N1 = RO.R3.C3 + RO.R2.C2 + RO.R1.C1 + L2 + RO.R3.C3;

N0 = RO;

D7 = [L1.L2.C3.C2.C1.(RO.R1+R3.R1+R3.R2+RO.R2)].[(R3/ RO+1).L2.C3];

D6 = [L1.L2.C3.C2.C1.(RO.R1 + R3.R1 + R3.R2 + RO.R2)].(L2/ RO + R3.C3) +

(L1.RO.R3.C3.C2.R1.C1 + L1.R2.C2.R1.C1.C3.RO + L1.L2.C1.R2.C2 + L1.RO.R3.C3.C1.R2.C2 +

L1.R2.C2.R1.C1.R3.C3 + L1.L2.C2.R1.C1 + L1.L2.C3.R3.C1 + L1.L2.C3.RO.C2 + L1.L2.C3.RO.C1

+ L1.L2.C3.R3.C2 + L2.C3.R3.R2.C2.R1.C1 + L2.C3.RO.R2.C2.R1.C1) [(R3/ RO+1).L2.C3];

D5 = [L1.L2.C3.C2.C1.(RO.R1 + R3.R1 + R3.R2 + RO.R2)] + (L1.RO.R3.C3.C2.R1.C1 +

L1.R2.C2.R1.C1.C3.RO + L1.L2.C1.R2.C2 + L1.RO.R3.C3.C1.R2.C2 + L1.R2.C2.R1.C1.R3.C3 +

L1.L2.C2.R1.C1 + L1.L2.C3.R3.C1 + L1.L2.C3.RO.C2 + L1.L2.C3.RO.C1 + L1.L2.C3.R3.C2 +

L2.C3.R3.R2.C2.R1.C1 + L2.C3.RO.R2.C2.R1.C1). (L2/ RO + R3.C3) + (L1.L2.C1 +

L1.R1.C1.R3.C3 + L1.L2.C2 + L1.R2.C2.R1.C1 + L1.RO.C1.R2.C2 + L1.R2.C2.C3.RO +

L1.RO.R3.C3.C2 + L1.R2.C2.R3.C3 + L1.R1.C1.C3.RO + L1.RO.R3.C3.C1 + L1.RO.C2.R1.C1 +

L2.R2.C2.R1.C1 + L2.C3.R3.R2.C2 + L2.C3.R3.R1.C1 + RO.R3.C3.R2.C2.R1.C1 +

L2.C3.RO.R2.C2 + L2.C3.RO.R1.C1).[(R3/ RO + 1).L2.C3];

D4 = (L1.RO.R3.C3.C2.R1.C1 + L1.R2.C2.R1.C1.C3.RO + L1.L2.C1.R2.C2 +

L1.RO.R3.C3.C1.R2.C2 + L1.R2.C2.R1.C1.R3.C3 + L1.L2.C2.R1.C1 + L1.L2.C3.R3.C1 +

L1.L2.C3.RO.C2 + L1.L2.C3.RO.C1 + L1.L2.C3.R3.C2 + L2.C3.R3.R2.C2.R1.C1 +

L2.C3.RO.R2.C2.R1.C1) + (L1.L2.C1 + L1.R1.C1.R3.C3 + L1.L2.C2 + L1.R2.C2.R1.C1 +

L1.RO.C1.R2.C2 + L1.R2.C2.C3.RO + L1.RO.R3.C3.C2 + L1.R2.C2.R3.C3 + L1.R1.C1.C3.RO +

L1.RO.R3.C3.C1 + L1.RO.C2.R1.C1 + L2.R2.C2.R1.C1 + L2.C3.R3.R2.C2 + L2.C3.R3.R1.C1 +

RO.R3.C3.R2.C2.R1.C1 + L2.C3.RO.R2.C2 + L2.C3.RO.R1.C1).(L2/ RO + R3.C3) + (L1.C3.RO +

L1.R1.C1 + L1.C2.R2 + L1.RO.C1 + L1.RO.C2 + L1.R3.C3 + RO.R3.C3.R2.C2 + RO.R3.C3.R1.C1

+ L2.C3.R3 + RO.R2.C2.R1.C1 + L2.R2.C2 + L2.R1.C1 + L2.C3.RO).[(R3/ RO + 1).L2.C3];

Ca pt u lo 2

15

D3 = (L1.L2.C1 + L1.R1.C1.R3.C3 + L1.L2.C2 + L1.R2.C2.R1.C1 + L1.RO.C1.R2.C2 +

L1.R2.C2.C3.RO + L1.RO.R3.C3.C2 + L1.R2.C2.R3.C3 + L1.R1.C1.C3.RO + L1.RO.R3.C3.C1 +

L1.RO.C2.R1.C1 + L2.R2.C2.R1.C1 + L2.C3.R3.R2.C2 + L2.C3.R3.R1.C1 +

RO.R3.C3.R2.C2.R1.C1 + L2.C3.RO.R2.C2 + L2.C3.RO.R1.C1) + (L1.C3.RO + L1.R1.C1 +

L1.C2.R2 + L1.RO.C1 + L1.RO.C2 + L1.R3.C3 + RO.R3.C3.R2.C2 + RO.R3.C3.R1.C1 + L2.C3.R3

+ RO.R2.C2.R1.C1 + L2.R2.C2 + L2.R1.C1 + L2.C3.RO).(L2/ RO + R3.C3) + (L1 + RO.R2.C2 +

RO.R1.C1 + L2 + RO.R3.C3).[(R3/ RO + 1).L2.C3];

D2 = (L1.C3.RO + L1.R1.C1 + L1.C2.R2 + L1.RO.C1 + L1.RO.C2 + L1.R3.C3 + RO.R3.C3.R2.C2

+ RO.R3.C3.R1.C1 + L2.C3.R3 + RO.R2.C2.R1.C1 + L2.R2.C2 + L2.R1.C1 + L2.C3.RO) + (L1 +

RO.R2.C2 + RO.R1.C1 + L2 + RO.R3.C3).(L2/ RO + R3.C3) + RO.[(R3/ RO + 1).L2.C3];

D1 = (L1 + RO.R2.C2 + RO.R1.C1 + L2 + RO.R3.C3) + RO.(L2/ RO + R3.C3);

D0 = RO;

No captulo 5 ser apresentado a funo de transferncia em Z empregando os

valores dos componentes adotados no projeto.

A inteno de utilizar o filtro LC duplo p oder fazer uma comparao de

resultados, com relao a caracterstica do sinal de sada, com uma outra fonte de

alimentao implementada no laboratrio com controle analgico. No s utilizou-se o

mesmo filtro de sada, como tambm o mesmo projeto de potncia para todo o conversor

e lay-out da placa de circuito impresso.

Grampeamento dos diodos retificadores

Embora no tenha sido abordada na descrio das formas de onda por se tratarem

de diodos ideais, a anlise do grampeamento dos diodos retificadores (bloco 1 Fig. 2.1)

fundamental para a operao do conversor.

Um diodo real antes de bloquear completamente necessita da circulao de uma

corrente reversa (corrente catodo-anodo) para que a energia armazenada durante o

intervalo de conduo se anule. Neste instante ocorre um fenmeno fsico que simula o

efeito de uma ressonncia devido a interao entre a indutncia de disperso do

transformador e a energia de recuperao do diod o retificador que pode ser modelada

como uma capacitncia. Este efeito leva a sobretenses destrutivas para este componente.

Utilizar diodos com maior tolerncia tenso reversa no deve ser a soluo, pois o

tempo de recuperao do diod o diretamente proporcional a tenso de break-down.

Ca pt u lo 2

16

Desta forma imprescindvel que algum tipo de circuito grampeador seja inserido no

conversor.

Embora bastante utilizado por sua simplicidade e baixo custo, o circuito de

grampeamento RCD tradicional provoca muitas perdas, pois apenas desloca o problema

da sobretenso nos diod os para o resistor de grampeamento. Utilizando o grampeamento

proposto por Redl et al [6] pode-se reaproveitar parte da energia da indutncia de

disperso e, tambm, da indutncia ressonante, devolvendo-a ao capacitor de entrada.

Desta forma, o problema isolado no primrio do transformador e o circuito snubber dos

diodos retificadores (RC) p ode ser redimensionado para uma potncia menor, visto que

agora os diod os de sada enxergam apenas parte da indutncia de disperso e

indutncias de trilha.

2.3. Concluso

O conversor apresentado neste captulo uma soluo tradicional para unidades

retificadoras monofsicas pelo seu elevado rendimento, possibilidade de isolamento em

alta freqncia e por proporcionar baixos nveis de interferncia. Alm disso, a tenso

sobre os interruptores grampeada na tenso de barramento de entrada, o que se traduz

em menores custos. Em termos de projeto foi utilizada a mesma estrutura de potncia e

lay-out aplicada por Alves [3]. O objetivo comparar a performance dos d ois projetos

sob a tica das normas impostas s caractersticas do sinal de sada, visto que [3] utiliza o

controle analgico tradicional e o presente trabalho, uma proposta de controle digital.

Alm disso, atravs da anlise das formas de onda bsicas, pde-se abordar

diversos aspectos importantes do funcionamento do conversor, inclusive a sua funo de

transferncia, principal base para o desenvolvimento deste trabalho que focado no

controle digital desta estrutura.

Ca pt u lo 3

17

Captulo 3

Caractersticas do Processador

3.1. Introduo

Para se fazer o controle do conversor FB-ZVS-PS e ser aplicado a uma unidade

retificadora comercial, o processador digital de sinais deve atender a diversos requisitos.

Com base nas peculiaridades exigidas optou-se por utilizar o Kit DSP TMS320LF2407 da

Texas Instruments [30 e 31].

A famlia TMS320x24x composta por processadores digitais em ponto fixo de 16

bits, projetados para controlar sistemas em tempo real. Para exercer tal funo com o

desempenho necessrio eles operam em diversas freqncias. A freqncia de clock da

CPU do LF2407 igual a 30 MHz, mas a freqncia pode variar de 20 MHz a 40 MHz em

outros processadores. Ainda existe a srie LF28x que opera a 150 MHz. Os DSPs integram

a alta performance de um processad or digital funcionalidade dos perifricos de um

microcontrolad or. Unindo-se a isto um amplo conjunto de instrues, pode-se realizar

tarefas complexas com relativa facilidade.

Estes processad ores, em princpio, foram projetados vislumbrando atender ao

mercado de controle de sistemas de acionamento, em especial sistemas com motores de

baixo custo, visto que a proposta d o controle digital possibilitaria maior flexibilidade e

consequentemente, menor custo com a reduo de componentes. Devido a esta

preocupao, estes processadores renem perifricos com funes apropriadas para o

gerao de pulsos de comando de um inversor (controle e modulao). Como o bom

desempenho de uma fonte chaveada est relacionada ao seu circuito de comando e estes

DSPs so capazes de gerar pulsos de diversas formas diferentes, contemplando at o

tempo-morto, os profissionais de Eletrnica de Potncia passaram a voltar suas atenes

para estes dispositivos.

De forma geral, todos estes processad ores apresentam algumas caractersticas

bsicas que os tornam muito atrativos para o controle de conversores estticos.

Ca pt u lo 3

18

Primeiramente, deve-se ressaltar a separao das estruturas de barramento de memria

programa e dados para dar maior velocidade de processamento. Isto possibilita ler

simultaneamente dados e instrues. Juntamente com o processamento tipo pipeline,

isto permite que algumas instrues possam ser realizadas em apenas um ciclo de

mquina. Em aplicaes que exigem alta freqncia de comutao, como a deste projeto,

no se pode fazer uso de um simples microcontrolador. Microcontroladores so muito

teis para fazer a superviso de uma fonte chaveada, mas no tem a performance

necessria para controlar seus estados [41].

3.2. Caractersticas bsicas

Entre as principais caractersticas d o DSP TMS320LF2407 para implementao

neste projeto pode-se destacar:

Freqncia de clock = 30 MHz.

16 portas de entrada analgicas multiplexadas com tempo de converso de

aproximadamente 500 ns.

2 gerenciadores de eventos independentes.

Portas I/ O digitais.

Memria de programa on-chip (SARAM, DARAM e Flash EPROM).

Comunicao serial.

Registrador de soma e produto de 32 bits.

Instrues apropriadas implementao de compensadores.

Estrutura de processamento tipo pipeline.

O laboratrio dispunha dos kits de desenvolvimento da srie F243 e LF2407.

Outros processadores foram estudados, porm o fato de se operar o conversor na

freqncia desejada, a necessidade de atender a diversos requisistos de interface, a

facilidade em termos de programa que se obteve com a utilizao dos d ois gerenciadores

de eventos e a familiaridade do laboratrio na utilizao de processad ores da famlia

TMS320 tornam o kit DSP TMS320LF2407 bem indicado, no sendo necessrio optar por

verses mais avanadas. Esta necessidade pode aparecer no desenvolvimento de uma UR

comercial contend o o controle dos conversores de entrada e sada e de perifricos como

sinalizaes de monitorao e comunicao serial.

A tabela a seguir apresenta um comparativo das principais caractersticas dos

processadores da famlia TMS320x2x.

Ca pt u lo 3

19

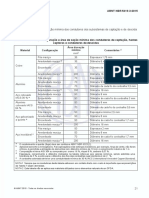

Tab. 3.1 Comparativo das principais caractersticas dos processadores da famlia TMS320x24x.

F241 F243 LF2407 LF2407A F2812

Ciclo de instruo 50ns 50ns 33ns 25ns 6,67ns

Converso A/ D

8 canais

10 bits

8 canais

10 bits

16 canais

10 bits

16 canais

10 bits

16 canais

12 bits

Tempo de converso 1s 1s 500ns 375ns 80ns

Gerenciador de eventos 1 1 2 2 2

Pinos I/ O 26 26 41 41 56

Interface com memria externa Sim Sim Sim Sim Sim

Interface para comunicao serial Sim Sim Sim Sim Sim

Embora seja uma caracterstica importante para aplicao em um produto, pois

possibilita o controle e monitorao remota da UR, bem como facilita o carregamento de

novos cdigos de instruo quando ainda na fase de desenvolvimento, a comunicao

serial no ser explorada neste projeto. A interface com o computador, nesta fase de

desenvolvimento, realizada atravs do kit DSP da Spectrum Digital [42].

3.3. Unidades de memria

O DSP TMS320LF2407 utiliza uma arquitetura Harvard aprimorada com

dispositivos com mltiplos espaos de memria acessveis em 3 barramentos paralelos e

independentes: PAB (Program Address Bus), DRAB (Data-Read Address Bus) e

DWAB (Data-Write Address Bus). Isto permite o acesso simultneo aos espaos de

dados e programa, ou seja a CALU (Central Arithmetic Logic Unit) pode executar em 1

ciclo 3 operaes de memria.

O LF2407 dotado de memria RAM, ROM e FLASH e seu mapa de endereos de

192K words x 16 bits organizado da seguinte forma:

64K words: Memria de programa.

64K words: Memria de dados.

64K words: Memria I/ O.

Ca pt u lo 3

20

Memria de programa: Alm de armazenar o cdigo d o programa, tambm

armazena operadores imediatos e dados de tabela.

Memria de dados: Armazena valores a serem utilizados pelo cdigo d o

programa e configuraes dos registradores relacionados ao conjunto de perifricos. Pode

ser acessada de duas formas, endereamento direto ou indireto. No caso de utilizar o

endereamento direto deve-se declarar qual das 512 pginas (data-pages) se quer

acessar. Cada data-page ocupa um espao de 128 words. O endereamento indireto

acessa a memria de dados atravs de registradores auxiliares que so carregados com o

valor do endereo.

Memria I/O: acessada para definir parmetros de controle da memria Flash e

de comunicao entre a CPU, seus perifricos e a memria externa.

A Fig. 3.1 apresenta os blocos de memria do LF2407 e suas divises e a Fig. 3.2 o

mapa de memria dos registradores dos seus perifricos.

Fig. 3.1 Mapa de memria do DSP TMS320LF2407.

Ca pt u lo 3

21

Fig. 3.2 Mapa de memria dos perifricos na memria de dados.

Memria RAM

DARAM (Dual-access On-chip RAM): Pode ser acessada 2 vezes por ciclo de

mquina. dividida em trs blocos: B0, B1 e B2. Em geral usada como memria de

dados, mas o bloco B0 pode ser usado como memria de programa dependendo do bit

CNF do registrador de status1.

SARAM (Single-access On-chip RAM): Pode ser acessada apenas 1 vez por ciclo

de mquina. Pode ser utilizada tanto como memria de dados como de programa e ainda

configurvel por software como memria interna ou externa.

Memria ROM

mapeada na memria de programa e habilitada na falta de uma interface com a

memria externa (LC240x). A ROM vem programada de fbrica.

Memria FLASH

utilizada quando se deseja um armazenamento permanente do programa, mas

com possibilidade de atualiz-lo. Quanto memria Flash, a famlia LF240x similar aos

dispositivos F24x, mas com avanos como possuir interface JTAG que p ode melhorar a

programao e a emulao.

Ca pt u lo 3

22

Apesar da srie LF2407 possuir interface com memria externa, o que permite

acesso a um espao ainda maior, ele tambm possui memria on-chip. Ela possibilita

melhorar a performance d o processador por no necessitar de estados de espera (wait-

states) imprescindveis para comunicao com a CPU e por consumir menos energia.

3.4. Ncleo de processamento

A Unidade Central de Processamento (CPU) do TMS320LF2407, apresentada na

Fig. 3.3, pode ser dividida nas sees a seguir apresentadas.

Fig. 3.3 Diagrama de blocos da CPU.

Input Scaling Shifter: Permite o deslocamento em 16 bits de dados conectados

ao barramento de dados e das sadas de 32 bits. Como opera como parte da instruo, no

necessita de ciclos de mquina extras para ser executado. Os bits menos significativos d o

dado de sada so preenchidos com n zeros aps o deslocamento de n bits. Os mais

Ca pt u lo 3

23

significativos podem ser preenchidos com zeros ou bits de sinal dependendo do valor do

bit SXM do registrador de status 1.

Multiplicador: Este DSP utiliza um multiplicador em hardware de 16 x 16 bits

capaz de computar um produto de 32 bits, com ou sem sinal, em apenas 1 ciclo de

mquina. Isto uma grande vantagem deste processador em relao a outros ou em

relao a muitos microcontroladores que precisam de rotinas especficas para esta funo,

prejudicando a rapidez de processamento da informao.

Os registradores envolvidos so:

TREG: Registrador de 16 bits preenchidos com um dos operadores.

PREG: Registrador de 32 bits preenchidos com o resultado do produto.

O LF2407 capaz de realizar uma operao de multiplicao simples, como

tambm est totalmente preparado para solucionar equaes recursivas de diversas

ordens. Com instrues dedicadas que aproveitam os recursos de pipeline pode-se

executar diversas multiplicaes e somas de produto j carregando um novo valor no

operad or TREG em apenas 1 ciclo de mquina. Desta forma, este DSP se torna

extremamente atrativo no controle de estruturas das mais variadas reas.

Diretamente relacionados com o PREG possvel, atravs d o campo PM (Product

Shift-Mode) do registrad or de status 1, rotacionar os bits do dad o de sada. Este recurso

permite o uso de diferentes formatos de representao numrica e consequentemente uma

melhor preciso do resultado, visto que no possvel representar qualquer nmero real

de forma digital. A tabela abaixo apresenta de forma sucinta a possibilidade de rotao de

bits dos dados presentes no PREG.

Tab. 3.2 Modos de escala de um produto.

PM Deslocamento Descrio

00 sem deslocamento Dado sem deslocamento.

01 1 bit a esquerda Remove o bit de sinal extra gerado pelo produto

de 2 dados em complemento 2.

10 4 bits a esquerda Remove os 4 bits de sinal extra gerado pelo

produto de um dado de 16 bits por uma

constante de 13 bits

11 6 bits a direita Reescala o produto para evitar overflow.

Ca pt u lo 3

24

No programa utilizado neste projeto se fez uso deste recurso para que se pudesse

representar os ganhos do compensador de forma mais precisa. Utilizando uma

representao numrica tipo Q6 e carregando o campo PM com o valor 3,

automaticamente o resultado da multiplicao reescalado para o formato Q0 (valor

inteiro) [11].

Unidade Lgica e Aritmti ca Central (CALU): Implementa uma srie de funes

lgicas e aritmticas que se dividem em 4 categorias.

Adio em 16 bits.

Subtrao em 16 bits.

Operaes de lgica Booleana.

Testes e deslocamento de bits.

Todas as operaes de adio e subtrao esto vinculadas ao acumulador,

independente do dado a ser somado estar em uma posio da memria de dados, ou seja,

um valor imediato. Desta forma, os campos OVM (Overflow Mode), SXM e SPM dos

registradores de status 0 e 1 influenciam diretamente nesta unidade.

Alm disso, devido a responsabilidade de executar testes de bits, a CALU pode

controlar uma srie de branchs condicionais.

Acumulador: o registrador de sada da CALU. Possui 32 bits que podem ser

divididos em 2 grupos de 16 bits para comunicao com o barramento de dados. Como

mencionado anteriormente, est totalmente vinculado s unidades de deslocamento

(shift) e a alguns modos de operao definidos por campos dos registradores de status.

Unidade Aritmtica de Registradores Auxiliares (ARAU): Realiza operaes

aritmticas nos 8 registradores independentemente da CALU. A Fig. 3.4 ilustra em forma

de diagrama a ARAU.

Ca pt u lo 3

25

Fig. 3.4 Detalhe da ARAU.

A ARAU pode operar da seguinte forma:

Incrementa ou decrementa os registradores auxiliares de 1 unidade ou de um

valor indexado.

Compara o contedo de AR0 com o do registrad or ativo (ARP = 1-7) e coloca o

resultado no bit de teste e controle (TC).

Os registradores auxiliares podem ser utilizados para as funes descritas abaixo:

Permitir o acesso a qualquer posio de memria do barramento de dados

atravs do endereamento indireto utilizando o valor carregado no registrador

como o endereo desejado.

Ser utilizado em rotinas de comparao devido ao uso do bit TC do registrador

de status 1.

Armazenar valores temporrios.

Servir como contador.

Operao em pipeline: Consiste de uma seqncia de operaes que ocorrem

durante a execuo de u ma instruo, que como ocorrem paralelamente, formam canais

Ca pt u lo 3

26

de operaes que podem tornar muito mais rpido o processamento de uma srie de

funes. O DSP TMSx240x possui 4 estgios independentes.

Localizao da instruo.

Decodificao da instruo.

Localizao do operando.

Execuo da instruo.

A Fig. 3.5 mostra a operao dos 4 estgios de pipeline para instrues d o tipo

single-word e single-cycle desprezando a presena de wait-states.

Fig. 3.5 Seqncia de instrues utilizando o recurso de pipeline.

importante o programador ter conhecimento deste recurso para que seu cdigo

seja otimizado para o seu melhor aproveitamento. O uso excessivo de branches no

programa, por exemplo, no uma forma indicada para obter o melhor aproveitamento

deste processador.

3.5. Conjunto de perifricos

Em muitas reas da engenharia, inclusive a de Eletrnica de Potncia,

microcontrolad ores so utilizados para fins de monitorao, alarme e comunicao. Mas

quando se deseja, alm disso, o controle de variveis de uma estrutura, o desempenho do

conjunto de perifricos, os recursos simples de CPU e do conjunto de instrues destes

microcontrolad ores podem no ser suficientes para tal funo.

Como os conversores apresentam freqncia de comutao cada vez mais alta

necessrio um conjunto de perifricos capaz de obter um dado a ser controlado, process-

lo e atuar sobre os mecanismos de acionamento em perod os extremamente pequenos

para atender os requisitos de desempenho tais, como de rejeio de perturbao, ripple

Ca pt u lo 3

27

de sada, entre outros. Desta forma, a utilizao de microcontrolad ores no se mostra

eficaz.

O processador digital de sinais TMS320LF2407 possui um poderoso conjunto de

perifricos e um amplo conjunto de instrues capaz de aproveitar os diversos recursos de

CPU disponveis.

O conjunto de perifricos do LF2407 dividido nas seguintes unidades:

Gerenciadores de eventos (EVA e EVB).

Conversor Analgico-Digital (ADC).

Portas I/ O e pinos de dupla funo.

Interface de comunicao serial (SCI).

Interface serial com perifricos (SPI).

Controlador de rede (CAN).

PLL-based clock.

Temporizador Watchdog (WD).

Os mdulos principais empregados neste projeto so apresentados a seguir.

3.5.1. Gerenciadores de eventos

Juntamente com o mdulo de converso A/ D, os gerenciadores de eventos so,

nas aplicaes em Eletrnica de Potncia, os perifricos mais importantes do processad or.

Esta a unidade responsvel pela gerao dos pulsos de comando do conversor.

Os processadores da famlia Lx240x apresentam um mdulo gerenciador a mais

do que seus antecessores, a famlia F24x. A Fig. 3.6 apresenta o diagrama de blocos do

gerenciador de eventos A.

Este segundo mdulo foi importantssimo no desenvolvimento deste projeto, pois

possibilitou definir os pulsos de comando dos d ois braos do conversor utilizando apenas

unidades de comparao do tipo full-compare que esto diretamente relacionadas com

registradores de tempo-morto, o que dispensa a programao de uma rotina especfica e

no to precisa para esta funo. Caso fosse utilizado o processador da famlia F24x, que

possuem todas as unidades de comparao d o tipo full-compare relacionadas a apenas

um timer, com a inteno de definir os pulsos d e comando inteiramente por software,

seria necessrio implementar uma rotina dedicada a definir um atraso na atualizao do

estado dos pulsos visand o simular o tempo-morto que automaticamente gerado para os

pulsos de comando de um d os braos. Isto praticamente impossibilitaria esta

Ca pt u lo 3

28

implementao inteiramente por software, visto que a no utilizao de perifricos levaria

a um enorme esforo de programao para garantir que chamadas de interrupo no

ocorressem justamente no momento de definio d os pulsos, o que levaria a uma

assimetria.

Fig. 3.6 Diagrama de blocos do EVA.

Exceto quanto aos ndices utilizados, o gerenciador de eventos B exatamente

igual.

Como se pode ver, cada gerenciador de eventos tem vinculado a si temporizadores

(timers) de propsito geral, unidades de comparao e sadas PWM, unidades de

captura e circuitos quadrature-enconder pulse (QEP).

A Tab. 3.3 apresenta a composio dos dois gerenciadores de eventos e destaca em

negrito as unidades utilizadas neste projeto.

Ca pt u lo 3

29

Tab. 3.3 Mdulos e sinais dos gerenciadores de eventos.

EVA EVB

Mdulos do EVM

Mdulo Sinal Mdulo Sinal

Temporizadores

Timer 1

Timer 2

T1PWM/ T1CMP

T2PWM/ T2CMP

Timer 3

Timer 4

T3PWM/ T3CMP

T4PWM/ T4CMP

Unidades de comparao

Compare 1

Compare 2

Compare 3

PWM1/PWM2

PWM3/ PWM4

PWM5/ PWM6

Compare 4

Compare 5

Compare 6

PWM7/PWM8

PWM9/ PWM10

PWM11/ PWM12

Unidades de captura

Capture 1

Capture 2

Capture 3

CAP1

CAP2

CAP3

Capture 4

Capture 5

Capture 6

CAP4

CAP5

CAP6

QEP

QEP 1

QEP 2

QEP1

QEP2

QEP 3

QEP 4

QEP3

QEP4

Entradas externas

Direction

Ext. Clock

TDIRA

TCLKINA

Direction

Ext. Clock

TDIRB

TCLKINB

Temporizadores: H dois temporizadores para cada mdulo gerenciador que

podem ser programad os para operar em freqncias mltiplas do clock de CPU ou de

uma referncia externa. Eles podem ser utilizados como diferentes bases de tempo em

diversas aplicaes, tais como: definio do perodo de amostragem, chamadas de

interrupo, base de tempo das unidades de comparao, entre outras. Os temporizadores

podem tambm ser sincronizados entre si.

Os temporizadores do LF2407 possuem 4 modos de operao:

1) Stop/Hold: Neste modo a contagem interrompida e mantm seu estado

atual at o momento em que o programador desejar.

2) Contagem crescente contnua: o modo de contagem adotado neste projeto

para definio dos pulsos de comand o. a verso digital do sinal dente-de-

serra. O perodo da contagem definido pelo valor carregado no registrador

TxPR acrescentado de u ma unidade e multiplicado pelo perodo de clock da

CPU.

A Fig. 3.7. descreve de forma simplificada a operao deste modo.

Ca pt u lo 3

30

Fig. 3.7 Verso digital do sinal dente-de-serra.

3) Contagem crescente-decrescente contnua: a verso digital da forma de

onda triangular. A contagem crescente at o valor definido por TxPR e depois

passa a ser decrescente at atingir o underflow. Dessa forma o perodo de

contagem duas vezes o valor de TxPR multiplicado pelo perodo de clock

da CPU.

4) Contagem direcional: Este mod o pode realizar a funo de qualquer modo de

contagem contnua de forma crescente ou decrescente de acordo com o

registrador TDIRA/ B. importante por permitir alta flexibilidade ao

processador, mas de pouca utilidade para controle de conversores.

Dos registradores relacionados aos temporizadores, aqueles que foram utilizados

no projeto so detalhados a seguir com os valores empregados.

Timer x Control Register - T1CON / T3CON (7404h / 7504h)

15 14 13 12 11 10 9 8

Free Soft Reservado TMODE1 TMODE0 TPS2 TPS1 TPS0

0 0 1 0 0 0 0

7 6 5 4 3 2 1 0

T2SWT1

T4SWT3

TENEABLE TCLKS1 TCLKS0 TCLD1 TCLD0 TECMPR

SELT1PR

SELT3PR

0 1 0 0 0 0 1 0

Bits 15-14: Bits de controle da emulao. Configurado para interromper a

contagem na suspenso da emulao.

Bits 12-11: Seleo dos modos de contagem. Modo Continous-Up Count.

Ca pt u lo 3

31

Bits 10-8: Fator de multiplicao do clock. CLKTIMER = CLKCPU

Bit 7: Bit de sincronizao dos temporizadores. Cada temporizador usa seu prprio

bit de inicializao.

Bit 6: Bit que habilita o temporizador.

Bits 5-4: Seleo da fonte de clock. Clock interno selecionado.

Bits 3-2: Condio de recarga do registrador de comparao dos temporizadores.

Configurado para recarregar quando o contador atingir 0.

Bit1: Habilita o timer compare.

Bit 0: T2CON/ T4CON usam os prprios perodos ou o perod o de

T1CON/ T3CON.Reservado em T1CON/ T3CON.

Overall GP Timer Control Register A/ B - GPTCONA / GPTCONB (7400h /

7500h)

15 14 13 12 11 10 9 8

Reserv. T2STAT T1STAT Reserv. Reserv. T2TOADC T2TOADC T1TOADC

0 0 0 0 1/0

7 6 5 4 3 2 1 0

T1TOADC TCOMPOE Reserv. Reserv. T2PIN T2PIN T1PIN T1PIN

1/0 1 0 1 0 1

Bit 14: Status do GP Timer2/ 4. Somente leitura.

Bit 13: Status do GP Timer1/ 3. Deve-se ler 1 devido a contagem progressiva destes

temporizadores.

Bits 10-9: Controla o incio da converso com u m evento do Timer2/ 4. Nenhum

evento inicia o ADC.

Bits 8-7: Controla o incio da converso com um evento do Timer1/ 3. Uma

interrupo de comparao do timer 1 inicia o ADC.

Bit 6: Habilita as sadas comparadoras.

Bits 3-2: Polaridade da sada comparadora d o GP Timer2/ 4. Ativo-baixo.

Bits 1-0: Polaridade da sada comparadora d o GP Timer1/ 3. Ativo-baixo.

T1PR / T3PR (7403h / 7503h): Os registradores de perod o so carregados com

210 (decimal) como valor nominal para 140 kHz, mas o registrador T3PR pode

Ca pt u lo 3

32

ser alterado para realizar o deslocamento dos pulsos de comando de um brao

em relao ao outro. Isto ser melhor explicado no captulo seg uinte.

Unidades de comparao: Cada mdulo gerenciador possui trs unidades tipo

full-compare que so responsveis por seis das oitos sadas PWM de cada um deles.

Neste projeto no sero utilizados sadas relacionadas aos registradores TxCMPR. As

unidades do tipo full-compare so um dos mais poderosos recursos dos perifricos

deste DSP. capaz de gerar pulsos de comando com temp o morto definido e sadas

complementares tendo sua razo cclica determinada por comparaes com os

temporizadores.

A Fig. 3.8 apresenta o diagrama de blocos das unidades de comparao.

Fig. 3.8 Diagrama de blocos das unidades comparadoras.

Sendo que:

Para EVA: x = 1, 2, 3; y = 1, 3, 5; z = 1;

Para EVB: x = 4, 5, 6; y = 7, 9, 11; z =2;

Como mencionado anteriormente, o LF2407 por possuir dois gerenciadores de

eventos independentes simplificou bastante a tarefa de gerar os pulsos para o conversor

FB-ZVS-PS. Desta forma pode-se fazer uso de duas unidades full-compare, cada uma

relacionada a um timer diferente (1 e 3). Como as sadas PWM 1-6 esto relacionadas ao

GP timer 1, a nica soluo caso no houvesse as sadas PWM 7-12 seria utilizar a sada

relacionada ao registrador T2CMPR (T2PWM). Logo, abriria-se mo da configurao de

Ca pt u lo 3

33

tempo mort o que a unidade de comparao possibilita e realizaria esta funo

externamente, o que encareceria o produto final, ou por software, o que no seria to

preciso.

Os registradores destas unidades utilizados no projeto so apresentados a seguir.

Compare Control Register A/ B - COMCONA / COMCONB (7411h / 7511h)

15 14 13 12 11 10 9 8

CENABLE CLD1 CLD0 SVENABLE ACTRLD1 ACTRLD0 FCOMPOE Reserv.

1 0 0 0 0 0 1

7 6 5 4 3 2 1 0

Reservado

Bit 15: Habilita a operao de comparao.

Bits 14-13: Condio de recarga do registrador de comparao CMPRx. Recarrega

o registrador na ocorrncia de um underflow em T1CNT/ T3CNT.

Bit 12: Habilita o modo space-vector PWM. Desabilitado.

Bits 11-10: Condio de recarga do ACTR. Recarrega o registrador na ocorrncia de

um underflow em T1CNT/ T3CNT.

Bit 9: Habilita as sadas comparadoras.

Compare Action Control Register A/ B - ACTRA / ACTRB (7413h / 7513h)

15 14 13 12 11 10 9 8

SVRDIR D2 D1 D0

CMP6ACT1

CMP12ACT1

CMP6ACT0

CMP12ACT0

CMP5ACT1

CMP11ACT1

CMP5ACT0

CMP11ACT0

0 0 0 0 0 1 0 1

7 6 5 4 3 2 1 0

CMP4ACT1

CMP10ACT1

CMP4ACT0

CMP10ACT0

CMP3ACT1

CMP9ACT1

CMP3ACT0

CMP9ACT0

CMP2ACT1

CMP8ACT1

CMP2ACT0

CMP8ACT0

CMP1ACT1

CMP7ACT1

CMP1ACT0

CMP7ACT0

1 0 0 1 0 1 1 0

Bit 15: Utilizado somente para o space-vector PWM.

Bits 14-13: Utilizado somente para o space-vector PWM.

Bits 11-0 : Polaridade dos pinos de sadas comparadoras CMP12 CMP1. Os pinos

PWM1 e PWM2 devem ser complementares assim como PWM7 e PWM8.

01 Ativo-baixo.

Ca pt u lo 3

34

10 Ativo-alto.

Dead-Band Timer Control Registers A/ B - DBTCONA / DBTCONB (7415h

/ 7515h)

15 14 13 12 11 10 9 8

Reservado DBT3 DBT2 DBT1 DBT0

0 1 0 1

7 6 5 4 3 2 1 0

EDBT3 EDBT2 EDBT1 DBTPS2 DBTPS1 DBTPS0 Reservado

0 0 1 0 0 1

Bits 11-8: Definem o valor do perodo dos 3 dead-band timers de 4 bits de cada

gerenciador. Combinado com o prescaler definem o tempo morto.

Bits 7-5: Habilitam os 3 dead-band timers relacionadas aos blocos de

comparao CMP6-1 e CMP12-CMP7. Desta forma esto habilitados para os pinos

PWM1, PWM2, PWM7 e PWM8.

Bits 4-2: Dead-band timer prescaler.

Com esta configurao, o temp o-morto ficou programado para 500 ns nas sadas

PWM e levando-se em conta que existe um circuito drive para comando dos

interruptores, o tempo-morto diretamente aplicado a estes foi de aproximadamente 380

ns.

CMPR1 / CMPR4 (7417h / 7517h): so configurados com o valor nominal igual

a 104 que corresponde a razo cclica de aproximadamente 50%, mas CMPR4

pode ser alterado para que o controle phase-shift seja realizado, em

decorrncia da alterao de T3PR.

Registradores de interrupes: so configurados de acord o com a interrupo que

se deseja na ocorrncia de um evento do gerenciador. So divididos em registradores d o

tipo mscara (mask) e do tipo flag.

Os registradores do tipo mscara definem quais interrupes esto habilitadas.

Neste projeto foi necessrio habilitar a interrupo de comparao do GP timer 1. Ela

controla o incio da converso A/ D e a chamada da interrupo que tratar os dados

adquiridos.

Ca pt u lo 3

35

Os registradores d o tipo flag atuam como sinalizao da ocorrncia de um

evento, cuja interrupo havia sido habilitada. Os bits que so setados devem ser

levados a zero novamente para que a interrupo possa ser identificada pelo processad or.

Os registradores de interrupes so os seguintes:

Tab. 3.4 Registradores de interrupo.

Registradores Flag Registradores Mask Mdulo EV

EVAIFRA (742Fh) EVAIMRA (742Ch) EVA

EVAIFRB (7430h) EVAIMRB (742Dh) EVA

EVAIFRC (7431h) EVAIMRC (742Eh) EVA

EVBIFRA (752Fh) EVBIMRA (752Ch) EVB

EVBIFRB (7530h) EVBIMRB (752Dh) EVB

EVBIFRC (7531h) EVBIMRC (752Eh) EVB

3.5.2. Converso Analgico-Digital (ADC)

Outro mdulo importante do conjunto de perifricos, o ADC do LF2407 apresenta

as seguintes caractersticas:

Tempo de converso 500 ns.

Converso A/ D em 10 bits.

16 canais de entrada multiplexados.

Capacidade de programar uma seqncia de canais a serem adquiridos e

modos de converso.

Uma das vantagens da famlia Lx240x em relao a F24x, alm do tempo de

converso reduzido, a possibilidade de realizar uma seqncia de converses. Ele possui

2 seqenciadores independentes de 8 converses (SEQ 1 e SEQ 2) que podem ser

cascatead os para 16 converses. Como o F24X s permitia 2 converses em seqncia,

ento, reduziu-se muito o tempo necessrio para reconfigurar o ADC para uma nova

aquisio. Quando h rudos de comutao nos sinais a serem controlados interessante

implementar um filtro digital atravs da mdia de 2 a 4 aquisies para minimizar este

efeito no controle, j que, diferentemente do sistema analgico, no sistema digital a

varivel amostrada se mantm como uma referncia constante para todas as aes de

controle durante todo o perod o de amostragem. Caso seja necessrio controlar mais de

uma varivel, o nmero de converses pode passar de 8. Neste projeto so monitorados

os sinais de tenso e corrente de sada fazendo uma mdia de 2 aquisies para cada

varivel, que nos testes de bancada apresentou melhores resultados.

Ca pt u lo 3

36

A Fig. 3.9 apresenta o diagrama de tempos em relao ao perodo de amostragem e

a Fig. 3.10 o diagrama de blocos do mdulo ADC.

KT

t(K) t(K+1)

T = 7,14 us

a

233ns 400ns

2 6 5

1us

1 - "Backup" de informaes (pilha).

2 - Configurao de registradores para aquisio de sinais.

3 - 2 Aquisies da imagem da tenso de sada.

1 3 4

1us 2,2us 1us

4 - 2 Aquisies da imagem da corrente de sada.

5 - Algoritmo: lgica de modulao e reconfigurao

6 - Restaurao de informaes.

de registradores.

Fig. 3.9 Diagrama de tempos.