Professional Documents

Culture Documents

Lecture Notes - Introduction To Accumulators and Fpgas: Accumulator Basics

Uploaded by

Waqar AzeemOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture Notes - Introduction To Accumulators and Fpgas: Accumulator Basics

Uploaded by

Waqar AzeemCopyright:

Available Formats

ECE238 laboratory lecture notes

University of New Mexico

Lecture notes - Introduction to Accumulators and FPGAs

Accumulator Basics

An accumulator is build with an adder whose sum can be loaded into a register as shown in figure 1. Accumulators are a basic building block of most large digital logic or DSP project. As an analogy, you can think of an up accumulator (the type we are using in this project) as a file cabinet. It starts out empty. If you add two, it now holds the value of two. If you add three more it now holds five.

Figure 1; Block diagram for an Accumulator

Adders

A basic half adder logic diagram is shown in figure 2, including its equations and truth table. It is called a half adder because it does not include a carry in within its inputs. Note that the circuit is made of simple XOR and AND gates. A basic full adder logic diagram is shown in figure 3, including its truth table. A full adder does include the carry in as an input. It is build by two half adders and an additional OR gate. Note that figure 3 is showing a full 1 bit adder. In order to build full X-bit adders (where X represents any integer) we must put together several 1-bit full adders. There are several ways to do so. In this lab we will follow a ripple carry adder approach. A full 4-bit adder schema is shown in figure 4.

Figure 2; half adder logic diagram, equations and truth table

Figure 3; Logic diagram of a 1-bit wide full adder and truth table.

ECE238 laboratory lecture notes

University of New Mexico

Other techniques will have different configurations corresponding to different trade off between delays, size of the circuit and complexity. For more references please go to chapter 5 of your text book.

Figure 4; Block diagram of a 4-bit wide ripple carry adder.

Field Programmable Gate Array (FPGA) Basics

The workhorse of the programmable logic industry is the FPGA. Similarly to CPLDs, a FPGA also replace discrete logic but it is build differently. A FPGA architecture resembles to a two dimensional array of logic cells interconnected by a huge amount of routing resources and connected to the exterior world with I/O blocks. Therefore an FPGA has three basic parts as shown in figure 5.

Figure 5. Building blocks of a FPGA The basic building block of a FPGA is a slice which is made of two identical Configurable Logic Block (CLB), as shown in figure 3. A CLB is made of Look-up Table (LUT) units; some carry and

ECE238 laboratory lecture notes

University of New Mexico

control logic and storage elements. The amount, characteristics and interconnection of these elements varies between FPGA families. A detailed CLB schematic is shown in figure 7. LUT: Form the basic logic generation. It is typically of four inputs, being able to build any four-input logic function. In a CLB as the one shown in figure 6, a LUT can also be configured and used as a 16-bit x 1 RAM or a 16-bit shift register. Carry and control: It is composed of fast arithmetic logic, multiplier and multiplexer logic. Storage elements: Usually latch or flip-flops with set and reset capabilities, true or inverted inputs and synchronous or asynchronous control.

Figure 6; A simplified slice view. Taken from Virtex 2 datasheet.

Figure 7; A detailed CLB view. Taken from Virtex 2 datasheet.

ECE238 laboratory lecture notes

University of New Mexico

For you to have an idea of how much logic we can fit in the chips on the boards we will use for, note that they have around 400 CLBs. It is also common to measure a FPGA size by useable or system gates. If you remember the work you did earlier in the semester with the 7400 chip you will recall that the chip contained four two input NAND gates. Given the belief that any logic can be developed using enough two input NAND gates, this measure has been assigned the useable/system gates term. The Digilent boards (containing the Xilinx SpartanXL FPGA chips) we will be using for the rest of the semester are described as having 10 thousand useable gates. Each day, the number of useable gates increases, as does the speed. What is the standard today will be considered antique in the next year or so. The one underlying theme that will continue to survive is the coding scheme. You can use VHDL to program ANY CPLD and ANY FPGA. That is why hardware description languages are critical to know. Finally, a significant difference with CPLDs is that a FPGA is a SRAM device, it requires external devices for configuration after each power cycle. In general, FPGAs offer more logic flexibility and more sophisticated system features than CPLDs: clock management, on-chip RAM, DSP functions (multipliers), etc. Why can say that FPGA are generally used for larger and more complex designs. Be aware tough, that they consume a lot more power than a CPLD.

Using the Digilent XL Prototyping Board

The board we are going to be using for the rest of the semester is the Digilent Spartan XL board (figure 5). It is an excellent prototyping board. If you are interested in doing additional projects after this course, there are a large variety of very reasonably priced boards that are virtually limitless in the span and quantity of projects you can do.

Figure 5. Digilent XL board.

ECE238 laboratory lecture notes

University of New Mexico

The Xilinx FPGA on the board is a 3.3volt, 10,000 useable gate device. Once again you can see where we are using lower voltages (3.3 vs. the 5 from the discrete logic) to conserve power and heat. The trend is towards lower and lower voltages in programmable logic. The device has a speed grade of 5. This is the 5C that you see at the bottom of the chip. A large number of these chips are cut at a single time from a large wafer. The chips closer to the center of the wafer are of better quality and their speed is higher (thus a higher number and price). The lower the number the further from the center of the wafer and thus the slower the device (and cheaper the cost). For our chip (XC2S30), they come in speed grades 4 and 5. We will also begin using more and more files within each project. This is necessary anytime you wish to increase your level of complexity and increase the quantity of things you wish to accomplish.

Floorplanner

Just as Chipviewer gave you a chance to look within the CPLD, Floorplanner gives you a chance to look within the FPGA. Many times, design engineers will never need this capability. In this course you will never need it. What we have taken for granted is that your designs are small and you do not care about the speed at which your circuit operates. You just click on the buttons, step back and let the software take over for you. It is a comfortable place. Unfortunately, in the real world you always want your design to fit on a smaller device and you always want to make it go just a little faster than the competitor. This is where Floorplanner becomes your friend. Floorplanner provides you with a graphical ability to modify how your design is placed and routed on the chip. It is a graphical placement tool that gives you control over placing a design into a target FPGA using a drag and drop paradigm with the mouse pointer.

This lower picture shows you the CLB in row 7, column 8 and how it was wired on a previous project. These two pictures give you an idea of where we are headed.

This document was created with Win2PDF available at http://www.daneprairie.com. The unregistered version of Win2PDF is for evaluation or non-commercial use only.

You might also like

- FPGA Fundamentals - National InstrumentsDocument5 pagesFPGA Fundamentals - National InstrumentsAndrea QuadriNo ratings yet

- FPGA Arquitectura BasicaDocument7 pagesFPGA Arquitectura BasicaJesus LeyvaNo ratings yet

- Fpga IntroDocument10 pagesFpga IntroJpradha KamalNo ratings yet

- Fpgas - Under The Hood: Figure 1. The Different Parts of An FpgaDocument14 pagesFpgas - Under The Hood: Figure 1. The Different Parts of An FpgaTolga KökalpNo ratings yet

- Design of Arithmetic Calculator Using FpgaDocument58 pagesDesign of Arithmetic Calculator Using FpgavikramNo ratings yet

- What Is An FPGADocument6 pagesWhat Is An FPGAVishnu VikashNo ratings yet

- Fpga QuestionsDocument10 pagesFpga QuestionsSuji DarsanNo ratings yet

- Design of Embedded ProcessorsDocument80 pagesDesign of Embedded ProcessorsSayan Kumar KhanNo ratings yet

- FPGA Design Flow: Page 1 of 5Document6 pagesFPGA Design Flow: Page 1 of 5PRAVEEN034No ratings yet

- Digital Filters in Programmable Logic DevicesDocument13 pagesDigital Filters in Programmable Logic DevicesJoerg MenkeNo ratings yet

- Lecture 2 - Introduction To FPGAs PDFDocument14 pagesLecture 2 - Introduction To FPGAs PDFVenkateswara ReddyNo ratings yet

- Master Thesis FpgaDocument5 pagesMaster Thesis Fpgatashahollowaylittlerock100% (1)

- Atul K Srivastava: 10.3 Field Programmable Gate ArraysDocument4 pagesAtul K Srivastava: 10.3 Field Programmable Gate ArraysTushar GuptaNo ratings yet

- Make-SoCs-flexible-with-embedded-FPGADocument6 pagesMake-SoCs-flexible-with-embedded-FPGAALiftsNo ratings yet

- Fpga Implimentation of LCD Display1Document77 pagesFpga Implimentation of LCD Display1praveen_banthiNo ratings yet

- Designing Digital Circuits Using Field Programmable Gate Arrays (Fpgas) (Part 1)Document7 pagesDesigning Digital Circuits Using Field Programmable Gate Arrays (Fpgas) (Part 1)조현민No ratings yet

- FPGA: Field Programmable Gate ArrayDocument5 pagesFPGA: Field Programmable Gate ArrayGolnaz KorkianNo ratings yet

- Asic Prototyping TPDocument11 pagesAsic Prototyping TPsarin.gaganNo ratings yet

- Fpga Viva QuestionDocument4 pagesFpga Viva QuestionManila MathurNo ratings yet

- FpgaDocument6 pagesFpgaÁryâñ SinghNo ratings yet

- Fpga Interview QuestionsDocument9 pagesFpga Interview QuestionsV SharmaNo ratings yet

- Lab 1: FPGA Physical LayoutDocument9 pagesLab 1: FPGA Physical LayoutNeeraj GuptaNo ratings yet

- VHDL TutorialDocument127 pagesVHDL TutorialDeepanker KumeriaNo ratings yet

- A Framework For The Design of High Speed Fir Filters On FpgasDocument4 pagesA Framework For The Design of High Speed Fir Filters On Fpgasamit1411narkhedeNo ratings yet

- C 789Document18 pagesC 789Ác QủyNo ratings yet

- University of Technology Michatronics Branch: Wasan Shakir Mahmood 4 - Stage Supervisor: Layla HattimDocument13 pagesUniversity of Technology Michatronics Branch: Wasan Shakir Mahmood 4 - Stage Supervisor: Layla HattimWasan ShakirNo ratings yet

- CPLDDocument7 pagesCPLDnanbanjayNo ratings yet

- ASK Me For Digital Programmable Circuits: Fixed Function Undefined FunctionDocument4 pagesASK Me For Digital Programmable Circuits: Fixed Function Undefined FunctionHudaa EltNo ratings yet

- ASK Me For Digital Programmable Circuits: Fixed Function Undefined FunctionDocument4 pagesASK Me For Digital Programmable Circuits: Fixed Function Undefined FunctionHudaa EltNo ratings yet

- Eecs150: Lab 2, Mapping Circuit Elements To Fpgas: 1 Time TableDocument15 pagesEecs150: Lab 2, Mapping Circuit Elements To Fpgas: 1 Time Tabledarkdrone66No ratings yet

- FPDSP LatestDocument14 pagesFPDSP LatestHassaan AhmadNo ratings yet

- InterconnectsDocument6 pagesInterconnectsachuu1987No ratings yet

- FPGA Vs ASICDocument9 pagesFPGA Vs ASICKamleshNo ratings yet

- Fpga Interview QuestionDocument35 pagesFpga Interview QuestionRAGUL RAJ S100% (1)

- All About FPGAsDocument11 pagesAll About FPGAsSujeet SharmaNo ratings yet

- Fpgas and DSP: Design Alternatives For DSP SolutionsDocument8 pagesFpgas and DSP: Design Alternatives For DSP Solutionsnguyendinh126No ratings yet

- 3 Fpga Programming PDFDocument49 pages3 Fpga Programming PDFdimen100No ratings yet

- FPGA and FPGAC (High Level Synthesise Tools)Document15 pagesFPGA and FPGAC (High Level Synthesise Tools)RUBEN DARIO TAMAYO BALLIVIANNo ratings yet

- Partitioning An ASICDocument6 pagesPartitioning An ASICSwtz ZraonicsNo ratings yet

- FPGA Genreal PaperDocument7 pagesFPGA Genreal PaperParth SomkuwarNo ratings yet

- Synplicity Efficient DSPDocument8 pagesSynplicity Efficient DSPravindarsinghNo ratings yet

- FPGA Based Multi Core ProcessorDocument16 pagesFPGA Based Multi Core ProcessorvinayNo ratings yet

- Asic Prototyping TPDocument11 pagesAsic Prototyping TPLexx TwoNo ratings yet

- Embedded Systems Design with Platform FPGAs: Principles and PracticesFrom EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesRating: 5 out of 5 stars5/5 (1)

- Vlsi Manual 2013-2014Document36 pagesVlsi Manual 2013-2014hr_suresh_kNo ratings yet

- Jan 08 FeatureDocument5 pagesJan 08 FeatureCarlos Andrés Moreno PetroNo ratings yet

- Single Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGADocument4 pagesSingle Chip Solution: Implementation of Soft Core Microcontroller Logics in FPGAInternational Organization of Scientific Research (IOSR)No ratings yet

- A Brief Study of Reconfigurable Computation Systems With A Focus of FPGA Based DevicesDocument11 pagesA Brief Study of Reconfigurable Computation Systems With A Focus of FPGA Based DevicesMeToolNo ratings yet

- Fpga Interview QuestionsDocument11 pagesFpga Interview QuestionsNavathej BangariNo ratings yet

- GameCube Architecture: Architecture of Consoles: A Practical Analysis, #10From EverandGameCube Architecture: Architecture of Consoles: A Practical Analysis, #10No ratings yet

- Design Performance AnDocument17 pagesDesign Performance Anankaiah_yadavNo ratings yet

- Thesis VHDL PDFDocument6 pagesThesis VHDL PDFmarybrownarlington100% (2)

- Fpga DaDocument137 pagesFpga DaSiddaling B AlandNo ratings yet

- Fpga: Digital Designs: Team Name:Digital DreamersDocument8 pagesFpga: Digital Designs: Team Name:Digital DreamersRishabhNo ratings yet

- Programmable Logic ArraysDocument5 pagesProgrammable Logic ArraysSitotaw NigussieNo ratings yet

- VLSIDocument11 pagesVLSIKumaril BorkuteNo ratings yet

- Thesis FpgaDocument7 pagesThesis FpgaWriteMyPaperCanada100% (2)

- 8 Bit ALU by XilinxDocument16 pages8 Bit ALU by XilinxDIPTANU MAJUMDERNo ratings yet

- High-Level Design Process Using Intel OpenCL FPGADocument4 pagesHigh-Level Design Process Using Intel OpenCL FPGAjackNo ratings yet

- ANOVA ExamplesDocument23 pagesANOVA ExamplesWaqar AzeemNo ratings yet

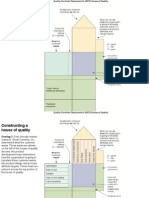

- Constructing A House of QualityDocument5 pagesConstructing A House of QualityWaqar AzeemNo ratings yet

- Statistics For Business and EconomicsDocument116 pagesStatistics For Business and EconomicsWaqar AzeemNo ratings yet

- Clarkson Lumber Case Study - SolDocument5 pagesClarkson Lumber Case Study - SolWaqar Azeem73% (11)

- Section 22 20 23 - Natural Gas PipingDocument11 pagesSection 22 20 23 - Natural Gas PipingWaqar AzeemNo ratings yet

- Location and Site Map: Bin Qasim Coal Power Project - 420 M.WDocument2 pagesLocation and Site Map: Bin Qasim Coal Power Project - 420 M.WWaqar AzeemNo ratings yet

- EFSAnnouncement1 2013Document4 pagesEFSAnnouncement1 2013Hassan ShahNo ratings yet

- NTDC LetterDocument2 pagesNTDC LetterWaqar AzeemNo ratings yet

- MBA MC Evening RevisedDocument1 pageMBA MC Evening RevisedWaqar AzeemNo ratings yet

- Karachi Electric Supply Company Limited: Payslip For The Month of September, 2012Document1 pageKarachi Electric Supply Company Limited: Payslip For The Month of September, 2012Waqar AzeemNo ratings yet

- Aquafina-Marketing PlanDocument4 pagesAquafina-Marketing PlanWaqar Azeem67% (3)

- LM741Document7 pagesLM741vila mathanki100% (1)

- 6968-C.v. (Salman U) - Experience FirstDocument3 pages6968-C.v. (Salman U) - Experience FirstWaqar AzeemNo ratings yet

- Project ObjectiveDocument2 pagesProject ObjectiveWaqar AzeemNo ratings yet

- 2012-03-05 PDFDocument6 pages2012-03-05 PDFWaqar AzeemNo ratings yet

- Dometic RM4185 6405 PDFDocument20 pagesDometic RM4185 6405 PDFcarlosrei2No ratings yet

- Founder-CEO Succession at Wily TechnologyDocument12 pagesFounder-CEO Succession at Wily TechnologyMayank Saini100% (1)

- Pump Installation Report: 30 Damascus Road, Suite 115 Bedford, Nova Scotia B4A 0C1Document1 pagePump Installation Report: 30 Damascus Road, Suite 115 Bedford, Nova Scotia B4A 0C1Yosif BabekerNo ratings yet

- Hw3 UpdatedDocument2 pagesHw3 UpdatedGeoffrey Liu0% (1)

- APL APOLLO - Chaukhat - Catalogue A4 English - 04 03 2022 - Low ResDocument48 pagesAPL APOLLO - Chaukhat - Catalogue A4 English - 04 03 2022 - Low ResarrsshaNo ratings yet

- SIRTOS A Simple Real Time Operating SystemDocument6 pagesSIRTOS A Simple Real Time Operating Systemmiguel angelNo ratings yet

- Serie: Guía RápidaDocument12 pagesSerie: Guía RápidalumapueNo ratings yet

- A140Document104 pagesA140hungchagia1No ratings yet

- Osisense ManualDocument2 pagesOsisense ManualLki SelfNo ratings yet

- TDSC Tpus420 enDocument23 pagesTDSC Tpus420 encatalind_cdNo ratings yet

- Anern Integrated Solar Garden Light-201604Document1 pageAnern Integrated Solar Garden Light-201604Godofredo VillenaNo ratings yet

- Maintenance and Repair Instructions TM 124/11: Spring-Applied Sliding Caliper Brake FSG110 With Hub CenteringDocument11 pagesMaintenance and Repair Instructions TM 124/11: Spring-Applied Sliding Caliper Brake FSG110 With Hub CenteringNik100% (1)

- Chapter 1: INTRODUCTION: 1.1 BackgroundDocument5 pagesChapter 1: INTRODUCTION: 1.1 BackgroundAhsan azizNo ratings yet

- Supervisory Setpoint Control (SSC) : I/A Series SystemDocument46 pagesSupervisory Setpoint Control (SSC) : I/A Series SystemMiguel Angel GiménezNo ratings yet

- CFD Analysis of Free Cooling of Modular Data CentersDocument4 pagesCFD Analysis of Free Cooling of Modular Data CentersEmad AbdelsamadNo ratings yet

- Careers 2Document1 pageCareers 2CityPressNo ratings yet

- Contoh Ringkasan Mengajar Bahasa Inggeris Tahun 2 Dan 3Document2 pagesContoh Ringkasan Mengajar Bahasa Inggeris Tahun 2 Dan 3Izla MajidNo ratings yet

- Manual Safety Relays 3SK2 en-USDocument352 pagesManual Safety Relays 3SK2 en-USKarina Ospina100% (3)

- Tool PresettingDocument22 pagesTool PresettingAtulMaurya100% (1)

- UbnfilelDocument3 pagesUbnfilelJorge LorenzoNo ratings yet

- Session 2A JonkerDocument15 pagesSession 2A JonkerD_D_ANo ratings yet

- Performance Analysis of Cooperative Communication For Wireless NetworksDocument164 pagesPerformance Analysis of Cooperative Communication For Wireless NetworksIhtesham JadoonNo ratings yet

- Feedwater Heating SystemsDocument82 pagesFeedwater Heating SystemsJitendra ChaudhariNo ratings yet

- Power GenerationDocument34 pagesPower GenerationTaufiq AkbarNo ratings yet

- QAch 02Document13 pagesQAch 02Rami Alnajjar100% (1)

- Mach Oil BrochureDocument44 pagesMach Oil BrochureIntan DavidNo ratings yet

- BLTouch Setup ManualDocument7 pagesBLTouch Setup ManualBobbyNo ratings yet

- 009-1137-00 HST-SMRTD Savant Smart Host Tech SpecDocument6 pages009-1137-00 HST-SMRTD Savant Smart Host Tech Specferna2420No ratings yet

- Giving Constructive Feedback Training Course OutlineDocument3 pagesGiving Constructive Feedback Training Course OutlineJeeNo ratings yet

- Information Security Chapter 2 Planning For SecurityDocument20 pagesInformation Security Chapter 2 Planning For SecurityBramara Sri100% (1)