Professional Documents

Culture Documents

Clock Skew

Uploaded by

naveenchand_a6Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Clock Skew

Uploaded by

naveenchand_a6Copyright:

Available Formats

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

Clock Skew Definitions: The difference between arrival times of the clock at different devices is called clock skew.

Example of clock skew:

2004 Centre for Development of Advanced Computing

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

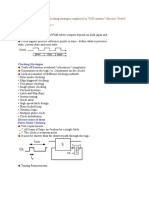

Clock Skew

Buffering the clock: In a large system, the single clock signal may not have adequate fanout to drive all of the devices, so it may be necessary to provide one or two copies of the clock signal.

The buffering method of figure (a) produces excessive clock skew, since CLOCK1 and CLOCK2 are delayed through an extra buffer compared to CLOCK. A recommended method is shown in figure (b). All of the clock signals go through identical buffers, and thus have roughly equal delays.

2004 Centre for Development of Advanced Computing

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

Minimizing the clock skew

Add Delay in Data Path:

The amount of the inserted delay (number of BUFD or INVD macros) in the data path should be large enough so that the delay becomes sufficiently greater than the clock skew.

2004 Centre for Development of Advanced Computing

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

Minimizing the clock skew

Clock Reversing:

In this method, the clock signal arrives at the clock port of the destination register sooner than the source register. Therefore, the destination register will clock in the source register (current) value before the source register receives its clock edge. The clock reversing method will not be effective in circular structures such as Johnson counters because it is not possible to define the source register explicitly.

2004 Centre for Development of Advanced Computing

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

Minimizing the clock skew

Clock Reversing in circular structure:

In this example, the clock skew problem exists between flip-flops U1 and U3.

2004 Centre for Development of Advanced Computing

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

Minimizing the clock skew

Alternate Phase Clocking: The following are the most common methods of alternate phase clocking: 1. Clocking on alternate edges 2. Clocking with two phases 1. Clocking on alternate edges:

In this method, the sequentially adjacent registers are clocked on opposite edges of the clock. This method provides a short path-clock skew margin of about one-half clock cycle.

2004 Centre for Development of Advanced Computing

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

Minimizing the clock skew

Signal propagation for previous circuit:

2004 Centre for Development of Advanced Computing

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

Minimizing the clock skew

Clocking with two phases:

In this method, the sequentially adjacent registers are alternatively clocked on two different phases of the same clock. In this case, between each two adjacent registers, there is a safety margin approximately equal to the phase difference of the two phases.

2004 Centre for Development of Advanced Computing

DIPLOMA IN VLSI DESIGN

VHDL CONSTRUCTS - I

THANK YOU

2004 Centre for Development of Advanced Computing

You might also like

- Programmable Logic Design Grzegorz Budzy Ń L Ecture 10: Fpga Clocking SchemesDocument70 pagesProgrammable Logic Design Grzegorz Budzy Ń L Ecture 10: Fpga Clocking SchemesTechy GuysNo ratings yet

- Radio Control for Model Ships, Boats and AircraftFrom EverandRadio Control for Model Ships, Boats and AircraftRating: 5 out of 5 stars5/5 (1)

- Clock GenerationDocument45 pagesClock GenerationMoin PashaNo ratings yet

- Clock Gating Techniques for Power Optimization in VLSI CircuitsDocument4 pagesClock Gating Techniques for Power Optimization in VLSI Circuitsvaibhav.1991No ratings yet

- Designing robust clock trees for complex SoCsDocument9 pagesDesigning robust clock trees for complex SoCsStudent100% (1)

- 16th Edition IEE Wiring Regulations: Design and Verification of Electrical InstallationsFrom Everand16th Edition IEE Wiring Regulations: Design and Verification of Electrical InstallationsRating: 4 out of 5 stars4/5 (1)

- A Semi Digital Dual Delay-Locked LoopDocument10 pagesA Semi Digital Dual Delay-Locked Loopmkdo67No ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- Clock GateDocument19 pagesClock Gateamma4manuNo ratings yet

- Clock Tree Synthesis: Presentation by Sudhir Kumar MadhiDocument69 pagesClock Tree Synthesis: Presentation by Sudhir Kumar Madhisudhir100% (2)

- Clock Tree Synthesis Presentation by Sudhir Kumar MadhiDocument69 pagesClock Tree Synthesis Presentation by Sudhir Kumar MadhiAgnathavasiNo ratings yet

- Design of Clock Distribution Networks-Case StudyDocument3 pagesDesign of Clock Distribution Networks-Case StudyPino Watson PisoloNo ratings yet

- Chapter2 Clocks Resets-02Document11 pagesChapter2 Clocks Resets-02Harish GurumurthyNo ratings yet

- Asic Design GuidlinesDocument45 pagesAsic Design Guidlinesliron192000No ratings yet

- Clock Skew AnDocument13 pagesClock Skew AnNimmalapudi SureshNo ratings yet

- Clock Skew Filtering and Minimizing Short Path ProblemsDocument8 pagesClock Skew Filtering and Minimizing Short Path ProblemshardeepNo ratings yet

- Unit Iv Reliability and Clock SynchronizationDocument15 pagesUnit Iv Reliability and Clock Synchronizationp.arunagiriNo ratings yet

- Layout Synthesis Benchmarks Focus on Speed, Skew, TestabilityDocument10 pagesLayout Synthesis Benchmarks Focus on Speed, Skew, TestabilityVishakh BharadwajNo ratings yet

- Clocking Strategies and Pipelining Techniques in VLSI CircuitsDocument17 pagesClocking Strategies and Pipelining Techniques in VLSI Circuitshrishikeshch123No ratings yet

- PAGE9Document6 pagesPAGE9praveenmorampudi42No ratings yet

- Lec16 SynchDocument9 pagesLec16 SynchSumanth VarmaNo ratings yet

- Most Asked INterview Questions For Physical DesignDocument2 pagesMost Asked INterview Questions For Physical DesignAvas RoyNo ratings yet

- Clock Distribution Using VHDLDocument66 pagesClock Distribution Using VHDLBridget GrahamNo ratings yet

- Static Timing Analysis Static Timing AnalysisDocument49 pagesStatic Timing Analysis Static Timing AnalysisRajesh DurisalaNo ratings yet

- How To Solve Setup & Hold Violations in The Design: PowerDocument20 pagesHow To Solve Setup & Hold Violations in The Design: PowerSujit Kumar100% (1)

- Dual Loop DLLDocument11 pagesDual Loop DLLKiran KNo ratings yet

- Pre-STA Timing AnalysisDocument39 pagesPre-STA Timing AnalysisSwathi KambleNo ratings yet

- Timing Issues in Digital Circuits: Synchronous Design: Presented by Presented ToDocument10 pagesTiming Issues in Digital Circuits: Synchronous Design: Presented by Presented ToShruti ShreyaNo ratings yet

- Week 5 Lecture MaterialDocument88 pagesWeek 5 Lecture MaterialAnupam DasNo ratings yet

- FPGA Design TechniquesDocument32 pagesFPGA Design TechniquesRavindra SainiNo ratings yet

- Clock Distribution: Shmuel WimerDocument79 pagesClock Distribution: Shmuel WimerKaushal PanchalNo ratings yet

- Performance Comparison of Various Clock Gating Techniques: S.V.Lakshmi, P.S.Vishnu Priya, Mrs.S.PremaDocument6 pagesPerformance Comparison of Various Clock Gating Techniques: S.V.Lakshmi, P.S.Vishnu Priya, Mrs.S.PremayanaNo ratings yet

- VLSI Interview Questions and AnswersDocument5 pagesVLSI Interview Questions and AnswersMahesh S GourNo ratings yet

- Electronic Clocks: UEET101 SPRING 2009Document27 pagesElectronic Clocks: UEET101 SPRING 2009Azhar HussainNo ratings yet

- VLSI file formats and clock tree exceptionsDocument23 pagesVLSI file formats and clock tree exceptionsvikasNo ratings yet

- Cts 1Document16 pagesCts 1Rohit D PandrangiNo ratings yet

- Lecture11 Ee689 Clocking Arch PllsDocument100 pagesLecture11 Ee689 Clocking Arch PllsdogudoguNo ratings yet

- Presentation 1Document33 pagesPresentation 1Satyajit GantayatNo ratings yet

- Instruction PipeliningDocument8 pagesInstruction PipeliningUsman UlHaqNo ratings yet

- Comb - and - Seq CircuitDocument13 pagesComb - and - Seq CircuitTibebeselasie MehariNo ratings yet

- Clock Gating MrthodologyDocument71 pagesClock Gating Mrthodologystarwar127No ratings yet

- Systolic Array Architectures in CmosDocument13 pagesSystolic Array Architectures in Cmosozoemena29No ratings yet

- Power Dissipation in Clock DistributionDocument66 pagesPower Dissipation in Clock DistributionBilal uddinNo ratings yet

- Synchronous Digital Design Methodology and GuidelinesDocument39 pagesSynchronous Digital Design Methodology and GuidelinesVenkataAkhilNo ratings yet

- Unit 2 - Session-6 To 10Document40 pagesUnit 2 - Session-6 To 10Sanjeevkumar M SnjNo ratings yet

- Unit 5Document60 pagesUnit 5sparsh kaudinyaNo ratings yet

- Lecture06 LatchesDocument30 pagesLecture06 LatchesBala KrishnaNo ratings yet

- 7 Clocking StrategiesDocument8 pages7 Clocking StrategiesErnest TiongNo ratings yet

- Constraining Designs 1.0Document17 pagesConstraining Designs 1.0bvrboseNo ratings yet

- Pipeline Hazards. PresentationDocument20 pagesPipeline Hazards. PresentationReaderRRGHT100% (1)

- Clock Gating Circuits PDFDocument4 pagesClock Gating Circuits PDFTej Pal Singh100% (1)

- Clock Gating: K.Harshavardhan 19021D6802 M-Tech (Vlsi & Es)Document14 pagesClock Gating: K.Harshavardhan 19021D6802 M-Tech (Vlsi & Es)Bunny harshaNo ratings yet

- Clocking and Latches: Notes For EEC180B Spring 1999 University of California DavisDocument18 pagesClocking and Latches: Notes For EEC180B Spring 1999 University of California Davisrvs_093No ratings yet

- What Are The Different Clocking Strategies Employed in VLSI System ? Discuss H-Tree' Clock Distribution in High Density CMOS Circuits ? AnsDocument6 pagesWhat Are The Different Clocking Strategies Employed in VLSI System ? Discuss H-Tree' Clock Distribution in High Density CMOS Circuits ? AnsTozammel Hossain TusharNo ratings yet

- LPVDDocument12 pagesLPVDPardha SaradhiNo ratings yet

- Clock Balance Ieee Seminar04Document49 pagesClock Balance Ieee Seminar04Anvesh Reddy100% (1)

- Clock Tree SynthesisDocument27 pagesClock Tree Synthesispdnoob100% (3)

- Sri Ramakrishna and Swami Vivekananda Revisited in the Light of TantraDocument10 pagesSri Ramakrishna and Swami Vivekananda Revisited in the Light of Tantranaveenchand_a6No ratings yet

- 2024 BroucherDocument4 pages2024 Brouchernaveenchand_a6No ratings yet

- CGHSDocument94 pagesCGHSnaveenchand_a6No ratings yet

- CG Employees 2024Document23 pagesCG Employees 2024naveenchand_a6No ratings yet

- Australia-China Relations: The Great Unravelling: Issue No. 366Document16 pagesAustralia-China Relations: The Great Unravelling: Issue No. 366naveenchand_a6No ratings yet

- TA English PDFDocument6 pagesTA English PDFchinna rajaNo ratings yet

- CGHS Hospital ListDocument125 pagesCGHS Hospital ListG RADHAKRISHNA67% (3)

- Shri Guru Charitra in EnglishDocument64 pagesShri Guru Charitra in EnglishHappy Mountains0% (2)

- RBI Alert PDFDocument1 pageRBI Alert PDFnaveenchand_a6No ratings yet

- State MachinesDocument27 pagesState Machinesnaveenchand_a6No ratings yet

- Voter Card Form No. 7Document4 pagesVoter Card Form No. 7Ajay SinghNo ratings yet

- CCS (Leave) RulesDocument53 pagesCCS (Leave) Rulespoojasikka196380% (5)

- Ca Rules After 7 PCDocument2 pagesCa Rules After 7 PCnaveenchand_a6No ratings yet

- Babylonian and Indian Astronomy - EarlyConnectionsDocument37 pagesBabylonian and Indian Astronomy - EarlyConnectionsjoker8832No ratings yet

- Lesson-4 Communication and Computer Network (123 KB)Document24 pagesLesson-4 Communication and Computer Network (123 KB)naveenchand_a6No ratings yet

- Computers For Bank Exams - Guide4BankExamsDocument82 pagesComputers For Bank Exams - Guide4BankExamsShiv Ram Krishna100% (4)

- Syn 2Document13 pagesSyn 2naveenchand_a6No ratings yet

- VHDL CookbookDocument111 pagesVHDL Cookbookcoolboyz81990No ratings yet

- ASIC Integrated Circuit Background GuideDocument27 pagesASIC Integrated Circuit Background Guidenaveenchand_a6No ratings yet

- Vlsi Design Power DissipationDocument19 pagesVlsi Design Power Dissipationnaveenchand_a6No ratings yet

- Latch Up in Cmos LogicDocument4 pagesLatch Up in Cmos LogicDeep SaxenaNo ratings yet

- A05 ShellscriptDocument16 pagesA05 Shellscriptnaveenchand_a6No ratings yet

- Ram A Krishna PrayerDocument3 pagesRam A Krishna Prayernaveenchand_a6No ratings yet

- General Knoweledge RefresherDocument59 pagesGeneral Knoweledge Refreshernaveenchand_a6No ratings yet

- Pass Transistor LogicDocument36 pagesPass Transistor LogicMuneza NaeemNo ratings yet

- Jis-Astm SpecDocument1 pageJis-Astm SpecRizki AhmadNo ratings yet

- Hero Honda - Erp SystemDocument10 pagesHero Honda - Erp SystemKaran Gaur0% (1)

- Orifice Catalogue EnglishDocument11 pagesOrifice Catalogue Englishrahman ariwibowoNo ratings yet

- Fuse Box Diagram Peugeot 406, 1995 - 2004Document8 pagesFuse Box Diagram Peugeot 406, 1995 - 2004MARGOTTONo ratings yet

- FNPT Screening: 3. Power Tabelle FNPT / Flap SettingDocument3 pagesFNPT Screening: 3. Power Tabelle FNPT / Flap SettingMarian GrigoreNo ratings yet

- SAP MM Interview QuestionsDocument19 pagesSAP MM Interview Questionsok tourNo ratings yet

- Tamilnadu Food Ind PDFDocument150 pagesTamilnadu Food Ind PDFdeva nesan100% (4)

- Chapter 4Document38 pagesChapter 4WANNo ratings yet

- Holiday Homework for Class 10 Cbse 2015Document7 pagesHoliday Homework for Class 10 Cbse 2015afmtcbjca100% (1)

- Importance of Low Point DrainDocument10 pagesImportance of Low Point Drainpesuk100% (1)

- Micro Controller Archtecture ProgrammingDocument94 pagesMicro Controller Archtecture ProgrammingyayavaramNo ratings yet

- E WasteDocument8 pagesE Wasteanon-815109100% (1)

- Tugas Resume Strategi Pembelajaran Di SDDocument8 pagesTugas Resume Strategi Pembelajaran Di SDDega YogaswaraNo ratings yet

- 5.8 GHZ 2-Line Corded/Cordless Answering System Ep5962: User Manual (Part 2)Document53 pages5.8 GHZ 2-Line Corded/Cordless Answering System Ep5962: User Manual (Part 2)Payphone.comNo ratings yet

- Maintenance Manual DrivelinesDocument73 pagesMaintenance Manual Drivelineshebert perezNo ratings yet

- Calculation of Crack Width As Per Is:456-2000Document4 pagesCalculation of Crack Width As Per Is:456-2000Gautam DuttaNo ratings yet

- Verification of AMBA Bus Model Using SystemVerilogDocument5 pagesVerification of AMBA Bus Model Using SystemVerilogdoomachaleyNo ratings yet

- Automated Sign Language InterpreterDocument5 pagesAutomated Sign Language Interpretersruthi 98No ratings yet

- 2019 Task 3.2 Bsbcus402 Bsbres411 Bsbwrt401 Assessment v3Document10 pages2019 Task 3.2 Bsbcus402 Bsbres411 Bsbwrt401 Assessment v3Laudious ChepkoechNo ratings yet

- Assessment Details:: Scenario (Relevant To Ass.1, Ass.2 & Ass.3)Document2 pagesAssessment Details:: Scenario (Relevant To Ass.1, Ass.2 & Ass.3)Farzana AlamNo ratings yet

- Online Travel Order Processing System Release 4 User's ManualDocument32 pagesOnline Travel Order Processing System Release 4 User's ManualRichard AdrianNo ratings yet

- FPE Micro-ProjectDocument21 pagesFPE Micro-ProjectHarsh PatilNo ratings yet

- Name - Date - GroupDocument2 pagesName - Date - GroupAlberto Recio GimenezNo ratings yet

- User Guide: Echolife Hg520C Home GatewayDocument25 pagesUser Guide: Echolife Hg520C Home Gatewayluis PavilaNo ratings yet

- Caja de Piso Ref 25249-FBADocument4 pagesCaja de Piso Ref 25249-FBACristianDuarteSandovalNo ratings yet

- ICON Tutorial 2019 Time Series ForecastingDocument129 pagesICON Tutorial 2019 Time Series Forecastingkiran gollaNo ratings yet

- Alineamiento y Perfil 1aupvDocument3 pagesAlineamiento y Perfil 1aupvingeniero civilNo ratings yet

- Virtualization: Hardware Virtualization Is Subdivided Into The Following TypesDocument5 pagesVirtualization: Hardware Virtualization Is Subdivided Into The Following TypesShweta YadavNo ratings yet

- MTTI successful bidders prequalification 2020/2021Document10 pagesMTTI successful bidders prequalification 2020/2021Lawrence KyaloNo ratings yet

- Project ReportDocument56 pagesProject ReportAstha MishraNo ratings yet